无结场效应晶体管基础知识解析

无结场效应晶体管(Junctionless Field Effect Transistor, JLT)是场效应晶体管的一种,由源极、漏极及中间的金属-氧化物-半导体(Metal-Oxide-Semiconductor, MOS)电容结构构成。与传统的金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor, MOSFET)器件不同,源极、沟道及漏极的杂质掺杂类型相同,无PN结,属于多数载流子导电器件。JLT利用栅极偏置电压改变垂直于导电沟道的电场强度,使沟道内的多数载流子累计或者耗尽,从而调制沟道电导控制沟道电流。无结场效应晶体管(JLT)已被提出作为传统MOSFET的替代品,以减轻传统晶体管由于特征尺寸微缩所面临的技术挑战。

背景技术

当代所有集成电路芯片均由PN结或肖特基势垒结构成,如结型场效应晶体管(Junction Field Effect Transistor, JFET)垂直沟道方向有一个PN结,金属-氧化物-半导体场效应晶体管(MOSFET)平行沟道方向有两个背靠背的PN结,高电子迁移率晶体管(High Electron Mobility Transistor, HEMT)垂直沟道方向有一个栅电极肖特基势垒结,等等。

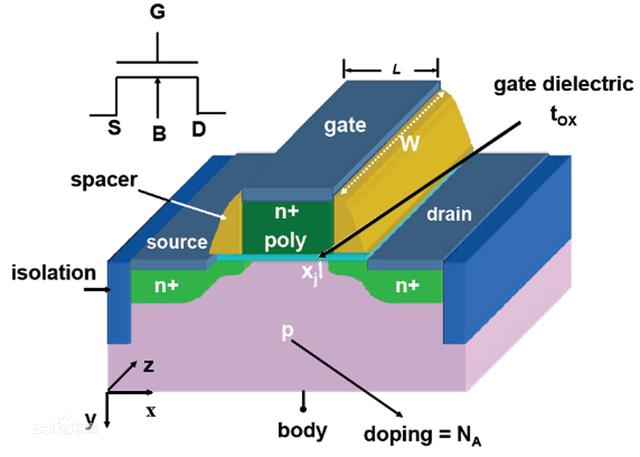

传统的MOSFET由源极、漏极及中间的金属-氧化物-半导体(MOS)电容结构构成,结构如图1所示。MOSFET沟道的掺杂类型与源、漏极相反(如沟道为N型,源、漏极则为P型),因此源极、沟道和漏极之间构成两个背靠背的PN结。栅极施以足够大的电压,产生垂直于沟道的电场,并在半导体沟道表面感应出少子电荷,半导体表面将由耗尽进入反型,形成反型沟道,即可允许电流通过,此时沟道导电类型与源、漏极相同。施加于栅极不同的电压值,流过沟道的电流亦会受其控制而改变。

由于结型场效应晶体管器件栅氧化层与半导体沟道界面的不完整性,载流子受到散射,迁移率下降,可靠性降低。MOS器件遵循“摩尔定律”,特征尺寸持续按比例微缩,基于PN结的MOS场效应晶体管器件弊端越来越明显:源漏距离不断缩短,产生短沟道效应,栅控能力变差,器件性能及可靠性严重退化;为防止源漏穿通,采用超陡掺杂浓度梯度,严重限制器件工艺热预算。除此之外,由于掺杂原子的统计分布及一定温度下掺杂原子易于扩散的自然属性,纳米尺度范围内制作超陡PN结变得异常困难,晶体管阈值电压下降,漏电严重。而金属-半导体场效应晶体管(Metal-Semiconductor Field Effect Transistor, MESFET)或高电子迁移率晶体管(HEMT)热稳定性较差,肖特基结栅电极漏电流较大,逻辑摆幅较小,抗噪声能力较弱等。这些问题的存在严重制约着未来半导体制造业进一步、深层次的发展。

为克服结型场效应晶体管器件在纳米尺度范围所面临的难以逾越的障碍,肖德元等人在2005年首次提出了一种全新结构及其制造方法-圆柱体全包围栅无结场效应晶体管(Gate-All-Around-Cylindrical Junctionless Field Effect Transistor, GAAC JLT),它属于多数载流子导电器件。从此半导体界兴起了一股研究无结场效应晶体管的热潮,每年的国际电子器件会议(IEDM)及IEEE杂志均有该器件的研究报道。

基本概念

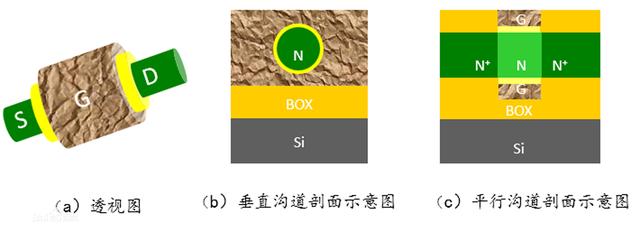

无结场效应晶体管(JLT)是场效应晶体管的一种,由源极、漏极及中间的金属-氧化物-半导体(MOS)电容构成。与传统的MOSFET器件不同,源极、沟道及漏极杂质掺杂类型相同,无PN结,属多数载流子导电器件。图2描绘了这种简化了的圆柱体全包围栅无结场效应晶体管器件结构透视图和沿沟道及垂直沟道方向器件剖面示意图。 SOI衬底上晶体管有一个圆柱体单晶硅沟道,其掺杂类型与源、漏区相同,如图2(c)所示。采用低压化学气相沉积或原子层沉积技术生长栅氧化层, 将整个沟道包裹起来, 接着在其上沉积金属及多晶硅栅, 导电沟道与金属栅之间被栅氧化层隔离。沟道内的多数载流子在圆柱体沟道内而非表面由源极到达漏极。通过栅极偏置电压使器件沟道内的多数载流子累计或者耗尽,可以调制沟道电导进而控制沟道电流。当栅极偏置电压大到将圆柱体沟道靠近漏极某一截面处的载流子完全耗尽时,沟道电阻变成准无限大,器件处于关闭状态。相较于传统的MOS场效应晶体管,无结场效应晶体管无PN结,制备工艺简单,性能优越,增强了器件的可靠性特别是抗热载流子注入效应及噪声容限。

器件模型

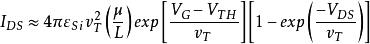

2009年,肖德元等人首次发表了圆柱体全包围栅无结场效应晶体管(Gate-All-Around-Cylindrical Junctionless Field Effect Transistor, GAAC JLT)基于沟道全耗尽的紧凑型模型并推导出该器件的电流-电压方程表达式。基于二维泊松方程、欧姆定律及部分常数近似,求得器件漏电流ID的表达式为:

其中

分别为源极与漏极的耗尽层深度。式中 μp为电子迁移率,εοx为绝缘体电容率,εs为半导体电容率,R为圆柱体沟道的半径,L为圆柱体沟道长度,d为栅绝缘层厚度,Na为衬底沟道掺杂浓度,Vg、Vd分别为栅极与漏极的偏置电压。

从器件电压-电流方程式可看出,与工作于反型模式的传统MOS晶体管器件不同,无结场效应晶体管器件的驱动电流与栅氧化层厚度不成反比例关系,减轻了MOSFET器件特征尺寸持续按比例缩小对栅氧化层厚度无休止的减薄要求。

2012年,韩国科学院和三星电子公司的科学家在肖德元等人的无结圆柱体沟道场效应晶体管耗尽层近似器件模型基础上,提出了完整的长沟道圆柱体全包围栅无结场效应晶体管器件模型。该模型基于Pao-Sah积分并在器件全耗尽、部分耗尽及积累等所有工作区间,采用电势抛物线近似,从而获得电荷模型。

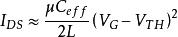

器件亚阈值区,漏极电流表达式可简化为:

其中Vth为阈值电压,Vt为热电压 KT/q,μ为载流子有效迁移率, L为器件沟道长度。

器件线性区(Vg-Vt>Vds ),漏极表达式可简化为

其中Ceff为半耗尽区有效栅电容。

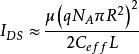

器件饱和区(Vg-Vth<Vds ),漏极电流表达式可简化为

小Vds平带情形,漏极电流表达式可进一步简化为

这时器件相当于一个电阻( I=V/R),与栅氧化层的厚度无关。

器件饱和区平带情形,漏极电流表达式可进一步简化为

它与栅氧化层厚度d相关。

器件特点

无结场效应晶体管是电压控制器件,不需较大信号功率。栅极偏置电压可360度方向将圆柱体沟道内的载流子由表及里耗尽,大大增强了栅极对圆柱体沟道的控制能力,有效降低了器件的阈值电压。由于避开了不完整的栅氧化层与半导体沟道界面,沟道内的多数载流子在圆柱体沟道体内而非表面由源极到达漏极,载流子受到界面散射影响有限,提高了载流子迁移率,噪声较低。相比于传统的反型沟道MOS场效应晶体管,无结场效应晶体管属于多数载流子导电器件,沿沟道方向靠近漏极的电场强度较低,提高了器件性能及可靠性。该器件制作工艺简单,与传统平面CMOS技术兼容较好。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

光伏发电相关文章:光伏发电原理