浅谈usb2.0的ESD静电防护设计

生活中,静电放电的危害无处不在,很多电子产品都设计有对外的连接端子,最为常见的要属USB了,现在很多电子产品都有这个接口,并且由于USB接口可热插拔,会容易产生不可避免的人为因素,导致静电损坏器件,如死机、烧板等。使用USB接口的用户迫切需求加大ESD防护设计的器件。

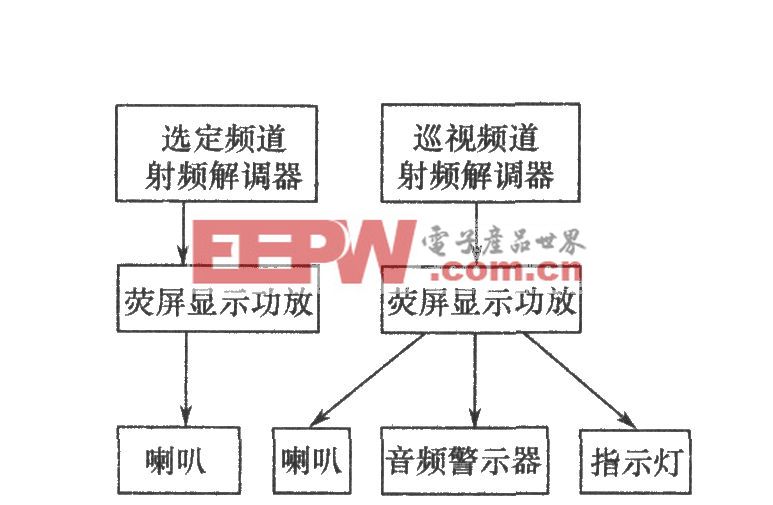

通常我们在USB线路上布局ESD防护器件:电源线与地之间会放置一颗CV0402VT6101的高分子聚合物静电抑制器,参数为:6V,100PF,0402封装;差分线对数据传送速度高达480Mbps,需要器件的结电容(即寄生电容)不能太大,不然会影响数据信号传输,我们通常先择3PF以下的,CV0402VT6030T这颗静电管的参数为6V,3PF,0402封装。这样,我们就基本从元器件部局方面对静电进行了有效的抑制和泄放。

在实际测试中,我们会发现,其实除了ESD静电的影响,USB的辐射也是一个比较难解决的问题,除了选择比较好的USB数据线外,我们还要从板内的USB走线进行有效的布局。

USB2.0的PCB布线要遵循以下原则:

(1)差分线对要保持等长匹配,否则会影响时序偏移,降低信号的质量,增加了EMI辐射问题;

(2) 差分线对之间的间距保持小于10mm,并增大与其他信号走线的间距;

(3)差分走线要求在同一板层,不同层产生的诸如阻抗、过孔的差别会破坏差模传输的效果,引起共模噪声;

(4)差分走线周边进行包地处地,并沿地隔3-5mm左右放置过孔

(5)尽量减少过孔和其他会引起线路不连续性的因素;

(6)避免导致阻值不连续性的 90°走线,使用圆弧或45°折线来代替

(7)USB端引脚附近放置ESD防护器件,并放置在端口位置 。差分线要串联贴片共模电感:CMF1210DH900MFR。以衰减EMI共模从USB线辐射出去。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。