Xilinx Zynq UltraScale+ MPSoC应用专栏系列连载[第一篇]写在前面

Xilinx Zynq UltraScale MPSoC应用专栏系列连载[第一篇]写在前面

本文作者:Hello,Panda

一、写在前面

FPGA 是可编程芯片,因此 FPGA 的设计方法包括硬件设计和软件设计两部分。硬件包括 FPGA 芯片电路、存储器、输入输出接口电路以及其他设备;软件即是相应的 HDL 程序以及最新非常流行的基于高层次综合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。

(1)选择FPGA(SoC)的若干理由

a) FPGA具有现场可编程能力,即使产品已经投入市场,也可根据特殊应用重新配置硬件;

b)FPGA具有强大的并行处理能力;

c) FPGA具有比ASIC设计更短的设计周期和更低设计成本;

d) FPGA比较易用;

e) 随着半导体技术的突飞猛进, FPGA 越来越成为一种融合处理、HBM存储、接口于一体的超级芯片。

(2)设计提醒

强烈推荐FPGA设计遵循自顶向下的设计流程,也就是说从系统级设计开始,划分为若干个二级单元,然后再把各个二级单元划分为下一层次的基本单元,一直下去,直到能够使用基本模块或者 IP 核直接实现为止。

需要特别提醒的是,大规模逻辑设计必须先有完整明确的需求和实现方案后再启动硬件平台和软件设计。否则,任何一个小的改动都可能导致极大的纠正成本甚至整个系统全盘推翻重来。

二、设计小Tips

(1)明确FPGA设计需求

和所有的设计一样,FPGA设计过程是一个迭代过程,首先是有一个系统的想法,然后将这一想法细化到具体交易中。

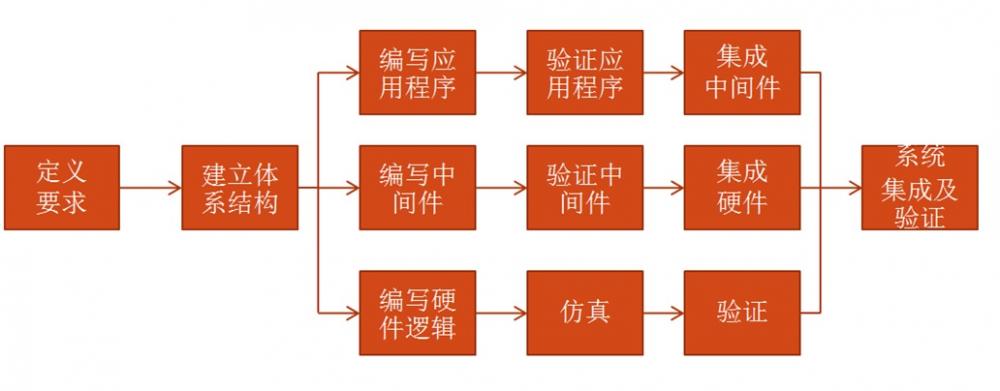

图1 需求评估拓扑

(2)如何选型

FPGA的硬件设计选型主要考虑如下因素:

1)器件的供货渠道和开发工具支持

2)器件的硬件资源

a)逻辑资源;

b) IO资源(FPGA负荷过重、发热,影响速度、稳定性和寿命);

c) 布线资源(影响速度);

d) DSP(乘法器、矢量浮点加速器)资源;

e)存储器资源(内部RAM块和内部和外部的DDR/SRAM)等;

f) 时钟资源;

g) 串行收发器;

h) 硬核及集成块。

3)器件的电气接口特性

4) 器件的速度等级

5) 器件的封装和价格等

(3)嵌入式设计流程

图2 设计流程

这个流程看上去有点像操作系统的层次结构,硬件就是FPGA逻辑和底层单元;中间件就是平台相关的可以重复利用的标准协议和接口;应用层执行产品的核心功能。这三个层级是向下验证的,最后实现系统的集成和验证。

更为具体的,针对某种器件,嵌入式工程师的主要工作如下:

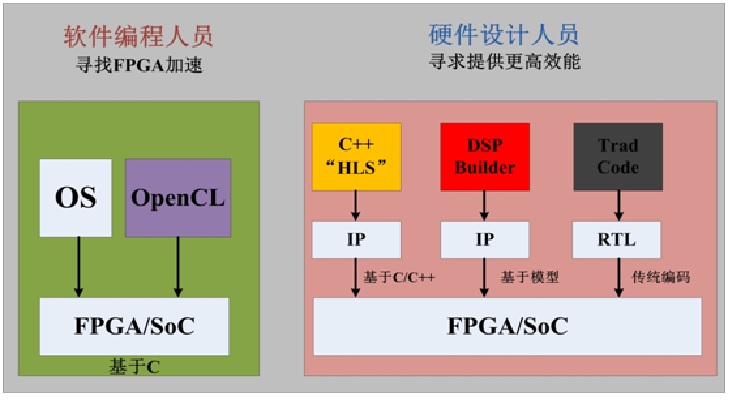

图三 设计内容

三、FPGA的几种典型应用

a)运动控制。需要高性能的工业设计领域;

b)电视广播。SDI接口已经图像流的优化重构和压缩;

c)通信领域。处理通信过程中的海量并行数据流;

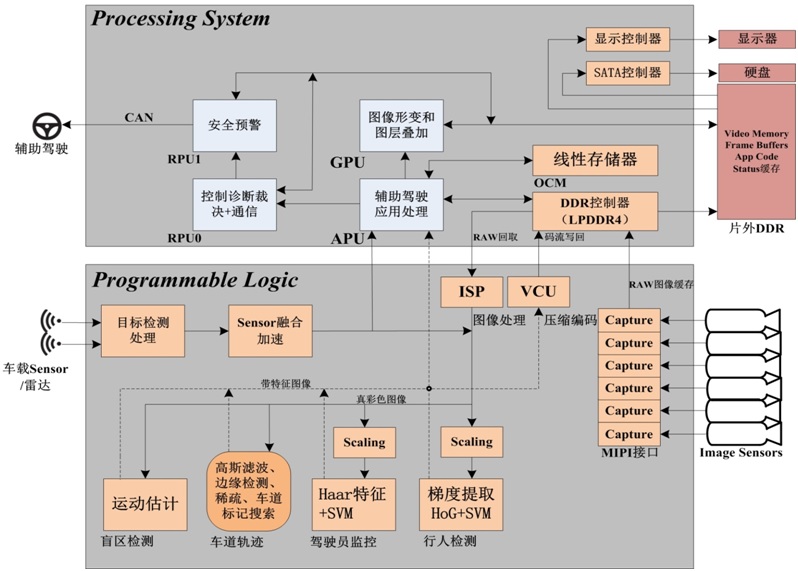

d)汽车辅助驾驶。属于对图像处理、图形、控制的集大成应用;

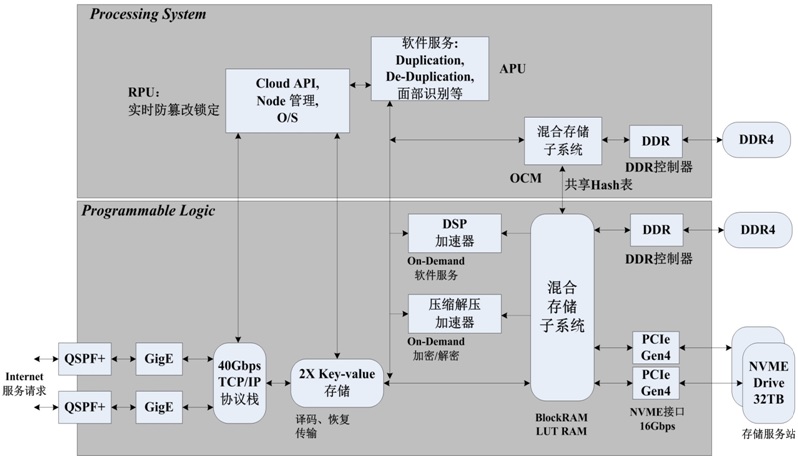

e)高性能计算。数据库、金融市场加速、地震和医学成像、矩阵数学、AI、云计算、机器学习应用等;

f)高端服务器;

g)IO和总线扩展、桥接。

随着半导体技术的飞速发展,器件的集成度越来越高,集成的硬核和功能块也越来越丰富。FPGA各厂商面向不同层次的应用也在不断的拓展,FPGA必将褪下它贵族的脸孔走入寻常百姓家。

图4 ADAS应用

图5 云级应用

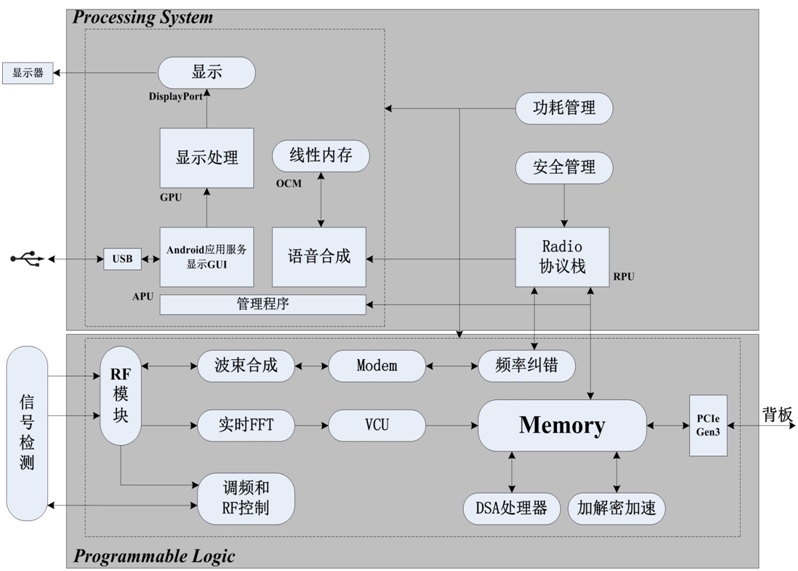

图6 软件无线电系统

图7 控制系统与移动通信

原创文章,转载请注明出处,感兴趣的同行们可加入QQ群:300148644进行进一步的技术交流!

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。