- 三角波发生器电路图如图所示,这是一个具有恒流充电和恒流放电的变形多谐振荡器,恒流源I1由VT1控制。当VT1导通时3脚呈高电平,VT2导通,I1对C2充电,充电速度为Dv0/Dt=当C2电压达到阕值电平均2/3VDD时,555被复位,3脚呈低电平,VT...

- 关键字:

三角波 发生器

- 正弦波发生器电路图,电路由IC,TL082组成。图二:正弦波信号发生器电路图

- 关键字:

正弦波 发生器

- 很多人为了守时的需要都会佩戴手表,但是除了时常电波对时的电波表之外,其他的表在跑了或长或短的时间之后,都会出现一定的偏差,这是为什么呢?机械表的不难理解,本身内部就存在不小的误差,无论怎么精工细作都难

- 关键字:

手表 时钟 同步源 功率测量

- 一 STM32 ADC 采样 频率的确定先看一些资料,确定一下STM32 ADC 的时钟:(1),由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。CLK 控制器为ADC 时钟提供一个专用的可编程预分频器。(2)一般情况下在程序 中将

- 关键字:

CLK ADC 控制器 可编程

- 关键词:I2S、主时钟、MCK、PLL、BCK、LRCK、压控振荡器、VCO、音频、模拟、半导体、德州仪器、TI信号链基础知识#54 谁是音频时钟的“老板”,谁是主,谁又是从呢?作者:Dafydd Roche,德州仪器 (TI) 音

- 关键字:

信号链 基础 时钟 音频

- 摘要:多核数字信号处理器(DSP)具有丰富的外设接口,每个外设接口具有各自独立的参考时钟。由于多核DSP具有较快的数据处理能力,对外设接口的时钟要求较高。当多个接口协同工作时,对时钟的同步要求较高。本文介绍了

- 关键字:

多核DSP 时钟 CDCM6208

- 摘要IEEE1588 标准又称为网络测量和控制系统的精确时钟同步协议标准,是 IEEE 标准委员会颁布的为了满足定位服务和无线移动通信系统高精度同步要求的标准。随着 Ethernet 技术的广泛应用,采用 IEEE1588 方式通过

- 关键字:

KeyStone IEEE1588 时钟

- 花了一天的时间,总算是了解了SystemInit()函数实现了哪些功能,初学STM32,,现记录如下(有理解错误的地方还请大侠指出):

使用的是3.5的库,用的是STM32F107VC,开发环境RVMDK4.23

我已经定义了STM32F10X_CL,SYSCLK_FREQ_72MHz

函数调用顺序:

startup_stm32f10x_cl.s(启动文件) → SystemInit() → SetSysClock () → SetSysClock

- 关键字:

STM32 时钟

- vxworks下aux clock的使用示例:利用辅助时钟进行对某些函数运行时间进行精确计时。1. vxworks映像中包含辅助时钟,包含组件hardware->peripherals->clocks->

- 关键字:

vxworks 辅助时钟 aux clk

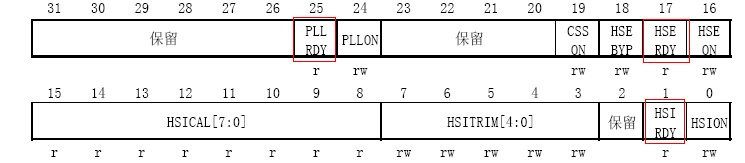

- 一:系统(SYSCLK)时钟3种 (注:时钟频率较高)

HSI振荡器时钟 8MHZ

HSE振荡器时钟 4-16MHZ

PLL 时钟 2-16倍频 PLL的设置必须在其激活前完成,激活后不能改变其状态。

1:HSI为内部8MHz RC振荡产生,启动时间比HSE短,精度较低。出厂校准精度为1%(25℃)。校准值存放在HSICAL[7:0]。

软件判断HIS是否启动完成:通过判断HSIRDY位是否为1。启动时,等HIS稳定后,硬件置位HSIRDY。可以产生中断,如果中断使能(R

- 关键字:

STM32F10X 时钟

- 3、CPU运行在晶振(32768Hz)和DCO时钟下:

最慢的频率,我们可以运行DCO约在1MHz(这也是默认速度)。

因此,我们将开始切换MCLK到DCO下。在大多数系统中,你会希望ACLK上运行的VLO或32768赫兹晶振。

由于ACLK在我们目前的代码是在晶体上运行,我们会打开DCO计算。

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

关闭看门狗定时器

if (CALBC1_1MH

- 关键字:

MSP430 时钟

- 3、CPU运行在晶振(32768Hz)和DCO时钟下:

最慢的频率,我们可以运行DCO约在1MHz(这也是默认速度)。

因此,我们将开始切换MCLK到DCO下。在大多数系统中,你会希望ACLK上运行的VLO或32768赫兹晶振。

由于ACLK在我们目前的代码是在晶体上运行,我们会打开DCO计算。

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

关闭看门狗定时器

if (CALBC1_1MH

- 关键字:

MSP430 时钟

- 实例分析:

1、CPU运行在VLO时钟下:

这是最慢的时钟,在约12千赫兹下运行。因此,我们将通过可视化的LED闪烁的红色慢慢地在约每3秒钟率。

我们可以让时钟系统默认这种状态,设置专门来操作VLO。我们将不使用任何ALCK外设时钟在此实验室工作,

但你应该认识到,ACLK来自VLO时钟。

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD;

关闭看门狗定时器

P1DIR = 0x40;

- 关键字:

MSP430 时钟

- 1、在MSP430单片机中一共有三个时钟源:

一个LFXT1CLK,为低速/高速晶振源,通常接32.768khz,也可以接(400khz~8Mhz);

一个为XT2CLK,外接标准高速晶振,通常是接8Mhz,也可以接(400khz~8Mhz);

还有一个叫DCOCLK,为内部晶振,有RC震荡回路构成。

2、在MSP430单片机内部一共有三个时钟系统:

一个为ACLK,通常由LFXT1CLK作为时钟源,可以通过软件控制改时钟的分频系数树;

一个为MCLK(Main C

- 关键字:

MSP430 时钟

- 晶振全称又叫Crystalz振荡器,它就像人体的心脏,神圣又美丽,起着至关重要的一部分.

帝国科技是国内具有一定规模的大型石英晶振生产企业,公司早期给国家军工企业专业代工,供应石英晶振,49/S,49/U,49/SSMD,6035mm,5032mm,3225mm圆柱晶振系列.

产品全部环保并且符合欧盟标准,产品有石英晶体谐振器,石英晶体振荡器,贴片晶振,圆柱晶振,SMD晶振系列.若有需要,来电咨询哦!以下是公司的产品图请欣赏!.

晶振的作用是为系统提供基本

- 关键字:

晶振 时钟

时钟(clk)发生器介绍

您好,目前还没有人创建词条时钟(clk)发生器!

欢迎您创建该词条,阐述对时钟(clk)发生器的理解,并与今后在此搜索时钟(clk)发生器的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473