STM学习笔记--STM32F10X时钟

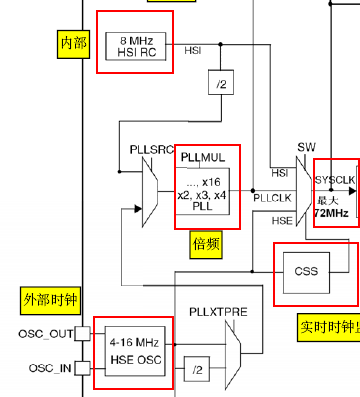

HSI振荡器时钟 8MHZ

HSE振荡器时钟 4-16MHZ

PLL 时钟 2-16倍频 PLL的设置必须在其激活前完成,激活后不能改变其状态。

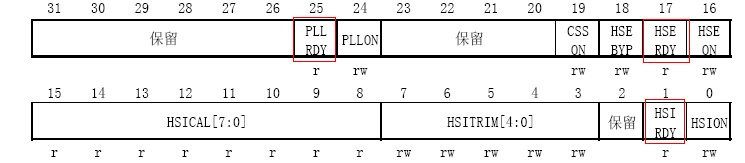

1:HSI为内部8MHz RC振荡产生,启动时间比HSE短,精度较低。出厂校准精度为1%(25℃)。校准值存放在HSICAL[7:0]。

软件判断HIS是否启动完成:通过判断HSIRDY位是否为1。启动时,等HIS稳定后,硬件置位HSIRDY。可以产生中断,如果中断使能(RCC_CIR)。

时钟切换:HSI在复位后为默认系统时钟,若改变时钟源,需等到目标时钟源准备就绪,才能够发送切换。准备就绪的标准是:RCC_CR寄存器里的状态位。

2:HSE时钟

产生方式两种:

à外部时钟源(HSE旁路):最大至25MHz

à外部晶体/陶瓷谐振器(HSE晶体):4-16MHz 负载电容需根据晶振调试

硬件配置:

软件判断HSE是否稳定:HSERDY=1,则HSE稳定。启动时,得等到HSE稳定时,硬件置位HSERDY。可以产生中断,如果中断使能(RCC_CIR)。

3:PLL为倍频HSI RC及HSE时钟。

SYSCLK外设应用

SYSCLK时钟 àI2S2/I2S3

àAPB预分频器(1-512)

à USB时钟48MHZàUSBCLK

à SDIO, FSMCCLK

à (HCLK最大72M)AHB总线,核心存储器,DMA

à APB1预分频器(1-16)最大时钟36MHZà PCLK1

à APB2预分频器(1-16)最大时钟72MHZ àPCLK2

à HCLK/2àSDIO的AHB接口

PCLK1给APB1外设使用

(DAC,,PWR,BKP,CAN,USB,I2C(1-2),USART(2-5),SPI(2-3),WWDG,TIM2-7)

PCLK2给APB2外设使用

(ADC(1-3),,USART1,TIM(1,8),SPI1,IOP(A-G),AFIO)

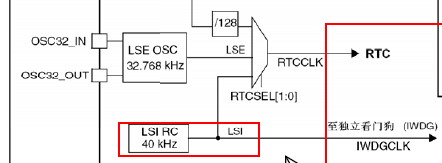

二:低速时钟LSE/LSI应用于RTC及IWDG

同理LSE 分为 àLSE旁路

àLSE外部晶体/时钟

LSE稳定软件判断:LSERDY为1,启动时,等待时钟稳定,当时钟稳定后,硬件置1。可以产生中断。

应用:RTC

LSE OSC 32.768KHZ à RTC

LSI为内部RC振荡,等待LSIRDY为1,若稳定,硬件置1,可以产生中断。

应用:独立看门狗IWDOG及RTC

LSI RC 40KHZ(30-60KHZ) à RTC 及 IWDG

三:时钟安全系统:CSS

作用是检测HSE是否出现故障,若出现故障,HSE自动关闭,立即产生中断NMI,直到CSS位中断挂起位(RCC_CIR)被清除。

评论