- 什么时钟?首先我们先讲讲什么是时钟。时钟就是单片机的心脏。每跳动一下。整个单片机的各个电路就同步的动 ...

- 关键字:

单片机 时钟 功耗

- 时钟电路:8031单片机的时钟信号通常用两种电路形式得到:内部振荡方式和外部振荡方式。在引脚XTAL1和XTAL2外接 ...

- 关键字:

51单片机 时钟 复位

- 利用核磁共振方法勘查地下水就是利用一个铺在地面上的线圈发射并接受NMR信号,线圈中需通入某一谐振频率(拉莫...

- 关键字:

低频 正弦波形 发生器

- 1、超声波发生器为了研究和利用超声波,人们已经设计和制成了许多超声波发生器。总体上讲,超声波发生器可以...

- 关键字:

超声波测距仪 发生器 压电晶体

- 凌力尔特公司(LinearTechnologyCorporation)推出一款60VDC/DC控制器LT3761,该控制器以作为恒定电流源...

- 关键字:

PWM 发生器 控制器

- 摘 要: 提出了一种采用晶振和比较器的结构实现实时时钟RTC的32. 768kHz集成晶体振荡电路的方法。设计基于UMC 0. 18um 工艺参数,并使用Hspice 对所设计的电路进行仿真,通过分析其各项性能指标,验证了电路具有起振

- 关键字:

电路 分析 设计 晶振 32.768kHz 实时 时钟 用于

- UPD78F0411 时钟控制(2)

1.4 控制内部低速振荡时钟示例

内部低速振荡时钟不能用作CPU 时钟。

只有如下外部硬件可以使用这个时钟。

#61623;看门狗定时器

#61623;8 位定时器H1 (选择fRL, fRL/27 或fRL/29 作为

- 关键字:

控制 时钟 UPD78F0411

- UPD78F0411 时钟控制(1)

UPD78F0411 时钟控制

1.1 控制高速系统时钟示例

如下两种高速系统时钟可用。

#61623;X1 时钟: 晶体/陶瓷振荡器连接到X1 和X2 引脚。

#61623;外部主系统时钟: 外部时钟输入到EXCLK 引

- 关键字:

控制 时钟 UPD78F0411

- UPD78F0411 系统时钟振荡器

1.1 X1 振荡器

X1 振荡器采用晶体振荡器或陶瓷振荡器(2 ~ 10MHz),连接到X1 和X2 引脚。

同样可以输入外部时钟。EXCLK 引脚输入时钟信号。

图5-10 为X1 振荡器的外部电路示例。

1

- 关键字:

振荡器 时钟 系统 UPD78F0411

- MSP430系列单片机是一种超低功耗控制器,它的每一系列根据不同的需要由不同的模块组成,其FLASH系列使高效电子系统变得轻巧。FLASH存储器同时也具有很强的灵活性。同时为了在低频率振荡器的驱动下得到较高的稳定频率

- 关键字:

显示 时钟 实现 单片机 MSP430

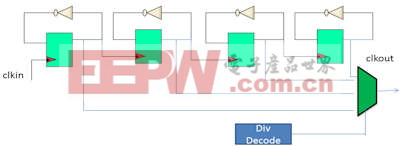

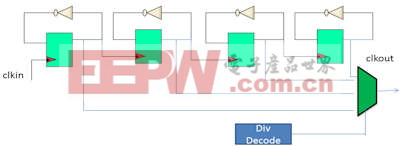

- 用于SOC或块级时钟的可配置分频器,时钟是SOC或块级设计最重要的组成部分之一,在设计概念构思/规划阶段中,需要很好地定义和理解时钟的架构。单个SOC拥有各类模块,如内核、闪存、存储器和外设,这些模块需要在不同频率下运行。它们的最大运行速率可能

- 关键字:

配置 时钟 SOC 用于

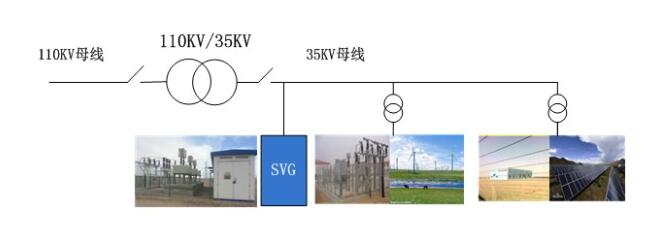

- 目前我国的风电技术大多还停留在理想电网条件下的风电机组的运行控制,而实际电网中存在有各类对称、不对称故...

- 关键字:

风力发电 电压跌落 发生器

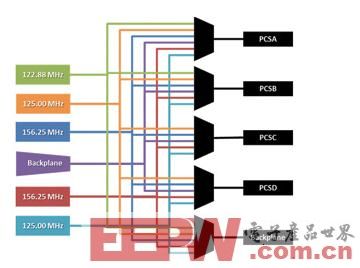

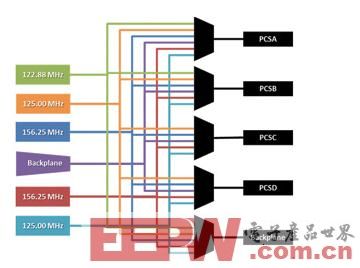

- 同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

FPGA开发团队不断面临过于繁琐、复杂的时钟网络的挑战。各种因素,包括不断增加的I/O需求、降低成本的要求和减少印刷电路板设计更改的需要,迫使设计人员重新审视时钟网络。本文将探讨FPGA时钟分配控制方面的挑战

- 关键字:

FPGA 时钟

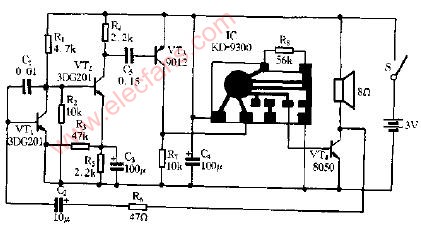

- 摘要:在这个噪声发生器电路,放大器(MAX4238)的1 /在其输入电压噪声f分量。它放大了自己的输入电压与低电阻值作出了反馈网络的噪声,避免增加明显的1 / f噪声的电阻器或放大器的输入噪声电流任。白噪声发生器(那些其

- 关键字:

4238 MAX 白噪声 发生器

- 随着电子技术产业结构调整,生产工艺的飞速发展,人们生活水平的不断提高,家用电器逐渐普及,市场对于智能时钟控制系统的需求也越来越大。本文所述智能时钟控制系统主要指时钟显示、时间设置、闹铃及家用电器定时开

- 关键字:

时钟 控制系统 智能 单片机 MCS-51 基于

时钟(clk)发生器介绍

您好,目前还没有人创建词条时钟(clk)发生器!

欢迎您创建该词条,阐述对时钟(clk)发生器的理解,并与今后在此搜索时钟(clk)发生器的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473