用ECL导线OR节省宝贵的皮秒时间

当人们借助高速ECL(射极耦合逻辑)做设计时,时钟周期之间的时间经常太少,无法在双稳态多谐振荡器之间用门电路来实现逻辑函数。在这些情况中,可以用导线OR和双稳态多谐振荡器互补逆变输出来派生等效逻辑函数(参考文献1、参考文献2、参考文献3)。可以把ECL的射极跟随器与一个下拉电阻并联,来实现几乎没有延时的OR函数。互补输出(其中一路被逆变)提供了无延时的逻辑逆变。

本文引用地址:https://www.eepw.com.cn/article/87725.htm

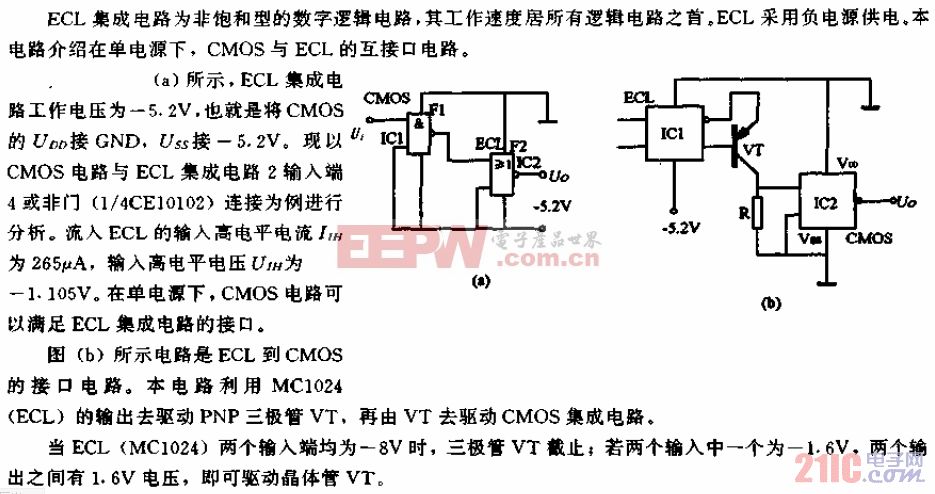

本设计实例使用较老的Motorola10HECL系列逻辑器件,当笔者在构建本设计时,最新型号已经上市(图1)。较新的ECL系列快得多,但适用相同的导线OR原理。为清晰起见,此图省略了功率电阻和50Ω下拉电阻。本设计需要在PRBS(伪随机二进制序列)数据流和本地PRBS参考(用于一个运行速率为250Mbps的BER计数器)之间做XOR比较(图1a)。但是设计遇到了一个问题:250Mbps时的时钟周期为4ns,而10H107XOR/XNOR门的最大传输延时为1.7ns。另外,10H131双稳态多谐振荡器的最大传输延时为1.8ns,并且需要的输入设置时间为0.7ns。所有这三个延时总计4.2ns,超过4ns时钟周期200ps。添加带有导线OR输出的第四个双稳态多谐振荡器,来代替10H107XOR/XNOR,就可解决这个问题(图1d)。

XNOR等效函数利用了NOR、AND、OR函数(图1b)。图1c中的电路用输出逆变器把NOR转换成等效OR,并用逆变的输入和输出把AND转换成等效OR。现在,电路只适用OR和逆变器。这种形式对于实现导线OR等效函数是必需的(图1d)。在这种情况下,双稳态多谐振荡器的逆变互补输出代替了逆变器,并且双稳态多谐振荡器的输出之间的并联电连接代替了OR门。

参考文献

1. “Using Wire-OR Ties In ECLinPS Designs,”Application Note AN1650/D, On Semiconductor.

2. “Dual D Type Master Slave Flip-flop,” MC10H131 data sheet, On Semiconductor.

3. “Triple 2-Input Exclusive OR/Exclusive NOR Gate,” MC10H107 data sheet, On Semiconductor.

评论