一种专用高速数据记录器的设计和实现

在持续数据采集存储系统中,数据存储是一项关键技术。常规的数据记录器多采用总线型设计思路。过去的做法是通过内存将采集和存储联系起来。外部采集到的数据经由PCI总线送入系统内存,然后再由主机把数据写入磁介质存储器。由于数据两次经由PCI总线进出内存,总线效率降低一半,速度也降低很多。

随着对PCI总线和SCSI总线接口协议以及计算机系统结构的了解愈加深入,现在多采用映射内存及总线主控技术,使SCSI适配器对PCI采集设备直接进行访问。由于避开了系统内存这一环节,速度得到了很大的提高。

一种常规的做法是在微机系统加一块PCI-SCSI接口卡,使数据通过高速PCI接口,由SCSI总线处理器将高速数据写入SCSI硬盘。其缺点在于数据速度受到PCI带宽的限制,而且由于对微机系统的依赖,系统难以实现模块化设计。

本文提出了一种专用的高速数据记录系统设计。设计脱离了微机系统,由DSP控制将高速数据实时持续的写入SCSI硬盘,在存储容量和传输速度等方面都具有很大的优势。此外,设备还支持数据的高速回写。

1. SCSI总线和硬盘

SCSI是英文Small Computer System Interface的缩写,译为小型计算机系统接口。SCSI是美国ANSI9.2委员会定义的计算机和外设之间的接口标准。本系统采用SCSI硬盘,因为SCSI接口本身具有很多优点:(1)SCSI提供了一个高速传输通道,目前Ultra320 SCSI总线数据传输速度可以达到320MB/s,虽然在实际应用中达不到这个理论值,但百兆比特的数据传输速度完全可以达到;(2)由于有专门的SCSI协议控制器和内嵌的处理器处理SCSI信号和数据传输,因此SCSI设备对CPU占用率低。此外还支持多任务工作模式;(3)SCSI总线占用系统资源少,还可以同时串接多台不同设备,最多时可达15个;(4)SCSI硬盘在标识硬盘扇区时使用了线形的概念,即硬盘只有顺序的第1扇区、第2扇区,第n扇区,不像IDE硬盘的“柱面/磁头/扇区”三维格局。这种线形编排方式的优点是访问时间小,可以有效地加快磁盘存取速度,尤其在持续大容量数据存储时,优势更为明显。此外,通过挂接多个硬盘组成磁盘阵列可以大大地增加数据的存储容量。

2. 系统结构设计

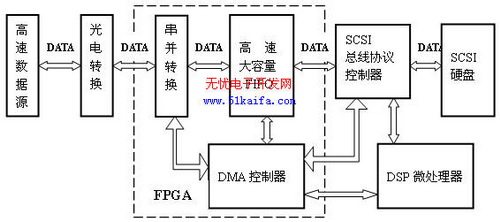

整个系统的设计结构[1]框图如图1所示,主要包括以下几部分:高速数据源(不在本文设计中)、光电转换和串并转换单元、高速大容量的数据缓存、微处理器、DMA控制器、SCSI协议处理器以及高速SCSI硬盘。下面逐一介绍。

2.1 光电转换和串并转换单元

系统的高速数据源为光接口,记录器接收到光信号后,首先经过光电转换变为串行的电信号,再经过串并转换变为16位的并行数据。

采用光接口的主要原因在于:光纤通道(Fibre Channel) 是一种高性能的串行数据接口,支持SCSI、ATM等上层数据传输协议,具有可靠性高、速度快和传输距离远的特点,特别适合高速大容量的信息传输。

2.2 高速大容量的数据缓存

图1:高速数据记录器结构框图

数据缓存的主要作用在于实现速度匹配,为高速DMA传输做好准备。

普通的SRAM存储器只有一套数据、地址和控制总线,无法同时进行读写操作。双口RAM有两套数据、地址和控制总线,可以同时进行读写操作。但其编译码电路复杂,而且价格相对较高。由于我们对数据不进行任何处理,只是单纯的数据存储,缓存单元在结构上相当于一个先入先出(FIFO: First In First Out),先到的数据先被存储。设计中,我们利用现场可编程门阵列(FPGA:Field Programmable Gate Array)实现一个高速FIFO,省去了复杂的编译码电路,大大简化了系统设计。而且,从外部数据接口看来,设备就是一个写不满的FIFO,也大大简化了对设备数据接口的操作。

2.3 微处理器

用来控制设备中各部分的工作,实现设备的特定功能。高速数据记录器主要实现数据持续高速存储,对数据处理的速度要求较高。通常采用数字信号处理器(DSP:Digital Signal Processing)作为微处理器。

2.4 DMA控制器

设计中,为保证大量数据的高速持续传输,采用直接存储器访问(DMA:Direct Memory Access)方式,因此需要DMA控制器单元。为了简化电路,提高效率,设备采用FPGA构造一个单独的DMA控制器。

2.5 SCSI协议处理器

无论DSP还是FPGA,通常都不会集成SCSI协议控制器。因此我们用专门的SCSI协议控制器来实现SCSI协议,辅助DSP来实现SCSI协议和通信。

2.6 SCSI硬盘

采用SCSI硬盘可以实现数据高速存储,而且通过增加磁盘数目可以很方便的扩展存储容量。

3. 硬件电路的实现

前面我们已经逐一介绍了系统各部分的功能,下面我们介绍一下高速数据记录器的硬件电路的实现。

由于设备采用光接口,当高速数据流进入设备后,首先我们需要进行光电转换和串并转换。光电转换可以通过专门的光电转换芯片实现,而串并转换我们利用某些FPGA内嵌的收发器模块(Transceiver)来实现。这样做既可以保证数据的高速传输,又可以有效地保证时钟同步,实现字对齐,可靠性高。

高速数据缓存通常采用专用FIFO,但价格较高。我们利用FPGA来实现一个大容量的FIFO,即简化了系统,又提高了效率。前面已经介绍过专用的DMA控制器连接电路复杂,我们用FPGA来设计一个单独的DMA控制器同样可以简化电路,提高效率。

设计中,串并转换单元、高速数据缓存和DMA控制器都利用FPGA编程实现(如图1虚线所示)。用高度集成的FPGA取代分立元件进行高速数据传输设计是本文的一个重要特点。

微处理器我们采用德克萨斯仪器(TI:Texas Instruments)公司生产的数字信号处理器MS320F206;SCSI协议控制器则选用Qlogic公司的FAS660。

下面我们对SCSI协议控制器FAS660[3]做进一步的介绍。

FAS660是Qlogic公司推出的一款高性能SCSI引擎,它源于Qlogic公司的TEC485三重嵌入式控制器系列。可提供Fast-160的同步传输速率,支持先进的SCSI自动配置模式SCAM的1层和2层协议。内部嵌有微控制器,能够用编程的方法灵活的协调SCSI作业队列。FAS660和主流SCSI接口芯片最大的区别在于:主流SCSI接口芯片采用的是PCI总线接口,而FAS660采用的是微处理器和DMA接口的结构。这使得FAS660更为灵活,可以根据需要进行多种接口设计,尤其适合应用在一些专用SCSI总线控制场合。

4. 系统的软件设计

在硬件设计的基础上,还需要软件模块

负责对相关硬件进行控制和协调,最终实现SCSI协议、硬盘的控制和DMA传输等。软件模块的设计是本系统的难点和重点。本系统中,软件设计主要分为两部分:DSP控制软件和FPGA实现的DMA控制器,此外还有FPGA实现的串并转换和高速FIFO。程序的优劣关系到整个系统数据存储的性能,下面分别进行讨论。

4.1 FPGA设计

FPGA设计主要包括异步收发器模块、高速异步FIFO缓冲模块、DMA控制器模块以及时钟生成模块。FPGA作为设计中的重要一部分,用来实现数据传输的准备(包括串并转换、高速缓冲以及加入奇偶校验、CRC校验)和对读写逻辑的控制。

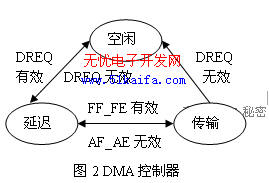

图2 DMA控制器状态机

DMA控制器是FPGA设计的主要工作。我们通过DMA控制器,实现传输数据的控制逻辑,同时对前端传来的数据(没有任何保护)加以保护(通常指奇偶校验保护和CRC校验保护)。它的控制逻辑相当简单。当FAS660发送数据传输请求(声明DREQ),如果FIFO非空,则经过延时后,开始数据传输(声明DACK)。FAS660的读写操作非常相似,但也有一些差别。读操作在DACK有效后的第二个DMA时钟周期开始传输,而写操作在DACK有效后的第一个DMA时钟周期开始传输。在FPGA设计的内部逻辑时尤其需要注意。

Altera公司为StratixGX系列FPGA提供了gxb(吉比特收发器) 、fifo(先入先出)、pll(锁相环)等MEGAFUCTION,通过对它们进行例化可以很方便地实现高速收发器,高速FIFO和时钟生成等模块。

4.2 DSP控制软件

基于FAS660的系统可以通过DSP微处理器和FAS660(内部有单独的微控制器和SCSI控制器用来实现SCSI协议)的协调工作来实现系统功能。一般来说,要完成一次数据交换必须完成SCSI总线的仲裁、选择、消息、命令、数据和状态等阶段,这些阶段通过为处理器TMS320F206对FAS660寄存器[4]的读写命令来实现。

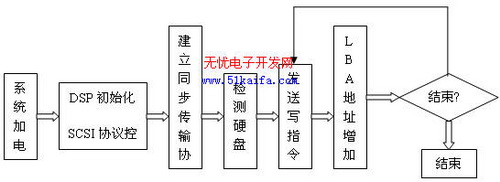

SCSI控制软件流程如图3所示。首先初始化设备,然后建立同步传输协议,检测硬盘。硬盘准备好后就可以进行数据传输。

图3 DSP控制软件流程

5. 结束语

本文介绍了一种光接口的专用高速数据记录器的设计。它脱离了微机平台,用DSP微处理器做控制,用专门的SCSI总线控制器处理SCSI总线信号,并建立了一个高速DMA通道,将数据高速持续的存储到SCSI磁盘阵列中。设计速度高,容量大,可移植性好,可以灵活应用到各种系统中。

本文作者创新点:

1.专用型记录器的设计思路,避免了总线带宽限制,可以达到更高的传输速度。

2.用DSP做为本地CPU,控制整个系统,脱离了微机系统,实现了模块化设计。

3.用高度集成的FPGA取代了多个分立元件(FIFO,串并转换,DMA控制器)。

4.源端数据采用光接口传输,可靠性高,速度快。

参考文献:

[1]姜凤山,雷宏. 一种基于FAS466的合成孔径雷达高速数据记录器的设计.电子技术应用,2004.6。

[2]何苏勤,王忠勇.TMS320C2000系列DSP原理及实用技术.北京:电子工业出版社,2003.9。

[3]Qlogic Corporation.FAS660 fast architecture SCSI processor technical manual,2002.7。

[4]Qlogic Corporation.FAS660 Fast Architecture SCSI Processor Designer’Guide,2003.1。

[5]吴志祥,汪波,基于ISCSI的存储系统实现方法. 微计算机信息,2006,3-3。

合成孔径雷达相关文章:合成孔径雷达原理

评论