可定制软微处理器内核的配置策略

可定制微处理器内核有两个特性:可配置性和可扩展性。可配置性是指设计工程师可以更改处理器的现有特性。可扩展性是指能加入处理器本身没有的功能特点,从而增加处理器的基本功能。

本文引用地址:https://www.eepw.com.cn/article/85720.htm从底层修改CPU结构的能力使得用户可定制处理器很显著地区别于传统的结构固定的CPU,设计工程师在设计处理器功能时有更大的自由度,例如:在设计时可以根据具体的应用需要定义一组指令;加入新的通用寄存器;定义新的条件代码;根据在仿真器上运行的软件反馈信息来精细地调整指令和数据缓存的大小和结构;在SRAM或逻辑电路内实现内核寄存器文件以及加入本地中间结果暂存RAM;加入强大的DSP处理功能,如乘法累加(MAC)指令和本地XY数据存储器。

此外,输入输出(I/O)的配置也很灵活。为了达到高的I/O速率,设计工程师可以将指令总线和数据总线分开(哈佛结构);为了减少管脚数和减小封装成本,数据和指令总线用统一总线(冯•诺曼结构)。可以把特定应用逻辑与处理器内核紧密相连,用其本身的I/O总线加入辅助寄存器文件。用户定义的指令可以提高一些关键软件算法的性能,从而提高整个系统的性能。

以前这种设计只能是由CPU厂商的高级工程师完成。在可综合的HDL、先进的EDA工具以及可定制的软处理器内核出现后,一般的嵌入式系统设计工程师在他们的SoC、ASIC和ASSP设计时就拥有控制系统架构的自由。

可定制IP的优越性

采用IP供应商提供的微处理器可综合HDL源代码(VHDL或Verilog格式)的优点包括:软内核独立于加工工艺、库、代工厂,因此在生产上有很大的灵活性;用户可以在这些HDL源代码基础上进行修改并保护专有的技术诀窍。

对用户可定制处理器内核进行开发的初期,只有IP供应商定义的最低限度的规范或基本内核。对于一些不需特别优化的深度嵌入式应用可以使用这种基本内核。但是,可定制处理器的真正魅力是其可被修改的特点,设计工程师可以对基本内核进行配置并根据需要进行功能扩展。

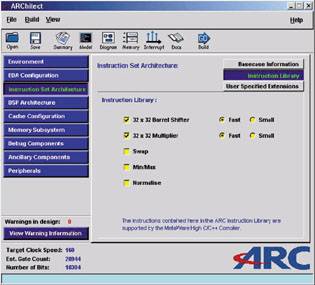

对可定制处理器的配置和功能扩展并不一定采用HDL编码。通过处理器配置图形工具,设计工程师甚至不用看HDL源代码就可以作大量的修改。通过简单的“点击、选择”界面进行选项设置,配置工具能自动生成HDL文件以及用于逻辑综合的脚本文件。例如对于ARCtangen-A4处理器, ARC处理器内核提供如图所示的ARChitect配置工具。

ARChitect工具允许设计工程师设置和扩展指令集、中断、指令缓存、数据缓存、存储器子系统以及DSP功能,还可以加入外围器件,如以太网的媒体访问控制器(MAC)以及用于实时处理的32位计时器。另外一个可选的设置是时钟选通,可以关断部分不需要的电路,具有节电功能。

ARCtangen-A4处理器的基本指令集包括所有的基本算术指令、逻辑指令、加载/存储以及分支/跳转操作指令,这些指令是典型的嵌入式应用所必需的。通过使用ARChitect工具,设计工程师可以从一个库中选择另外的指令和功能特点。例如,一个硬件可控阵列移位器(hardware barrel shifter)和相关的指令尤其适合用于网络信息处理中在数据包中插入或提取数据包头或一段数据位。还有两个不同的硬件乘法器可以用来加速算术功能以及其它任务的处理。用于数字信号应用的DSP指令还能在内核中优化。

可定制处理器供应商不可能预料到系统设计工程师需求的所有扩展指令,因为用户定义的指令需要进行HDL编码。为精简这种扩展处理过程,处理器HDL源代码的设计中已经考虑了这种扩展,在原代码内已经清楚地对用户插入代码进行了标记和文件接口。

另外,所加入的额外寄存器非常有用,在配合用户指令和其它逻辑功能时尤其如此。例如,一个“智能”寄存器能自动地对写入该寄存器的值进行四舍五入处理;辅助寄存器与用户逻辑和外围器件一起能实现高性能的I/O。

用户条件代码是另外一个使软件更智能化的方法。在ARCtangen-A4处理器条件下,条件指令集允许通过读一个条件代码(状态标志)来决定每个指令是否执行。设计工程师可以为实现某个目标来建立自己的条件代码。例如,网络处理器在从网络收到一个数据包时可能会设置一个标志位。基本指令和用户定义指令可以根据条件代码的状态有条件地执行。

在整个开发周期中,设计工程师可以在可定制处理器中反复分配硬件和软件的任务。例如,可以通过仿真器和设计工具中Profiler提供的反馈信息,让那些性能很关键的软件由用户指令来实现。可以定义专用操作数、助记符、寄存器和功能,从而使设计工程师能把内部循环操作由硬件来实现,进而执行复杂多周期指令,提高处理器的速度性能。这不仅提高了性能,而且使产品的硬件多样化,通过提高盗版难度达到保护知识产权的目的。

定制功能并不意味着总要进行功能扩展。设计工程师也可以从处理器中去除不需要的指令和其它功能,减小处理器的门数,降低功耗和制造成本。

灵活的缓存结构

在配置可定制处理器内核时,设计工程师需要注意缓存结构对功耗和硅片面积的影响。因此要均衡考虑指令缓存和数据缓存的结构。

从广义上说,缓存结构包括直接映射(direct mapped)和多路(multiway)配置两类。这两种结构都互有优缺点,要根据具体的应用来选择最佳的类型。

直接映射缓存是两者中较简单的一类,因此需要的门数较少。功耗是门数的函数,所以直接映射缓存的功耗小。但如果直接映射产生的缓存空间丢失(miss)比多路配置缓存更多,那么由于处理器需要经常访问存储器,功耗反而会增加。

实际上功耗并不是唯一的考虑因素,在有些应用中不允许太多的缓存丢失。例如,由于音频处理是一个实时处理过程,频繁的缓存丢失会造成音频质量下降。多路缓存能改善直接映射缓存的不确定性,提高有效访问率,但其代价是功耗更大和门数更多。设计工程师在做选择时常常难以权衡。例如,在设计电池供电的MP3音播放器时,一方面多路缓存适合于实时的音频处理,另一方面多路缓存功耗更大。这个矛盾可以从优化缓存的大小和结构来解决。利用现在先进的仿真工具对设计会有很大的帮助。

好的缓存设计还有其它的要求。例如线锁(line locking)功能,能对部分的缓存进行保护以避免在出现缓存遗失时被处理器刷新。

传统的CPU结构是固定的,设计工程师只能对其作很少的修改甚至是不能改动。而用户可制定的处理器却给设计工程师带来了最大的自由度,能根据具体的应用进行真正的最优化设计。

本文结论

如果微处理器以可定制软IP 形式提供时,在项目进行的任何阶段都可以进行修改。设计工程师可以在他们原有的设计基础上改变,而不必放弃原来的设计从零开始,这样更能满足快速变化的市场要求。如果产品规范发展到使原来的软件运行缓慢,设计工程师可以改变可定制处理器来解决这个问题。如果要降低成本,设计工程师可以从硬件和软件中去除一些功能。可定制软IP让真正了解设计的工程师可以设计出满足需要的最优化CPU。

评论