利用Allegro实现嵌入式系统高速电路布线设计

1.在Allegr o的assign diff pair菜单中选择建立差分对的信号Tx+/-,命名为TX_Pair。

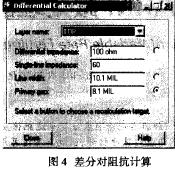

本文引用地址:http://www.eepw.com.cn/article/85065.htm2.按照对信号TX+/-阻抗控制要求计算差分对线宽、线距,如图4所示,选择走线层面top层,填入差分对阻抗100欧,单线阻抗60欧,得到线宽10.1mil,主要线间距8.1mil。

3.定义差分对TX_PAIR电气约束条件:

主要线宽,线间距:10mil/8mil;

次要线宽/线间距:10mil/8mi;

线最小间距:6mil;

两条线无法走到一起时允许的线长:100mil;

两条线可允许的误差值:25mil。

4.分配差分对TX_PAIR到电气约束集,打开差分对DRC模式。

图4差分对阻抗计算

以上实现差分对走线和阻抗控制的方法在涉及到大量差分对的通信系统电路中非常简单实用。

4 结语

笔者利用强大的PCB设计软件Allegro实现了基于EP9315嵌入式系统的硬件电路设计。该板采用6层PCB布线,完全满足高速电路设计中对等长、差分、阻抗控制的要求。 基于该电路设计的嵌入式系统与武汉中科院岩土力学所设计的SY5声波工程检测仪实现了良好接口,与由51单片机搭建的原 SY5 声波仪相比,改系统功耗降低,体积变小,稳定性增强,成本降低,更适合工业控制中的运用。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)DIY机械键盘相关社区:机械键盘DIY

评论