利用Allegro实现嵌入式系统高速电路布线设计

3.2 Xnet在IDE总线等长布线中的应用

本文引用地址:http://www.eepw.com.cn/article/85065.htm3.2.1系统中的IDE接口设计

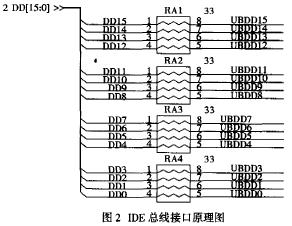

EP9315强大的外设接口能力能够直接驱动IDE硬盘 ,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置 propagation_delay和relative_propagation_delay只能针对同一NET设置.IDE总线信号由EP9315扇出,要求EP9315到IDE接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和 UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。而UBDD*没有足够绕线空间时。这样设置等长不可行。Allegro提供了一种方法,将DD*和UBDD*走线相加再进行等长比对,这就要用到Xnet。

图2 IDE总线接口原理图

3.2.2 Xnet概念和Xnet等长设置

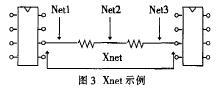

通常把连续的几段由无源元件(电阻,电容或电感)连接的NET合称为Xnet,如图3所示。

Xnet示例

图3 Xnet示例

图2中将DD*和UBDD*设置为同一个Xnet。对属于该Xnet的所有信号等长控制。Xnet等长设置分为以下步骤:

1.设置Xnet

选择要设置Xnet的器件(图2中为排阻RA1-RA4),创建ESpiceDevice model,Allegro将自动填入模型名称,电路类型-Resistor,PIN连接顺序:1,8,2,7,3,6,4,5,表示1和8是一个电阻 (见图2)。至此,查看排阻两边NET都添加了同一Xnet属性。

2.Xnet的等长设置

(1)建立Xnet的pin pair:在Allegro中打开constraint manager,选择relative_propagation_delay属性。已设置的Xnet自动显示,选择Xnet建立pin pair,Allegro提供整个项目中Xnet关联的起始pin和结束pin。选择需要等长设置的起始pin和结束pin。

(2)建立等长 group:选中所有需要设置等长的pin pair,创建名为R_IDE_DATA的MATCH GROUP,在与relative_ propagation_delay对应的工作窗体选择区中出现了刚创建的R_IDE_DATA,其内含建立的pin pair,按照IDE总线走线等长要求设置走线误差10mil以内,一般选择最长走线为基准线(target)。

(3)走线完成后,重新打开constrait manager对实际走线进行分析,Allergo自动显示分析结果,绿色表示走线以基准线为标准。走线误差在10mil以内。红色表示走线误差超过10mil,如果分析结果,大部分走线都为红色,可以适当调整基准线的选择。

此外,Allegro在等长走线时。会实时显示走线长度是否在误差范围内,可以使用蛇型线调整走线长度。这些都极大的确保了布线可靠性。

3.3差分线和阻抗控制在网络布线中的应用

3.2.1物理层接口芯片cs8952布线准则

CS8952使用CMOS技术。提供一个高性能的100Base-X/10Base-T物理层(PHY)线路接口。它使自适应均衡器达到最优化的抗扰性和抗近端串扰(NEXT)性。可将接收器的应用扩展至超过160米的电缆,它结合了一个标准介质无关端口(MII),可简便地连接微处理器EP9315的介质访问控制器(MAC)。

以下一些PCB布线规则,将使得CS8952工作更加稳定并得到良好的EMC性能:

1. 使用多层电路板,至少有一个电源层,一个地层,叠层设置为:top,gnd,VCC,bottom。使用底层pcb走信号线只作为第二选择。把所有的元件都放在顶层。然而,旁路电容优选越靠近芯片越好,最好放置在CS8952下方的底层pcb上。RJ45终端元件和光纤元件可以选择放在底层。

2.4.99k的参考电阻应该越靠近RES管脚越好,把电阻另外一端使用一个过孔接到地平面。邻近的vss(85和87脚)接在电阻接地端,形成一个屏蔽。

3.对关键信号Tx+/-,RX+/-,RX_NRz+/-控制阻抗,作为微带传输线(差分对100欧,单线60欧),MII信号作为68欧微带传输线。

4.差分传输线布线应靠近(线宽间距6-8mil),与其他走线、元件保证2个线宽的距离。TX和RX差分对布线远离彼此。必要时使用pcb的相对面。

3.2.2网络部分关键信号差分走线和阻抗控制的设置

网络部分差分线及其阻抗控制以信号Tx+/-为例。步骤如下:

linux操作系统文章专题:linux操作系统详解(linux不再难懂)DIY机械键盘相关社区:机械键盘DIY

评论