编写高效的测试设计(testbenches)

简介:

本文引用地址:https://www.eepw.com.cn/article/84843.htm由于设计的规模越来越大和越来越复杂,数字设计的验证已经成为一个日益困难和繁琐的事。面对挑战,验证工程师们依靠许多的验证工具和方法。对于大的系统,如几百万门的设计,工程师们一般使用一套可靠的验证工具。当然,对于一些小的设计,设计工程师常常发现带有测试的hdl仿真器就可以做得很好。

测试设计已经成为一个验证高级语言设计HLL (High-Level Language) 的标准方法。

典型的,测试设计完成以下任务:

实现测试设计;

仿真通过使用模块的测试向量来仿真测试设计;

输出结果到终端或波形窗口以检视;

可选择的将实际结果和预期结果进行比较。

一般测试设计使用工业标准的VHDL或verilog硬件描述语言来编写。测试设计调用功能设计,然后仿真。复杂的测试设计完成一些附加的功能----如它们包含逻辑来为设计决定适当的设计激励或比较实际结果和预期结果。

后续的章节说明了一个非常稳定的测试设计的结构,并且提供了一个自较验测例子----它将自动比较实际结果和测试设计的预期结果。

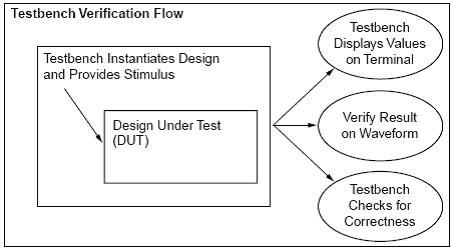

图1说明一个基于以上基本要求的标准的hdl验证流程。由于测试设计使用VHDL或verilogHDL来描述,测试设计的验证过程可以在不同的平台或不同公司的软件工具环境完成。另外,由于VHDL或verilogHDL是公开的通用标准语言,使用VHDL或verilogHDL来描述验证设计可以毫无困难的在将来重用。

图1使用测试设计的HDL测试验证流程

构建测试设计:

测试设计可以用VHDL或verilogHDL来描述.因为测试设计只用来进行仿真,它们没有那些适应综合中仅应用的rtl语言子集的语法约束的限制.而是所有的行为结构都可以使用。从而测试设计可以编写的更为通用,使得它们可以更容易维护。

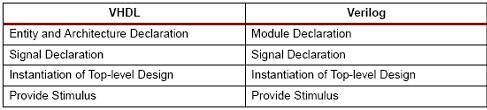

所有的测试设计包含了如表1的基本程序段块。正如上面所提到的,测试设计一般包含更多的附加功能,如在终端上可视的结果和内建的错误检测。

测试设计的基本程序段

下面的例子说明经常使用的测试设计的结构。

产生时钟信号

使用系统时钟来的时序逻辑设计必须产生时钟。重复的时钟信号可以很容易的在vhdl或verilog源码中实现。以下是vhdl和verilog的时钟发生示例。

VHDL:

-- Declare a clock period constant.

Constant ClockPeriod : TIME := 10 ns;

-- Clock Generation method 1:

Clock <= not Clock after ClockPeriod / 2;

-- Clock Generation method 2:

GENERATE CLOCK: process

begin

wait for (ClockPeriod / 2)

Clock <= ’1’;

wait for (ClockPeriod / 2)

Clock <= ’0’;

end process;

Verilog:

// Declare a clock period constant.

Parameter ClockPeriod = 10;

// Clock Generation method 1:

initial begin

forever Clock = #(ClockPeriod / 2) ~ Clock;

end

// Clock Generation method 2:

initial begin

always #(ClockPeriod / 2) Clock = ~Clock;

end

准备激励信号

为了获得测试设计的验证结果,激励必须在测试设计中提供。在测试设计中使用的并行激励块提供必要的激励。两个方法被考虑:绝对时间激励和相对时间激励。在第一个方法里,仿真变量被详细描述为相对于仿真时间零点。通过比较,相对时间激励提供初始值,然后在重触发激励前等待一个事件。根据设计者的需要,两种方法可以在测试设计中组合使用。

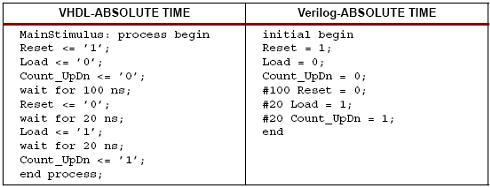

表2 绝对时间激励

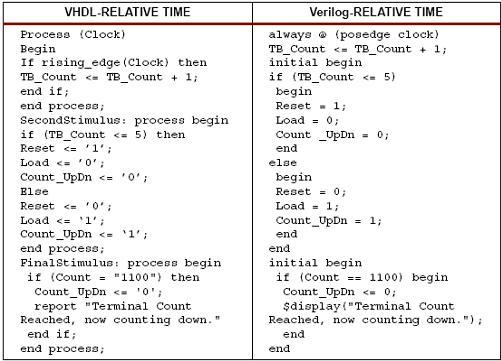

表2和表3分别以vhdl和verilog提供了一个绝对时间激励和相对时间激励的源代码。

表3 相对时间激励

评论