可编程系统级芯片使设计灵活性最大化

——

可编程系统级芯片使设计灵活性最大化

近几年来,有关系统级芯片(SOC)原理的讨论一直在持续着。虽然这些器件已经向世人展现了它们所具有的通过整合的方法来大幅度地缩减设计方案物理尺寸的能力,但许多设计师却对其总体灵活性稍感不满。

在某个特定的设计中,往往需要一种特殊的或“尚不具备”的功能。这种需要有可能迫使设计师不得不增设一些器件,以便能够把他们所需要的特殊功能添加进去。有时从某种意义上讲,该SOC架构或许还会成为一种负担(而并非一种可用的资源),因而导致设计师希望拥有更加优越的替代选择。

更加重要的是,大多数SOC都具有一定的专用性,因此是围绕着高级功能而开发的,因而完全不适用于众多的消费类和工业产品设计。显然,设计师需要的是一种能够适合于更加广泛的用途的、灵活性更高的解决方案。

应对这样的需求,赛普拉斯微系统公司(Cypress MicroSystems)推出了名为PSoC(Programmable System-On-Chip,可编程系统级芯片)可编程的混合信号SOC。

虽然赛普拉斯微系统公司的PSoC的核心是一个8位微处理器,但事实上,它很少被称为“微控制器”,而是被称作一个具有嵌入式微控制器内核的混合信号阵列。

正像这种描述性更强的名称所暗示的那样,PSoC是一种对于标准的“全数字式”微控制器设计、纯粹的模拟设计以及介乎此二者之间的所有设计而言具有同等的上佳适用性的器件。

如果想了解PSoC,那么首先必须搞清一个新的概念。这种新概念指的就是被称为“用户模块”的通用且可配置的模拟、数字和混合信号积木式部件的概念。用户模块的主要任务就是向设计师提供几组能够由其进行配置和互连的通用积木式部件,以便执行多种功能。

对于大多数设计师来说,复合可编程逻辑器件(CPLD)的“宏单元”是他们所熟悉的对用户模块最为贴近的类比。每个单元(同样,每个用户模块)都是根据核心功能来构筑的,当对其进行配置时,就会产生定制功能或板载外围元件的最终结果。

PSoC包括多种用户模块,与CPLD的宏单元非常相似,这些用户模块也可由设计师随意配置。不过,需要牢记的是:与CPLD不同,PSoC还包括能够完全以模拟方式(无需使用数字电路或CPU等等)来处理信号的用户模块。

事实上,当采用PSoC时,实际上能够创建一个“纯模拟型”的设计方案,在这种方案中,CPU内核除了按设计师的规定在上电期间执行配置代码以外根本不运行!此外,PSoC Designer开发工具还能够自动生成该配置的全部代码 …… 后文将对此做更加详细的阐述。

你可能对此感惊讶。如果你驻足思考一下你所做过的许多设计,就有可能意识到有一些关键的“积木式部件”是你曾经反复使用过的。赛普拉斯微系统公司的芯片设计人员也认识到了这一点。正是这种领悟导致了上述用户模块的开发成功。

为了提供最大的灵活性并满足大多数应用的需要,人们意识到有些基本积木式部件将是必须的,即:

(1) 一个8位CPU内核。

(2) 通用型数字用户模块。

(3) 具有通信能力的通用型数字用户模块。

(4) 模拟连续时间用户模块。

(5) 模拟开关电容器用户模块。

(6) 确定各种信号输入和输出器件的线路的能力。

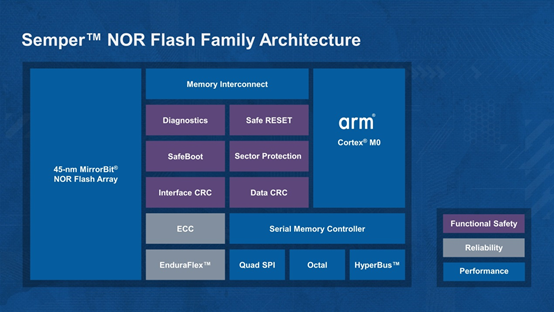

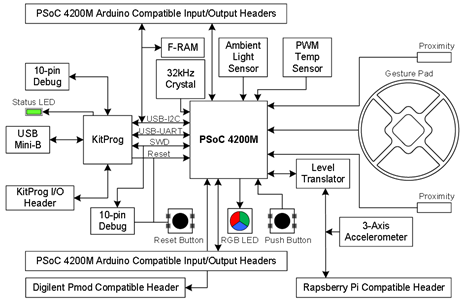

上面的“核心”功能列表形成了构筑PSoC器件系列的基本平台。为了使该器件具有最大的灵活性和能力,许多附加部件也被融入其中。图1示出了包含所有子系统的现行PSoC器件的方框图。

由图1可见,PSoC包括了大多数“纯数字型”微控制器的全部标准外围元件以及众多的新型部件和创新部件。

图1,PSoC的内部结构

数字模块

显而易见,列表的第一项——8位CPU内核是必不可少的。目前的PSoC系列的核心基于赛普拉斯半导体公司从其名为M8的USB控制器系列派生而来的成熟内核。这种哈佛(Harvard)架构内核能够在24MHz的频率下具有高达4MIPS的操作性能,并满足了非常苛刻的USB睡眠功耗规范要求。该器件具有一个具有全面可编程性的内部CPU时钟,甚至在正常操作期间也可对其加以改变。这意味着该PSoC能够实现一个全混合信号设计,而无需任何的外部元件(当然,电源除外)。

为了使该内核在PSoC中具有更高的能力,还增加了一些新型部件。这些部件包括一个硬件乘法-累加寄存器(MAC)、能够被分割并用作嵌入式EEPROM的FLASH代码空间、板载低电压检测以及嵌入式睡眠定时器等等。

该PSoC的CPU内核允许对所有由用户模块配置组成的特殊功能寄存器进行存取操作。在这种场合,该内核还支持一种名为“动态重构”的概念。这一能力使得PSoC能够在固件的控制之下对其所有的用户模块进行全面重构,并由此获得一个全新的“个性”和功能。(参见附文《定义个性化的的动态重构功能》)

我们给出的积木式部件列表的第二项和第三项形成了数字用户模块组的基础。这些用户模块是通用型数字功能部件,它们支持面向各种“数字”板载外围器件(包括计数器、定时器、脉宽调制器、UART、SPI、IrDA和CRC功能元件)的配置。

模拟功能

提到我们列表中的第四项(模拟连续时间用户模块),目前我们已经拥有了一个用于形成纯模拟连续时间积木式部件(比如:可编程增益放大器、模拟比较器、差分放大器和滤波器等不一而足)的框架。这些部件能够在无需CPU等的参与的情况下运行(只需在上电时进行初始化),并可在某些形式的“睡眠”或CPU暂停操作的条件下继续运行。

图2示出了PSoC的模拟连续时间用户模块的内部布线能力。

图2,PSoC模拟连续时间用户模块

尽管我们列表中和第一项至第四项对大多数设计师而言都比较熟悉,但第五项“开关电容器用户模块”恐怕就要稍显陌生了。在讨论开关电容器用户模块之前,有必要了解有关PSoC的一个重要事项,这就是第六项所提到的:该PSoC不仅包括上述的所有积木式部件,还包括用于对这些积木式部件进行内部互连、将外部信号输入以及将内部信号输出所必需的全部路由选择资源。模拟信号传送路径也包括在内。

在某个特定的设计中,往往需要一种特殊的或“尚不具备”的功能。这种需要有可能迫使设计师不得不增设一些器件,以便能够把他们所需要的特殊功能添加进去。有时从某种意义上讲,该SOC架构或许还会成为一种负担(而并非一种可用的资源),因而导致设计师希望拥有更加优越的替代选择。

更加重要的是,大多数SOC都具有一定的专用性,因此是围绕着高级功能而开发的,因而完全不适用于众多的消费类和工业产品设计。显然,设计师需要的是一种能够适合于更加广泛的用途的、灵活性更高的解决方案。

应对这样的需求,赛普拉斯微系统公司(Cypress MicroSystems)推出了名为PSoC(Programmable System-On-Chip,可编程系统级芯片)可编程的混合信号SOC。

虽然赛普拉斯微系统公司的PSoC的核心是一个8位微处理器,但事实上,它很少被称为“微控制器”,而是被称作一个具有嵌入式微控制器内核的混合信号阵列。

正像这种描述性更强的名称所暗示的那样,PSoC是一种对于标准的“全数字式”微控制器设计、纯粹的模拟设计以及介乎此二者之间的所有设计而言具有同等的上佳适用性的器件。

如果想了解PSoC,那么首先必须搞清一个新的概念。这种新概念指的就是被称为“用户模块”的通用且可配置的模拟、数字和混合信号积木式部件的概念。用户模块的主要任务就是向设计师提供几组能够由其进行配置和互连的通用积木式部件,以便执行多种功能。

对于大多数设计师来说,复合可编程逻辑器件(CPLD)的“宏单元”是他们所熟悉的对用户模块最为贴近的类比。每个单元(同样,每个用户模块)都是根据核心功能来构筑的,当对其进行配置时,就会产生定制功能或板载外围元件的最终结果。

PSoC包括多种用户模块,与CPLD的宏单元非常相似,这些用户模块也可由设计师随意配置。不过,需要牢记的是:与CPLD不同,PSoC还包括能够完全以模拟方式(无需使用数字电路或CPU等等)来处理信号的用户模块。

事实上,当采用PSoC时,实际上能够创建一个“纯模拟型”的设计方案,在这种方案中,CPU内核除了按设计师的规定在上电期间执行配置代码以外根本不运行!此外,PSoC Designer开发工具还能够自动生成该配置的全部代码 …… 后文将对此做更加详细的阐述。

你可能对此感惊讶。如果你驻足思考一下你所做过的许多设计,就有可能意识到有一些关键的“积木式部件”是你曾经反复使用过的。赛普拉斯微系统公司的芯片设计人员也认识到了这一点。正是这种领悟导致了上述用户模块的开发成功。

为了提供最大的灵活性并满足大多数应用的需要,人们意识到有些基本积木式部件将是必须的,即:

(1) 一个8位CPU内核。

(2) 通用型数字用户模块。

(3) 具有通信能力的通用型数字用户模块。

(4) 模拟连续时间用户模块。

(5) 模拟开关电容器用户模块。

(6) 确定各种信号输入和输出器件的线路的能力。

上面的“核心”功能列表形成了构筑PSoC器件系列的基本平台。为了使该器件具有最大的灵活性和能力,许多附加部件也被融入其中。图1示出了包含所有子系统的现行PSoC器件的方框图。

由图1可见,PSoC包括了大多数“纯数字型”微控制器的全部标准外围元件以及众多的新型部件和创新部件。

图1,PSoC的内部结构

数字模块

显而易见,列表的第一项——8位CPU内核是必不可少的。目前的PSoC系列的核心基于赛普拉斯半导体公司从其名为M8的USB控制器系列派生而来的成熟内核。这种哈佛(Harvard)架构内核能够在24MHz的频率下具有高达4MIPS的操作性能,并满足了非常苛刻的USB睡眠功耗规范要求。该器件具有一个具有全面可编程性的内部CPU时钟,甚至在正常操作期间也可对其加以改变。这意味着该PSoC能够实现一个全混合信号设计,而无需任何的外部元件(当然,电源除外)。

为了使该内核在PSoC中具有更高的能力,还增加了一些新型部件。这些部件包括一个硬件乘法-累加寄存器(MAC)、能够被分割并用作嵌入式EEPROM的FLASH代码空间、板载低电压检测以及嵌入式睡眠定时器等等。

该PSoC的CPU内核允许对所有由用户模块配置组成的特殊功能寄存器进行存取操作。在这种场合,该内核还支持一种名为“动态重构”的概念。这一能力使得PSoC能够在固件的控制之下对其所有的用户模块进行全面重构,并由此获得一个全新的“个性”和功能。(参见附文《定义个性化的的动态重构功能》)

我们给出的积木式部件列表的第二项和第三项形成了数字用户模块组的基础。这些用户模块是通用型数字功能部件,它们支持面向各种“数字”板载外围器件(包括计数器、定时器、脉宽调制器、UART、SPI、IrDA和CRC功能元件)的配置。

模拟功能

提到我们列表中的第四项(模拟连续时间用户模块),目前我们已经拥有了一个用于形成纯模拟连续时间积木式部件(比如:可编程增益放大器、模拟比较器、差分放大器和滤波器等不一而足)的框架。这些部件能够在无需CPU等的参与的情况下运行(只需在上电时进行初始化),并可在某些形式的“睡眠”或CPU暂停操作的条件下继续运行。

图2示出了PSoC的模拟连续时间用户模块的内部布线能力。

图2,PSoC模拟连续时间用户模块

尽管我们列表中和第一项至第四项对大多数设计师而言都比较熟悉,但第五项“开关电容器用户模块”恐怕就要稍显陌生了。在讨论开关电容器用户模块之前,有必要了解有关PSoC的一个重要事项,这就是第六项所提到的:该PSoC不仅包括上述的所有积木式部件,还包括用于对这些积木式部件进行内部互连、将外部信号输入以及将内部信号输出所必需的全部路由选择资源。模拟信号传送路径也包括在内。

评论