可控数字语音延迟器的PIC设计

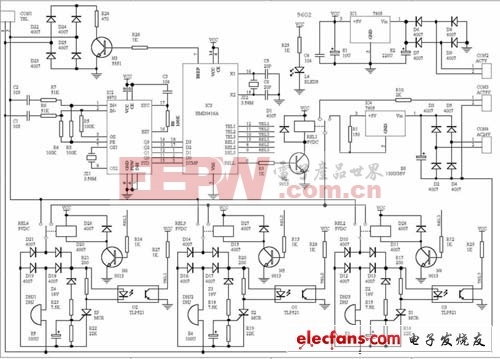

摘要:详细阐述一种采用PIC16C55单片机实现可控数字语音延迟器的设计方案,同时提供控制电路图及软件算法流程图。

关键词:延迟器 语音信号 PIC单片机

延迟器在音频信号处理中有着重要而特殊的用途,是制造混响器、回声信号的重要部件,在无线通信同步控制中也起着重要作用。延迟器大致可分为BBD (Bucket Brigade Device)式延迟器和数字式延迟器两类。数字式延迟器与BBD式延迟器相比,具有延时时间范围宽,工作频带宽,动态范围大等特点;而可控式延迟器可以灵活产生多种时延,以便应用于不同的场合。本文介绍一种基于PIC系列单片机的可控数字语音延迟器的设计方案。

本系统采用性价比极高的PIC16C55单片机作为中心控制部件。PID16C55单片机是PIC系列单片机中的低档型单片机,具有20个I/O,1个定时器和1个WDT,其最短指令周期可达200ns。利用该型号单片机作为控制部件,具有控制快速、扩展方便、低功耗、性能稳定等特点,同时还可以最大限度地减少外围电路以降低成本,提高性价比。

1 系统工作原理

可控数字语音延迟器的原理框图如图1所示。输入的语音信号先经过低通抗混迭滤波器,滤除其中的高频成分后送入A/D转换器。经过A/D转换后,信号变成数字信号。该数字信号在PIC16C55单片机的控制下被写入存储器。系统中高有两组存储器,这两组存储器在单片机的控制下交替工作:在一个延迟周期内,一组存储器专门用于存储本周期内采集的数据,而另一组存储器专门用于把上一个周期所采集的数据按顺序送到数据总线,经过D/A转换器和低通滤波器后恢复出原始信号。在下一个延迟周期,两组存储器交换工作状态,以后按此不断循环。可见,延迟的时间取决于A/D转换器前后两次启动的时间间隔和存储区的大小。在本系统中,利用PIC16C55中的定时器定时产生A/D转换器的启动信号,定时器的定时时间为10μs,所以,最小延迟时间为10μs。而存储区的大小设为256,所以,最大延迟时间为10μs

评论