ADSP-TS201的系统设计及外部总线接口技术

随着雷达技术发展,大带宽高分辨力、多种信号处理方式的采用,使得实时信号处理对数据的处理速度大大提高。同时在雷达信号处理中运算量大,数据吞吐量急剧上升,对数据处理的要求不断提高。随着大规模集成电路技术的发展,作为数字信号处理的核心数字信号处理器(DSP)得到了快速的发展和应用。ADSP-TS201DSP是美国模拟器件(ADD公司继TSl01之后推出的一款高性能处理器。此系列DSP性价比很高,兼有FPGA和ASIC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理和图像处理。如雷达信号处理、无线基站、图像音频处理等。

2 ADSP-TS201简介

ADSP-TS201采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式系统。其性能如下:

(1)最高工作主频可达600 MHz,指令周期为1.67 ns。支持单指令多数据(SIMD)操作。

(2)支持IEEE32位、40位浮点数据格式和8位、16位、32位和64位定点数据格式。

(3)4条128位的数据总线与6个4 Mb的内部RAM相连。

(4)32位的地址总线提供4 G的统一寻址空间。

(5)对与多片处理器的无缝互连提供片上仲裁。

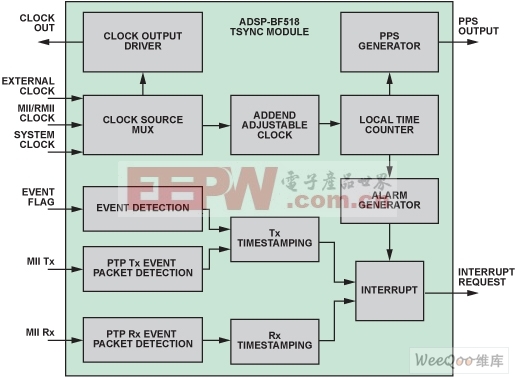

ADSP-TS201处理器由处理器核和IO接口两部分组成,结构框图如图l所示。其中处理器核由两个计算块、两个整型算术逻辑单元、程序控制器组成。IO接口由内部存储器、外部设备接口、14通道的DMA控制器、全双工的LVDS链路口、IEEEll49.1JTAG接口组成。内部存储器为24 Mb DRAM,外部设备接口包括SDRAM控制器、EPROM接口、主机接口、多处理器接口。

3 系统设计

应用ADSP-TS201进行系统设计时,有一些特别需要注意的地方,如:电源设计、时钟设计、JTAG接口、未使用的管脚如何处理等。下面就这几个方面分别进行讨论。

3.1 电源设计

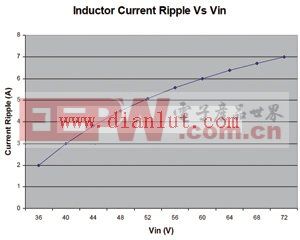

ADSP-TS201处理器共有4组电源,分别是核电源(VDD)、模拟PLL 电源(Vm-1)、内部DRAM电源(VDD-DRAM)、IO电源(VDD-K),并且在不同的工作频率下供电要求不同。以600 MHz为例,电源工作参数如表1所示。因此设计电源的时候要选择符合电压电流要求的电源。

ADSP-TS201在上电的时候有上电顺序的要求,这点在电源设计的时候必须考虑到。其上电顺序如图2所不,要求tVDD_ DRAM大于O ms,保证DRAM的上电在最后,而且上电时间也要有所保证。所以在选取电源芯片时应该选择带有关断功能的芯片,如MAX8869等。在电源芯片的SHUTDOWN管脚接一个电容到地,利用电容的充放电作用,在上电开始使能SHUTDOWN管脚,使电源芯片处于关断状态。随着电容充电至电源电压,SHUTDOWN为高电平,此时电源芯片开始工作,输出1.6 V的电压,为DRAM供电。

另外ADSP-TS201电源管脚需要旁路电容去耦。在PCB设计时旁路电容的顺序分别是:VDD A到VSS的旁路电容;VDD到VSS的旁路电容;VDD-DRAM到VSS的旁路电容; VDD-IO到VSS的旁路电容。

3.2 时钟设计

ADSP-TS201有2个时钟参考电压管脚,SCLK_VREFl和SCLK_ VREF2,这两个管脚应该连在一起,为系统时钟供电电压的一半。SCLKl和SCLK2是时钟输入端,最大系统时钟是核时钟的1/4。同时SCLK也为外部接口总线提供时钟。ADSP一TS201内部有一个PLL,通过设置SCLKRATE2~0引脚将SCLK倍频到所需的核时钟。在设计过程中,为了保证时钟的同步,可以采用时钟驱动芯片,可以同时输出多路时钟,为TS201 SDRAM提供系统时钟。

3.3 JTAG接口

ADSP-TS201 JTAG仿真器是一个14脚的母头,第3脚是没有任何连接的。在调试过程中第3脚必须拔出来。在JTAG接口设计时要注意以下方面:正确的上下拉电阻,数据(TDI,TMS,TDO,TRST,EMU)驱动、时钟驱动如74系列的驱动芯片。

3.4 未使用管脚的处理

ADSP-TS201包含有3个NC管脚,在设计中不要有任何连接。对于没有用到的管脚,应根据是单片系统还是多片互连系统进行处理,可以悬空的管脚悬空,不能悬空的管脚一定要接上拉电阻或者下拉电阻。特别是没有用到的链路口的输入管脚的处理,主要参考ADI网站中所给出的数据手册。

另外TS201支持多片DSP互连,最多可达8片。通过链路口完成片与片之间的通信,电路连接简单。

4 外部总线接口技术

ADSP-TS201外部总线支持各种不同的通用/专用协议,并且可以通过编程进行配置。外部总线接口支持流水线协议,SDRAM协议和慢速设备协议。TS20l可以采用流水线协议访问存储系统,数据传送速度非常快。另外TS20l有片上的SDRAM控制器,支持SDRAM协议。以下就是这两种协议的应用。

4.1 SDRAM接口

ADSP-TS201处理器有一个专用的SDRAM接口.可以实现与标准SDRAM 6 Mb,64 Mb,128 Mb.256 Mb.512 Mb的无缝连接。支持1 024-,512-,256字的页面长度,通过对SDRCON寄存器的编程可实现页面长度的选择。同时SDRAM占用TS201的外部存储空间地址,通过设置/MSSD3~0来确定SDRAM的地址空间范围。

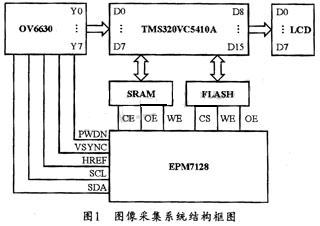

本设计选用的SDRAM是HY57V561620B,页面长度为512字,将两片SDRAM拼接成32位的总线宽度,实现与TS201的无缝接口。根据不同的总线宽度,TS201的地址总线与SDRAM的连接有所不同。

(1)对于32位数据总线其连接方式如下:

SDRAM地址Bit9~0与TS201 ADDR9~0相连;

SD

SDRAM地址Bitl5~11与TS201 ADDRl5~11相连。

(2)对于64位数据总线,连接方式如下:

SDRAM地址Bit9~0与TS201 ADDRl0~1相连,TS201 ADDR0悬空;

SDRAM地址Bitl0与TS201的SDAl0管脚相连;

SDRAM地址Bitl4~11与TS201 ADDRl5~12相连。

另外对于标准的SDRAM(3.3 V),TS201的地址线ADDRl5∽11都可以作为BANK的选择线。对于低功率的SDRAM(2.5 V),只有ADDRl5~14可以作为BANK的选择线。因此在进行接VI设计时一定要注意所选择SDRAM的电参数。

4.2 ADSP-T$201与FPGA接口

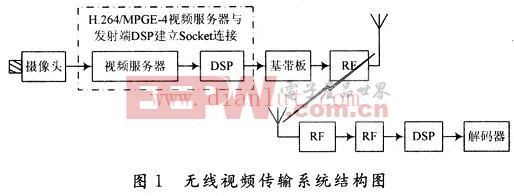

本文设计的系统需要将FPGA连接在TS201的外部总线上,采用DMA中断,通过总线的方式从FPGA的外挂RAM(乒乓存储)中读取数字下变频后的I,Q两路数据,其连接方式如图3所示。

其中MS0,MS1是片选信号,RD和WRL分别是读和写信号。在一个PRF周期内FPGA进行数字下变频,将I,Q数据存储到SRAM中,然后向 TS201发出DMA请求,TS201将SRAM的数据采用流水线协议通过总线读入片内RAM中,进行后续的处理。再将处理完的数据以总线方式写入到FPGA内部RAM中,以便进行在线仿真或者进行后续的输出。

5结 语

本文主要结合ADI公司的高性能ADSP-TS201的结构特点,讨论了在系统设计的过程中应该重点注意的几个问题和ADSP-TS201的外部接口技术,并给出了其与SDRAM,FPGA的连接实例,对基于TigerSHARC系列DSP的应用设计具有实用的参考价值。

评论