ADSP-TS101S的自动引导方式分析与设计实现

摘 要:本文详细分析了美国ADI公司最新推出的TigerSHARC系列数字信号处理器ADSP-TS101S的引导方式,并在最后给出了已成功实现的、基于该DSP处理器的某雷达信号处理机的自动引导设计方案。

关键词:ADSP-TS101S;引导方式;VisualDSP++;EPROM引导

ADSP-TS101S数字信号处理器简介

ADSP-TS101S数字信号处理器是美国ADI公司推出的TigerSHARC系列中一款具有极高性能的静态超标量处理器,其专为大信号处理任务和通信应用进行了结构上的优化。该处理器具有非常宽的存储器带宽和双运算模块(支持32bit浮点和8、16、32、64bit定点处理),其芯片内部的时钟频率最快可以达到300M。静态超标量结构使ADSP-TS101S每周期能够执行多达4条指令、24个16bit定点运算或6个浮点运算。芯片内部有三条相互独立的128bit宽的数据总线,每条连接三个2M bit内部存储器bank中的一个,总共提供了12Gbytes/s的内部存储器带宽。

自动引导方式分析

ADSP-TS101S的引导方式由复位时 管脚的电平高低决定。在复位时,为输入管脚,如果其电平为低,则设置为EPROM引导方式。对于这种方式,在信号无效后,信号就成为输出信号,作为EPROM的片选信号;如果其为高,ADSP-TS101S将处于空闲(IDLE)状态,等待外部主机或链路口来引导。总的来说,ADSP-TS101S有四种引导方式,其详细描述如下:

从EPROM引导:ADSP-TS101S被自动配置为通过外部端口,利用DMA通道0,从片外8位EPROM装载32bit的程序到片内存储器的0x00~0xFF,并将byte型数据自动打包成32bit指令,DMA传送完成的中断向量在复位后被初始化为0x00000000。EPROM存储器空间没有被映射到DSP的统一存储空间,即引导完成后,就与整个系统无关。其寻址空间被限定为最大16Mbytes。

从外部主设备(主机或另一个ADSP-TS101S)引导:任何共享簇总线上的主设备都能够通过外部端口,通过写它的内部存储器或自动DMA的方式引导ADSP-TS101S。

从链路口引导:ADSP-TS101S的四个接收链路的DMA在复位后均被自动配置为接收32bit到内部存储器的0x00~0xFF,相应的DMA传送完成的中断向量在复位后也被初始化为0x00000000。

无引导:ADSP-TS101S在复位后,自动从存储空间的某个地方开始执行。这是通过在复位后使能中断请求信号 来实现DSP启动的。

自动引导的软件设计

从软件角度看,所谓复位引导从某种意义上说就是在系统上电后,将生成的可执行文件的代码和数据按照对系统存储空间的分配装载到指定的地方,并接着依据规定的顺序来执行程序。

自动引导的软件设计思路

为了设计这一软件,首先必须了解ADSP-TS101S的软件设计流程。其流程图一般如图1所示。

其中,链接描述文件(.LDF)定义了整个系统的存储器配置和程序中数据及代码的具体存放位置。加载核文件(.DXE)是指加载引导核程序,其大小为32bit,放在加载文件的起始部分,其功能是用来实现ADSP-TS101S的正确引导。在VisualDSP++安装目录的ldr子目录下,ADI公司提供了标准加载核文件及相应的源程序(.ASM)和链接描述文件。一般可直接使用提供的标准加载核文件或对其相应的源程序进行简单修改,重新编译链接生成所需的加载核文件。加载文件是由引导加载器(elfloader)将可执行文件进行一定的格式变化,并在起始位置附加上加载核文件生成的。加载文件可以进一步通过仿真器和JTAG口在线烧写到Flash存储器中。加载文件被分成几段,依据类型不同可以分为:0-最终初始化段(Final Init);1-非零初始化段(None-zero Init);2-零初始化段(zero-Init)。另外ID号决定该段内容是哪一个处理器的,COUNT为该段内容以32bit字来计数的大小。

由于ADSP-TS101S有三种引导方式(不考虑无引导方式),ADI公司相应的提供了三种不同的加载核文件,分别为:TS101_prom.dxe、TS101_link.dxe、TS101_host.dxe。三个程序的核心思想和功能完全一致,只是由于使用的加载端口和方式的不同,在具体代码实现上稍有差异。

综合以上的分析可以看出:ADSP-TS101S的复位引导从本质说包括两个方面:其一,在生成加载文件时,在起始部分额外增加256字的加载核文件;其二,在复位结束后,按照设定的引导方式不同,自动从相应接口接收256字的代码(实际就是加载核文件)到内部存储空间的0x00~0xFF,并在完成这一接收过程后,从内部存储空间的0x00000000开始执行程序(实际就是执行加载核文件),最终是由加载核文件来完成整个可执行程序的加载。需要注意的是,加载核文件并不会永远占据内部存储空间的0x00~0xFF,因为加载核文件执行到最后会自动完成自身的覆盖。

下面以EPROM引导为例,来简要分析标准加载核程序(TS101_ prom.dxe)是如何具体实现可执行程序的加载的。

标准EPROM引导加载核程序分析

如前所述,复位后ADSP-TS101S自动从DMA通道0接收256字的内容到内部存储空间,该传送完成后,相应的中断将把ADSP-TS101S从空闲状态唤醒,接着ADSP-TS101S从0x00000000开始执行程序(即执行加载核程序)。在加载核程序中,DMA通道0被配置为从EPROM的地址0x0400 (0x0000~0x03FF为加载核程序,对应于ADSP-TS101S内部存储空间的256个字,向ADSP-TS101S的内部存储空间加载程序。具体包括以下几个步骤:

(1)从ADSP-TS101S的SYSTAT中获得处理器的ID,并放到XR10寄存器中。

(2)首先,利用DMA通道0从EPROM的0x0400传送8B的数据到ADSP-TS101S的内部存储空间0x00000000~0x00000001,即Data header for processor 0,从中分析出该段程序的处理器ID,并与XR10进行比较。若一致则转入(3),否则,跳过该段程序。

(3)分析该段程序的类型和大小。依据不同的类别分别将规定大小的代码或数据加载到指定的地址。其中,“Final Init”段将把加载核程序占据的内存空间覆盖掉。

(4)最终引导完成后,ADSP-TS101S的存储空间内容与用链接描述文件对可执行文件内容的分配完全一样,ADSP-TS101S从内部存储空间0x00000000开始执行程序。

某雷达信号处理机的复位引导设计方案

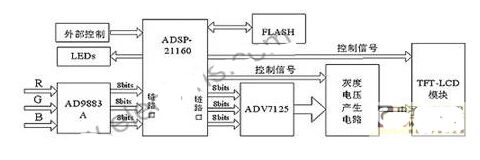

虽然ADI公司的ADSP-TS101S是性能较高的浮点信号处理器,其做1024点32bit浮点FFT(基2)仅需39.34ms(250M主频),但在设计某雷达信号处理机时,由于运算量巨大,经过分析,设计了一个以3片ADSP-TS101S为核心的信号处理机。三片ADSP-TS101S的连接关系如图2所示。

三片ADSP-TS101S要运行的程序最终放在一个Flash存储器中,其中TS1和TS2的加载程序以数组形式放在TS3的程序中。TS3设计为EPROM引导方式,TS1和TS2设计为链路口引导方式。系统上电后,TS3从Flash加载程序,TS3加载完成后,再通过链路口加载TS1和TS2。加载完成后,三片ADSP-TS101S都正常执行各自的程序。

结合以上各部分的分析,可以看出要实现该信号处理机中三片ADSP-TS101S的正确引导,所需的工作由以下几步组成:

(1)由第一片ADSP-TS101S要执行的程序(TS1.dxe),结合链路口的加载核程序生成第一片ADSP-TS101S的加载文件(TS3_1.ldr)。需要注意的是:该链路口加载核程序不能直接使用提供的标准链路口加载程序,必须将提供的链路口加载核源程序(TS101_link.asm)中的LINK常数改为2(#define LINK 2),即第一片ADSP-TS101S由链路口2引导。

(2)与(1)类似,生成第二片ADSP-TS101S的加载文件(TS3_2.ldr),只是需要把链路口加载核源程序(TS101_ link.asm)中的LINK常数改为0(#define LINK 0),即第二片ADSP-TS101S由链路口0引导。

(3)将TS3_1.ldr和TS3_2.ldr以数组的形式放在TS3的源程序(TS3.asm)中,其形式如下所示:(.var ts1[ ]={"ts1.ldr"}; .var ts2[ ]={"ts2.ldr"};),编译链接生成TS3的可执行程序(TS3.dxe),然后结合EPROM加载核程序生成第三片ADSP-TS101S的加载文件(TS3.ldr)。在此,可以使用ADI公司提供的标准EPROM加载核程序。另外,还需在TS3的源程序中(TS3.asm)开头加入对TS1和TS2的引导代码,其核心就是分别通过TS3的链路口0和链路口1将数组ts1和ts2以DMA方式传送给TS1和TS2。

(4)参考ADSP-TS101S开发板的Flash烧写程序,设计烧写系统所用Flash的程序,然后通过JTAG口将TS3.ldr烧写到系统的Flash存储器中,从而完成了整个过程。

结语

如果在系统中没有使用SDRAM,则只需对ADI提供的标准加载核源程序进行少量修改,重新编译链接即可使用;如果系统中有SDRAM,则还需在标准加载核源程序的起始处加入对SDRAM的初始化程序。但总的看来,如果清楚了ADSP-TS101S的复位引导过程,用户就可以在VisualDSP++集成开发环境中轻松完成整个ADSP-TS101S的复位引导。■

参考文献

1 ADSP-TS101 TigerSHARC Processor Hardware Reference.Analog Devices, Inc

2 VisualDSP++ C/C++ Compiler and Library Manuals for TigerSHARC DSPs.Analog Devices, Inc

3 苏涛,吴顺君,寥晓裙. 高性能数字信号处理器与高速实时信号处理. 西安,西安电子科技大学出版社

4 ADSP-TS101 TigerSHARC Processor Boot Loader Kernel Operation. EE-174.Analog Devices, Inc

c++相关文章:c++教程

存储器相关文章:存储器原理

评论