基于多通道缓冲串口的虚拟I2C总线

电子设计应用2004年第9期

本文引用地址:https://www.eepw.com.cn/article/3590.htm摘 要:本文提出一种用多通道缓冲串口(McBSP)完成I2C总线的虚拟方法,该方法简单可行、硬件成本低,并给出了该方法在智能交通控制系统(ITS)中的应用。

关键词:I2C;McBSP;ITS

引言

很多器件都具有I2C总线,如串行EPROM、ADC等。另外,也已有很多外围器件支持与I2C总线的接口,但不直接支持I2C总线,如多数MCU、DSP等,因而采用I/O口线虚拟I2C的方式成为一种通用解决方案。但大多数DSP器件直接支持的I/O口线较少,不能进行直接的位操作,所以如何用DSP进行I2C总线的虚拟是本文所要讨论的问题。通过使用高端DSP器件中都具有的McBSP成功地进行了虚拟I2C总线的实现,并在一个ITS系统的控制模块中得到应用。

I2C总线的数据传送规范

I2C总线由串行数据线(SDA)和串行时钟线(SCL)组成。通信时,所有具备I2C总线接口的器件都连接到这两根线上,而且既可以发送数据也可以接收数据,但任意时刻只能有一个主控器件进行I2C总线的控制,其他器件都为被控器件,它们分时占用总线。

I2C总线的数据传送由主器件控制。首先由主器件发出开始信号S,表示开始启动数据传输。当SCL为高电平时,如果出现SDA的电平由高变低则视为S信号,然后主器件发送从器件的7位地址和读写位R/W,接着主器件将接收从器件的应答信号,如果收到正确的ACK,则进行数据的传送。数据传送的方向由读写位R/W的值确定 ,而且数据传送为8位,高位在前,低位在后。不管是发送数据还是接收数据,在传送完8位数据后,必须由接收数据的器件在SDA上发一个应答信号。最后当全部数据传送完后,由主器件产生停止信号P,表示总线传送结束。SCL线为高,SDA线由低电平变高电平时,视为停止信号P。由上可知,I2C总线数据传输采用了应答式的工作方式:即发送方发送数据后由接收方发送是否正确接收的应答信号,发送方以此作为是否继续进行数据传送的判断依据。

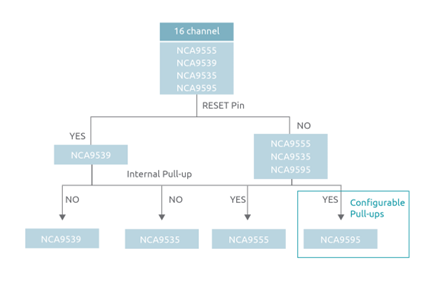

图1 主器件数据发送流程

用McBSP虚拟I2C总线的实现

从前面的分析可以看出,I2C总线的数据传输主要是由主控器件控制,在SCL的控制下,按位传送数据,也就是说,要想完成对I2C总线的虚拟主要是完成主控器件I2C的实现。下面讨论将TMS320C5410(以下简称5410)器件的McBSP配置为通用I/O口来虚拟I2C总线的实现方法。

McBSP配置为通用I/O口

作为主器件的I2C总线的两条信号线中,SCL总是作为输出,SDA根据需要配置成双向的I/O口,考虑到虚拟总线的数据线方向,本文用McBSP的FSX和CLKX两个信号线分别来虚拟I2C的SCL和SDA,其中FSX由于要作为SCL输出引脚,配置为GPO,CLKX模拟SDA信号线,由于SDA信号线为双向数据线,所以将CLKX配置为GPIO。McBSP配置为通用I/O口,主要涉及到McBSP的控制寄存器SPCR1、SPCR2和引脚控制寄存器PCR的设置。 PCR控制寄存器主要涉及到通用I/O口的方向控制,输入/输出的读写等,其中所涉及到的控制位如下:CLKXM、FSXM控制CLKX和FSX的通用I/O口的方向。由于FSX总是作为输出,所以FSXM=1;CLKX的方向设置,当作为虚拟SDA的输出时,CLKXM=1,反之CLKXM=0;CLKXP、FSXP控制通用I/O的输入/输出电平值,当要往输出I/O口送值时,它们作为输出位寄存器,直接将要输出的电平值写入对应的位中。当作为输入I/O时,CLXP和FSXP里的值就反映了输入引脚当前的电平状态。

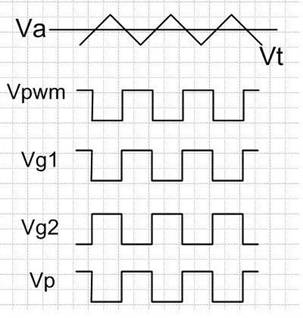

图2 启动信号S的时序要求

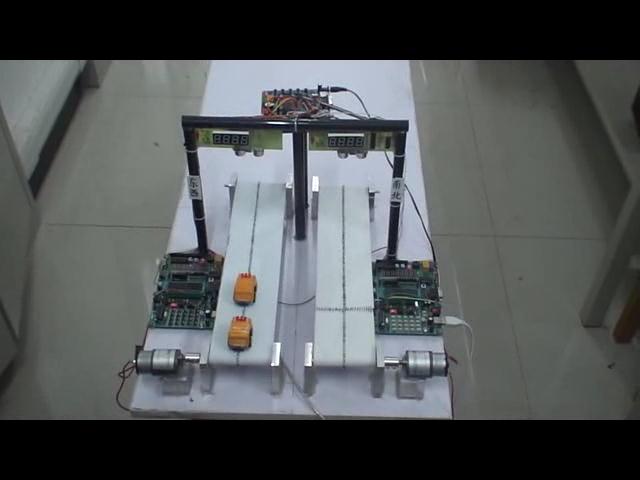

图3 虚拟I2C总线应用实例图

McBSP虚拟I2C总线的软件模块实现

首先将McBSP配置为通用I/O口使用,必须禁用其缓冲串口的功能、开启通用I/O使能,所以将SPCR2控制寄存器中的XRST置0,将PCR控制寄存器中的XIOEN置1。

要实现I2C总线的数据传输,以主器件向从器件发送N字节数据为例,其通信流程如图1所示, 一般需要包括以下几个子程序模块:

a. 启动位S和停止位P的发送

b. 从器件应答位ACK的判断

c. 字节数据(或地址)的发送

下面给出启动位S发送子模块的部分程序源码,其它子程序模块可以参照此程序修改。

启动位S发送子程序:

STM MCBSP_PCR_SUB_ ADDR,MCBSP0_SPSA

; 选择PCR寄存器

LD #2a00h,A

STLM A,MCBSP0_SPSD

; 设置CLKX为输出口

CALL XDELAY

LD #2a00h,A

ST #0002H,*AR3

OR *AR3,A

STLM A,MCBSP0_SPSD

; 置PCR中的CLKP位为1,引脚CLKX-SDA为高电平

ST #0008H,*AR3

LD #2a00h,A

OR *AR3,A

STLM A,MCBSP0_SPSD

; 置PCR中的FSXP位为1,引脚FSX-SCLK为高电平

call delay_prg1

;延时子程序delay_prg1

ST #0FFFDH,*AR3

AND *AR3,A

STLM A,MCBSP0_SPSD

; 置PCR中的CLKP位为0,引脚CLKX-SDA为低电平

call delay_prg2

;延时子程序delay_prg2

ST #0FFF7H,*AR3

AND *AR3,A

STLM A,MCBSP0_SPSD

; 置PCR中的FSXP位为1,引脚FSX-SCLK为高电平

RET

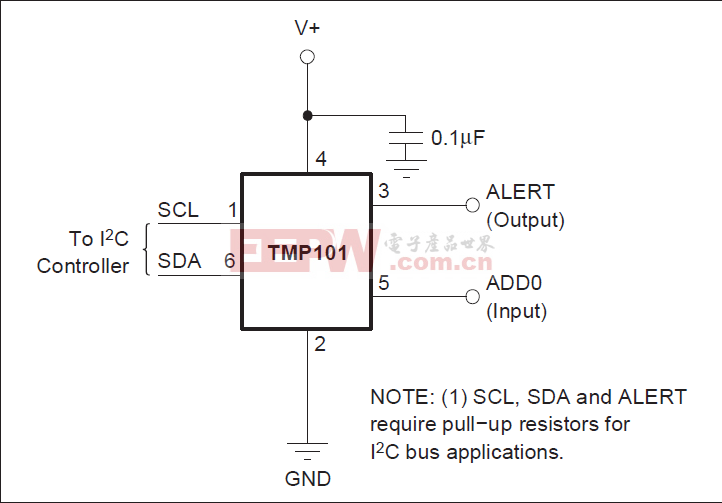

需要注意的是,I2C总线协议对信号的时序要求有严格的规定,如对启动信号S的时序要求如图2所示。即要求SDA信号在由高电平向低电平跳变时保持高电平时间至少为4.7ms,SCL信号在SDA信号由高电平向低电平跳变后必须保持高电平时间至少为4.0ms。启动位S发送子模块的源代码中的延时子程序delay_prg1、delay_prg2就是为了满足对启动位S的时序要求。假设DSP器件的内部时钟频率为100MHz,则其单指令周期为0.01ms,就可以根据延时时序参数的要求计算出所需要的指令周期数。显然子程序delay_prg1至少需要470个指令周期,delay_prg2则至少需要400个指令周期。

应用实例

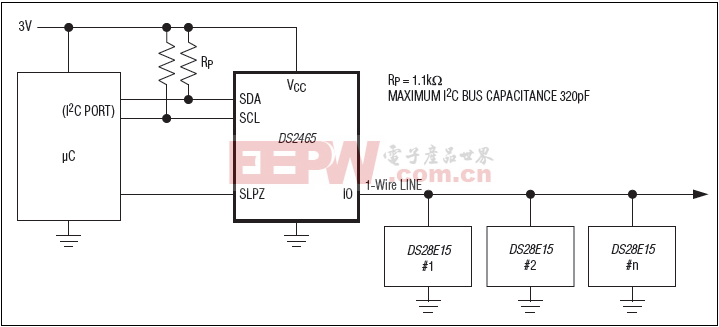

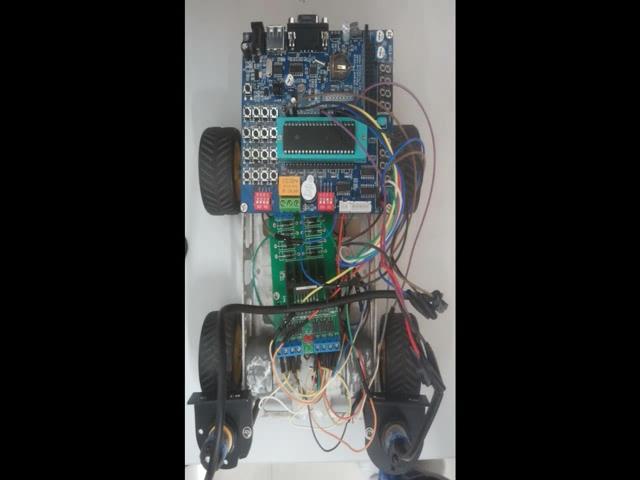

在智能交通控制系统中用5410的0号缓冲串口实现了虚拟I2C总线,系统的硬件原理如图3所示。系统由设置在某交通路口的摄像机提供交通视频信号,由PHILIPS专用视频采集芯片SAA7111完成图像的实时采集,然后将8bit的图像数据送至SRAM中缓存,并由DSP器件完成图像处理算法,提取出相应的交通参数。SAA7111完成图像采集首先必需通过I2C总线接口进行器件内部一些控制寄存器的初始化设置,由于5410器件没有专用的I2C总线接口,所以采用5410的McBSP0的FSX和CLKX引脚分别来虚拟I2C的SCL和SDA,实现了对SAA7111的初始化配置。

SAA7111控制寄存器初始化配置的过程就是DSP主器件向SAA7111从器件中的控制寄存器写配置数据的过程。SAA7111中涉及到的控制寄存器由00h~1Fh的寄存器基地址寻址,主器件发送配置数据的过程如表1所示。

采用这种方式对00h~1Fh的寄存器寻址时,必须向SAA7111分别传送这些地址字节,这个过程是非常繁琐的。I2C总线接口的外围器件中,如出现这种器件内部需要寻址多个地址空间时,总线数据的读写操作具有地址自动加一的功能,这样就简化了I2C总线的外部寻址,这种寻址方式下的主器件控制数据写流程如表2所示。

结语

本文采用DSP的McBSP来虚拟I2C总线接口,先将McBSP配置为通用I/O口,再对这些通用I/O口进行I2C总线数据传输的位操作,解决了DSP器件无法方便地进行位操作的问题,硬件接口简单,调试方便,并且可以节省硬件的花费,此方法已经应用于ITS系统中,方法可行,并运行可靠,为相关问题的解决作出了成功的尝试。■

参考文献

1 The I2C-Bus Specification, Philips Semiconductors, Version 2.1 January 2000

2 何立民, 周立功. I2C总线的串行扩充技术. 周立功单片机,2000,9

3 戴明桢,周建江. TMS32C54X DSP结构原理及应用. 北京航空航天出版社,2001,11

4 TMS320C54X DSP Reference Set Volume5: Enhanced Peripherals, Texas Instruments, SPRU302:June 1999

评论