挑战铜线互连极限 PCIe 4.0还要等两年

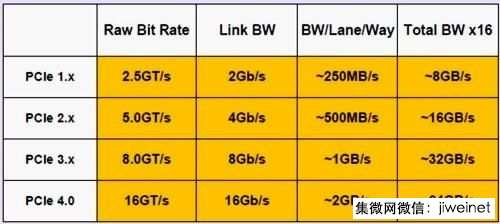

开发PCI Express (PCIe) 4.0互连介面规格的工程师们,已经在实验室里将其传输速度推到了16 GT/s (GTransfers/second);但遗憾的是,此恐怕会是铜线互连规格最后一次大跃进的新规格,最终版本恐怕在2017年初之前难以出世。

本文引用地址:https://www.eepw.com.cn/article/276261.htm负责开发最新PCI Express规格的PCI SIG预期,0.7版的PCIe 4.0可在今年底完成,但届时该技术并不会有太大的变化。而在PCIe 4.0正式公布之前,包括Cadence与Synopsys等厂商,都将于近日举行的年度PCI SIG大会上发表PCIe 4.0的PHY与控制器功能区块IP。

在PCIe 4.0新标准问世之前,重要的工作包括对该互连技术进行微调,以及取得工程师们对新规格参数的共识;这些步骤非常重要,因为要在较短的传输距离达到更高的速度,会为某些系统,例如大量使用PCIe介面的伺服器,带来需添加重定时器(retimer)的成本。

4.0 版本的PCIe规格可能会比以往的版本花更长时间才能完成开发,这是因为PCI SIG选择将铜线互连的能力发挥到极限、最大化资料传输速率,目标是达到上一代PCIe 3.0的两倍。PCI SIG主席Al Yanes接受EE Times美国版访问时表示:“我们正达到16G的速率;这在几年前我们还认为是不可能的。”

“基本传输距离仍有待验证,但原则上是7寸左右;”领导PCI SIG多年的Yanes指出:“较长的传输距离是15寸左右,以两个连接器搭配重定时器。PCIe 3.0也采用重定时器,现在我们需要采用该装置以缩短长通道。”

4.0版本的PCIe规格会是最后一代的铜线互连规格,其速率将加倍

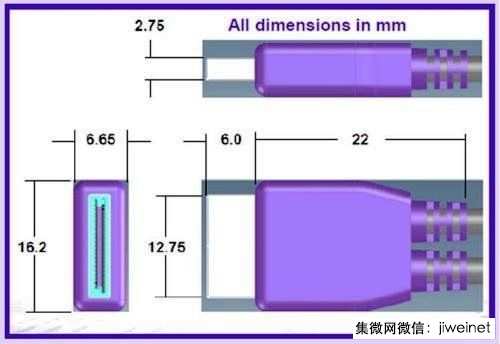

PCIe 4.0将采用新型连接器,但该标准将可在机构与电气规格上向后相容目前的8GT PCIe 3.0。Yanes表示:“我们已经针对连接器做了很多分析,尝试过各种可能的方案;我们的电气工作小组有一些顶尖工程师,他们在其中大显身手──我们很 兴奋地看到有大量的活动以及产业界的参与。”

迈向光学互连的未来

在2017年之后,我们可以很轻易地推断,届时工程师们若要将处理器性能推至极限,会需要光学连结技术;在过去20年来,已经有一些光学板卡以及晶片互连技术的研发,但到目前为止,铜线仍能支援所需的资料速率,而且成本比任一种光学互连方案都低。

对 此Yanes表示:“我相信工程师们会在需要的时候,找到具成本效益的(光学互连)方案──其实早在四年前产业界就积极推动光学互连规格。”不过目前 PCI SIG还没有着手进行光学互连规格的开发;考量到时间表,也有可能会有其他替代方案冒出头来,例如研究人员已经在利用各种形式的电容或电感耦合技术之无线 晶片对晶片互连技术开发上有不错进展。

有鉴于要达到高传输速率所面临的各种挑战,新版本PCIe规格进展脚步较慢是可预期的;再加上对PCIe需求量最大的PC产业领域目前处于低迷状态,也不再积极追逐更快的速度、更高的性能。Yanes表示:“现在更受瞩目的议题是低功耗。”

而PCI SIG也针对PCIe在行动装置的应用,开发一系列相关规格与技术,其中包括PCIe 4.0中对四分之一电压摆动状态(quarter-swing states)的支援;其功耗从PCIe 1.0所支援的半电压摆动(half swings)之400mW,进一步降低至200mW。

此 外PCI SIG预定在今年秋天发表1.0版的OcuLink──采用4个PCIe 3.0 8GT/s连结的PCIe缆线版规格;该规格被视为苹果(Apple)与英特尔(Intel)共同开发之Lightning互连介面之替代方案。但 OcuLink是否能在随处可见的USB与新兴Lightning互连介面环伺的市场上,找到可立足之地,恐怕就是产业界要好好想想的问题了。

缆线版PCIe规格OcuLink一开始将透过4个8GT/s连结提供32Gbits/s传输速率

评论