测试环路滤波器及射频电路设计详解

小数分频频率合成器在测试时必须外接一个环路滤波器电路与压控振荡器才能构成一个完整的锁相环电路。其外围电路中环路滤波器的设计好坏将直接影响到芯片的性能测试。以ADF4153小数分频频率合成器为例,研究了其外围环路滤波器的设计方法,给出了基于芯片测试的环路滤波器设计流程,并进行了验证测试。测试结果表明,该滤波器可满足小数分频频率合成器芯片测试的需要。在进行小数分频频率合成器的芯片测试时,数字部分可以通过常规的数字测试方法即可以实现;而输出射频信号的相位噪声、杂散噪声则需要芯片工作在正常的输出状态下才能测试。小数分频频率合成器芯片在测试时需要与外接环路滤波器(LF)、压控振荡器(VCO)才能构成完整的锁相环回路,在具备正常的芯片功能的前提下才能实现对其相位噪声、杂散噪声下的测试。

本文引用地址:https://www.eepw.com.cn/article/272350.htm压控振荡器均使用现成的器件,在挑选器件时注意性能指标的匹配就可以,只有环路滤波器才是需要计算和设计的。环路滤波器在整个电路中主要作为一个低通滤波器,它将芯片鉴相器输出的脉冲信号进行低通滤波,将高频分量滤除,最终得到一个相对平滑的直流电压信号去控制VCO工作,从而获得一个稳定的频率输出。环路滤波器的性能将直接影响到小数分频频率合成器芯片性能的测试。

本文以ADF 4153型小数分频频率合成器为例,给出了容易实现的三阶环路滤波器的设计方法,能够满足芯片实际测试的需要。

外接环路滤波器的设计

环路滤波器是电荷泵锁相环电路的重要环节,它连接在电荷泵和压控振荡器之间。锁相环的基本频率特性是由环路滤波器决定的。实际上,正是由于环路滤波器的存在,锁相环才可以选择工作在任意的中心频率和带宽内。环路滤波器的类型多种多样,大致分为有源滤波器和无源滤波器两大类,无源滤波器与有源滤波器相比,其优点在于:结构简单、低噪声、高稳定度和易以实现。

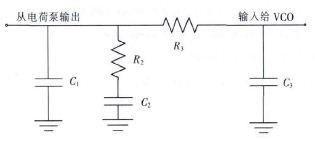

最常见的无源滤波器是如图1所示的三阶滤波器。一般而言,环路滤波器的带宽应为PFD频率(通道间隔)的1/10.提高环路带宽会缩短锁定时间。但环路带宽过大会大幅度地增加不稳定性,从而导致锁相环无法锁定的状态。

图1三阶环路滤波器

环路滤波器设计参数的选择

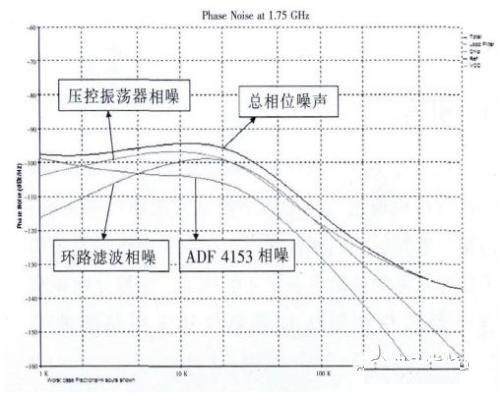

为了研究环路滤波器对锁相环输出频率相位噪声的影响,设计出符合芯片测试需要的外围环路滤波器。我们在ADIsimPLL软件中进行了如下仿真配置。器件型号:ADF 4153,fPFD=25MHz(理想信号源),INT=69,FRAC=101,MOD=125,VCO采用ZComm公司的V674ME34-LF,在该配置下,预期输出的RFOUT=1.7452GHz.

a)设定环路滤波器带宽为20kHz,相位裕度50°,其相位噪声的仿真情况如图2所示。

图2环路带宽20kHz时的相位噪声仿真图

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论