冗余时钟的平滑时钟切换——电子设计

摘要:

本文引用地址:https://www.eepw.com.cn/article/271856.htm检测到时钟丢失时平滑切换到冗余时钟源有助于避免系统运行中断。

正文:

当今许多数据通信、网络和计算机系统都需要实现时钟冗余。组件或板级故障甚至简单的定期系统维护等引起的任何中断都不应造成系统运行中断。因此,为整个电路工作提供时序的系统时钟必须避免因任何异常情况而中断。带冗余的理想时钟发生器也必须能在检测到时钟错误或丢失的情况下从母时钟源平滑切换到子时钟源或晶振。

以下给出几类常用的冗余时钟方案,其中包括:

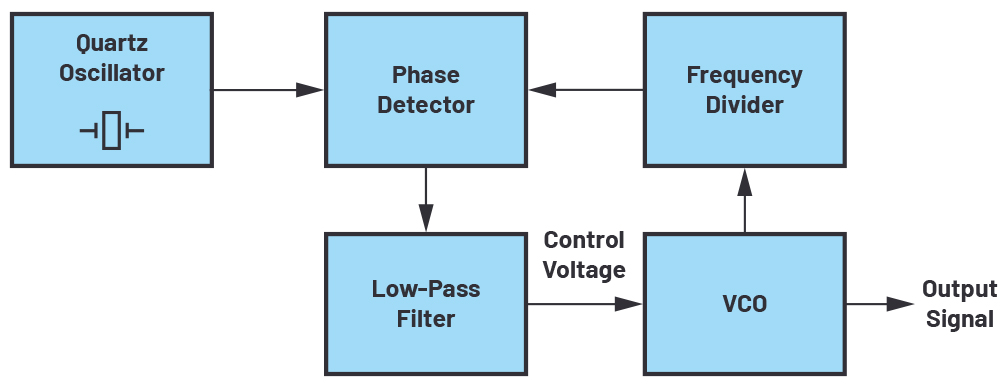

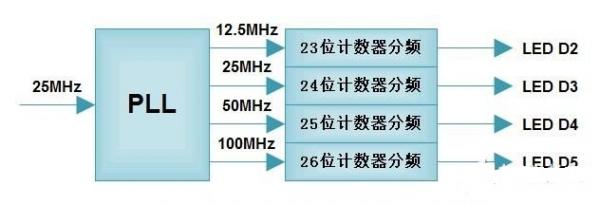

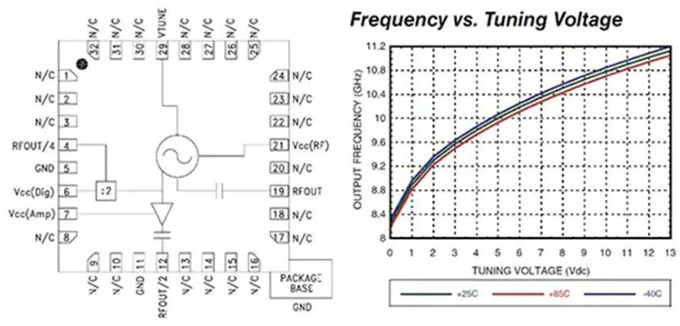

动态时钟切换:根据这种方案,系统在检测到母时钟源丢失或错误的情况下可自动切换到子时钟源。这种架构必须配备基于VCO的PLL。动态时钟切换要求:(1)具备错误或丢失参考时钟检测器,以及(2)要求电路能顺利无误地切换到子时钟源。

基于DCXO的时钟切换:根据这种方案,数控晶体振荡器(DCXO)可在母参考时钟源存在或丢失时提供时钟源。在存在参考时钟的情况下,DCXO会保持对参考时钟的PLL锁定。而在参考时钟丢失的情况下,DCXO则会通过保持参考时钟的最后相位和频率状态来提供时钟。

动态时钟切换与基于DCXO的时钟切换的对比

基于PLL的动态时钟切换是一种切实可行的时钟切换方式,这种操作方式可实现时钟之间的平滑切换。在时钟切换期内,会有单位周期相位校正(PCC)填入(或消除)母参考时钟和子参考时钟之间的相位差。母时钟源和子时钟源之间可能存在较大的相位误差,这会造成在切换时间不够长的情况下输出时钟出现较大相位冲突。基于PLL的器件应能够通过延长切换时间让单位周期相位校正(PCC)保持较小值,进而最大限度地减少相位冲突。PCC值的选择必须足够小,使其在切换期内不会对下游PLL或同步系统的设置/保持时间造成不利影响。

基于DCXO的时钟切换方案采用可牵引晶振锁相到参考时钟。DCXO在母时钟故障的情况下可保存参考时钟最后的频率和相位信息,从而有助于完成持续无误的操作。当参考时钟恢复时,DXCO能够自动与该时钟重新实现同步。基于DXCO的时钟切换相对于动态时钟切换而言可能具有一定的优势,但同时也存在自身的不足:

1. 需要外部可牵引晶振。这种类型的晶振通常尺寸较大,需占用更多PCB面积;

2. 由于晶振牵引范围有限,因此频率锁定范围也有限。这就导致基于DXCO的标准器件的最大频率变化限制为+/- 200PPM左右;

3. 速度太慢。DCXO PLL响应性使参考切换时间仅局限于数百毫秒(ms)的水平上;

4. 切换电容阵列会使频率单独改变,这就导致出现低频相位冲突。覆盖参考时钟全部PPM变化的电容阵列数量有限(典型设计中只有10个)。由于DCXO输出相位噪声(或相位冲突)过大,设计人员不愿在高性能应用中使用这种器件;

5. 由于器件的架构特性,当存在良好参考时钟时,输出时钟会在此期间显出DCXO不尽人意的相位噪声(或相位冲突)特性,而在参考时钟暂时丢失的情况下,倒能提供干净的晶振输出频率。这是因为参考时钟丢失时,DCXO仍能保持参考时钟的最后相位和频率状态且没有任何更新,因此也就不存在相位冲突;

6. 基于DCXO的器件的PLL带宽低(近2KHz)会造成跟踪误差过大;

7. 该器件因其PLL带宽低而不具备扩频意识。

基于DCXO的架构的低带宽有一定的优势,尤其是在参考时钟切换时表现尤为突出。在母参考时钟丢失而器件正被切换到子参考时钟或晶振期间,较长的切换时间会使单位周期相位校正(PCC)值极小,从而有可能实现平滑的时钟切换。理想的平滑时钟切换器件应当是具有低PCC值的基于PLL的动态时钟切换,或许需要时钟切换时PLL能够将带宽从额定值1 MHz降至5-10 KHz的水平。利用这种可变的PLL带宽架构,我们能够实现平滑的时钟切换。

参考时钟和晶振之间的动态切换

基于PLL的动态时钟切换可能不只能在参考时钟之间实现,还可在参考时钟和晶振输入之间实现。在检测到时钟错误或丢失的情况下,VCO能够切换到晶振输入。只要平滑完成切换,这在功能上就与故障安全器件相同,只是它不会存在任何基于DCXO的器件的缺点,特别是上述第5点提及的问题。在这种情况下,既不需要可牵引晶振,也不会出现相位冲突问题。

单位周期相位校正(PCC)实现平滑切换

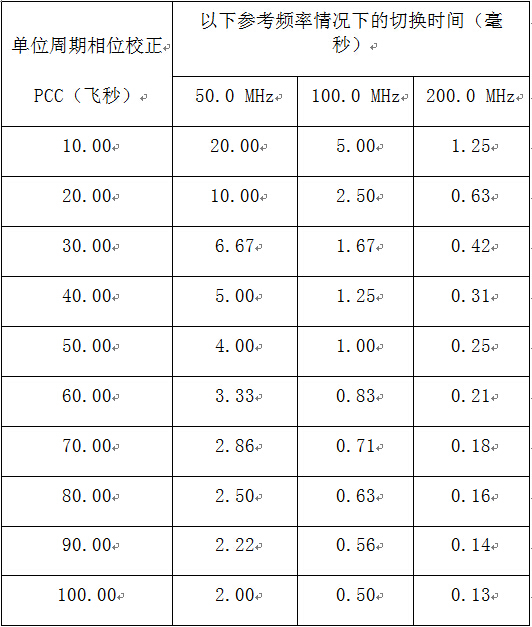

表1给出了50MHz、100MHz和200MHz等参考频率下计算得出的不同单位周期相位校正的切换时间。这里,我们假定相同频率但180°反相的两个参考时钟之间进行切换。不同参考频率下的单位周期相位校正(PCC)和切换时间曲线变化如图1所示。

表1:不同参考频率下切换时间和单位周期相位校正的对比情况

从上图可以看出,单位周期相位校正(PCC)和时钟切换时间曲线呈指数变化。PCC值越大,切换时间就越短。而PCC值越小,切换时间则呈指数级增加。请注意,我们就该曲线图做了如下假设:(a)PLL为线性相位错误校正,(b)PLL响应是在理想状态下,没有过冲或下冲。而在现实情况下,切换时间会比这里显示的要长,而且很大程度上取决于PLL系统响应。此外,我们还要注意,PCC值不变的情况下,时钟频率越高,切换时间会越短。

基于DCXO的故障安全器件实际系统应用的经验数据显示,20飞秒的PCC足以满足100-200 MHz频率范围的数据通信应用需求。在PCC为20飞秒的情况下,时钟切换造成的相位冲突微不足道,不会对系统性能造成不利影响。为此,我们建议50 MHz的参考时钟应采取的方案为20飞秒的PCC对应10 ms的切换时间。

动态平滑切换器件的设计通常包括两个功能块,如下所述:

1. 丢失参考时钟或错误相位误差检测器电路:这将提供错误输出,显示正在启动时钟切换。必须规定用复位输入引脚对错误输出进行复位。

2. 参考时钟切换电路:检测到错误后,电路将被切换到子参考时钟。子参考时钟可以是外部时钟源,也可以是晶振。在切换时间内,必须降低PLL带宽以实现平滑切换。

本文介绍了冗余时钟发生器源实现平滑时钟切换的不同方法,以及不同冗余时钟发生器的优劣势。基于PLL的动态时钟切换可平滑无误地实现时钟切换,建议使用该方法。动态时钟切换的关键要求是,应特别注意单位周期相位校正(PCC)的问题。在检测到时钟错误或丢失情况下,以上建议的动态时钟切换的独特特性能够实现从母时钟源到子时钟源或晶振的平滑时钟切换。

参考资料:

http://www.cypress.com/?rID=12622 – 了解赛普拉斯的零延迟缓冲器

http://www.cypress.com/?mpn=CY23FS04ZXI – 赛普拉斯的DCXO产品系列

负离子发生器相关文章:负离子发生器原理 晶振相关文章:晶振原理 离子色谱仪相关文章:离子色谱仪原理

评论