专家观点:暗场矽晶象征黑暗时代即将来临?

虽然传统的制程微缩得以在晶片中填入更多的电晶体,却使得晶片永远处于更“黑暗”的状态,而新兴的单晶片 3D 技术可望让晶片得以“重见光明”。

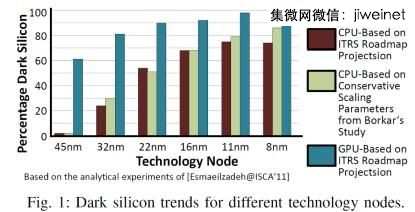

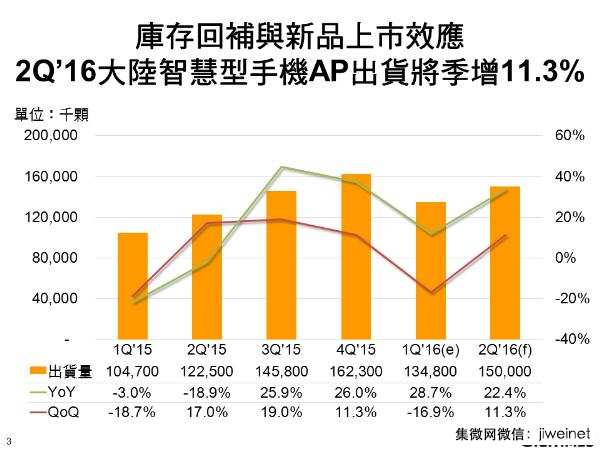

本文引用地址:https://www.eepw.com.cn/article/269648.htm“暗场矽晶”(dark silicon)指的是晶片中必须断电以避免过热的部份。在2014年的国际电子元件会议(IEDM)上,ARM的总工程师Greg Yeric指出,在20nm技术节点(包括16/14nm FinFET )时,暗矽的部份预计将占整个晶片面积的1/3,而到了5nm技术节点时还将增加到占80%的面积。

如今,制程微缩不再遵循Dennard's Law,在更薄闸电介质时越来越难以避免漏电急剧增加,“因此,尽管几何尺寸持续微缩,阈值电压却未随之降低。”

不同技术节点的暗矽趋势

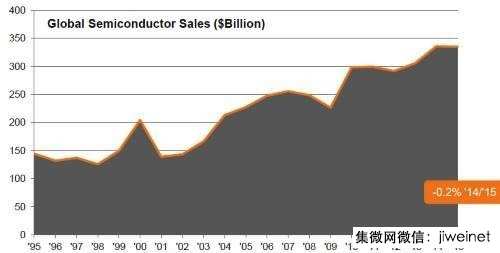

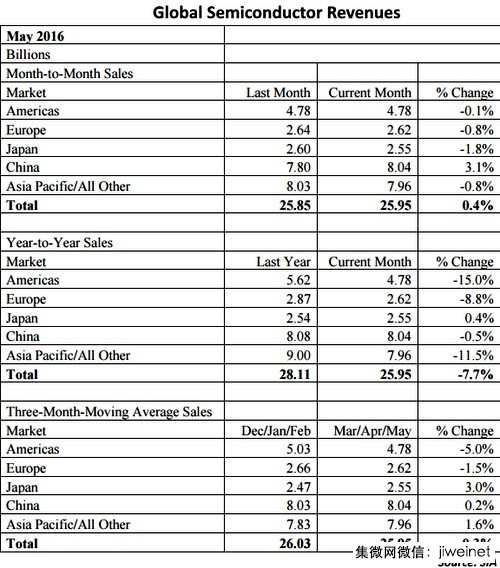

一旦考虑到晶片成本,这种黑暗的前景似乎更是雪上加霜。在最近的SEMI产业技术论(ISS),博通(Broadcom)总裁兼执行长Scott McGregor表示,呈指数上升成本将对产业带来变化:

每电晶体成本持续攀升

设计成本急剧增加

这为半导体产业描绘了一个非常黑暗的未来。为了开发使用更昂贵电晶体的设计,我们更需要指数级的投资。因此,Scott McGregor总结指出这个“半导体产业前进的重大变化”将是不可避免的。

为了寻找隧道尽头的一线曙光,ARM技术长Mike Muller提出以下三点建议:

.推动如绝缘矽(SOI)等新的晶片技术进展

.利用高能效、高密度的记忆体来填补部份的“暗场”

.结合最佳制程技术,以 3D IC 实现各种不同的功能。 3D IC 将“成为我们提供高能效解决方案的关键部份”。

的确,Sony日前宣布加入FDSOI Club,未来可望“使其GNSS晶片功耗从10mW降低至1mW。”

在IEDM 2014,多个研究论文都提出了单晶片 3D 技术与记忆体,如 RRAM 可在逻辑元件顶端成形为后段制程(BEOL)的一部份,有效地形成单晶片 3D 电路。此外,单晶片 3D 的一般情况是,上层电晶体自然形成SOI,因而可透过结合降低阈值的 SOI 达到功效提升,同时降低平均导线长度,并进一步降低导线功率与延迟。CEA Leti携手ST Micro、IBM与高通(Qualcomm)等公司,发表了单晶片 3D 技术 CoolCube ,可进一步实现 3D VLSI 微缩。下图显示CEA Leti发表期望在未来打造的全球单晶片 3D 生态系统。

单晶片3D生态系统

单晶片3D 技术可望带来更广阔的光明前景。直到最近,迈向单晶片 3D 的道路必须变更至前段制程(FEOL)。 FEOL 的制程改变一直是微缩的一部份,但它相当昂贵,而且大多只能由技术先进的主要业者来进行。如今,随着新兴的精确接合机(如EVG或Nikon推出的产品) 等工具进展,改变了单晶片 3D 技术的游戏规则。“...真正的单晶片 3D IC 并不需要新的电晶体资讯配方。现有的任何晶圆厂就能在制程技术上因应变化调整,为一系列的产品功能强化提供非常具有竞争力的成本,以及透过微缩为更好的产 品组合提供长期的发展蓝图。”

最终的结果是,虽然传统的制程微缩看起来将使晶片永远处于更“黑暗”的状态,但新兴的单晶片 3D 技术可望让晶片得以“重见光明”。

评论