一种数字示波器的微处理器硬件电路设计

引言

随着通信技术的迅猛发展,电信号越来越复杂化和瞬态化,开发人员对测量领域必不可少的工具——数字示波器的性能提出了越来越高的要求。最大限度提高实时采样率和波形捕获能力成为了国内外众多数字示波器生产厂商研究的重点,实时采样率和波形捕获率的提高又必然带来大量高速波形数据的传输、保存和处理的问题。因此,作为数字示波器数据处理和系统控制的中枢,微处理器性能至关重要。本文选用TI公司的双核DSP OMAP-L138作为本设计的微处理器,并实现了一种数字示波器微处理器硬件设计。

数字示波器的基本架构

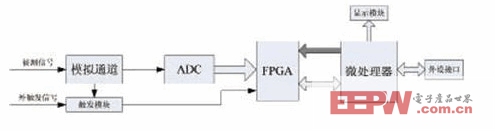

目前数字示波器多采用DSP、内嵌微处理器型FPGA或微处理器+FPGA架构。虽然内嵌微处理器型FPGA灵活性强,可以充分进行设计开发和验证,便于系统升级且FPGA外围电路简单。但是该类型FPGA属于高端FPGA,价高且供货渠道难得,不适合低成本的数字示波器使用。若单独使用DSP,虽然其数据处理能力强大,运行速度较高,但DSP的控制能力不突出,且数字示波器的采样率越来越高,DSP内部不能做数据流降速和缓存,当设计采用高实时采样率的ADC,就得选用频率更高且内部存储资源更丰富的DSP,而此类DSP一般都价格昂贵,同样不适合低成本的数字示波器使用。因此,微处理器+FPGA架构的方案是本设计首选。微处理器+FPGA架构的数字示波器的系统结构图如图1所示:

图1 微处理器+FPGA架构的数字示波器系统结构图

被测信号经模拟通道运放调理后送到ADC器件;ADC转换器将输入端的信号转换成相应的数字信号并经过FPGA缓存和预处理;微处理器对采样得到的数字信号进行相关处理与运算;最后将波形送到屏幕上显示,完成一次采集过程。同时采集过程中触发电路不断监测输入信号,看是否出现触发状态,触发条件决定了波形的起始位置,触发系统能够保证被测波形能够稳定的显示到屏幕上。

评论