FPGA电路设计: 如何应对电源相关问题的挑战

引言

在设计可编程门阵列(FPGA)电路时,必须极端重视电源问题,从而使最终产品能在所有可能的条件下无缺陷工作并处于最优状态。FPGA 电路电源有两项需考虑的问题: FPGA 电路上电要求和电路功耗分析。这篇文章针对这两方面的要求,讨论您可能遇到的问题,以及解决方案。

目前FPGA电路设计所面临的问题

FPGA电路通常需要多路电源输入。为优化开机时的电流拖曳,防止锁死和永久性的电路损坏,同时也为了防止开机接通时的毛刺干扰和降低开机接通的功耗,这些电源输入必须具有精确的上电序列以及正确的电压变化率。如何实现复杂多路供电的精确控制是FPGA电路设计验证过程中的难点。此外,随着项目的发展,FPGA电路设计指标通常会发生变化,灵活简单的上电参数调整方式也是工程师在进行前期电路设计时所需要的。

在产品设计过程中,还需要测试各种工作条件下的FPGA电路功耗,捕获大电流尖峰的精确轮廓,并带有时戳,以确定尖峰出现的时间,从而确定设计必须提供的最大电源功耗。可能还需要为电源资源有限的产品(如电池供电设备)进行进一步功耗优化设计。

实例: 为 Xilinx Spartan-3 FPGA 设置上电规则并进行功耗分析

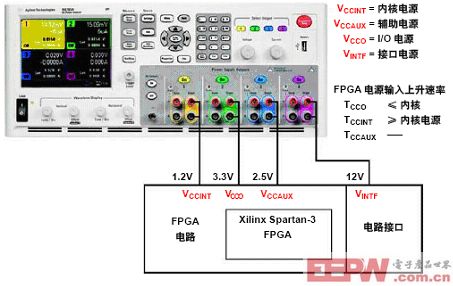

以Spartan-3系列FPGA为例,该FPGA电路需要四路供电,包括VCCINT(内核电源),VCCAUX(辅助电源),VCCO(I/O电源)和VINTF(接口电源)。其中VINTF用于为配置器件如NOR Flash PROM 或微控器供电的供电。为正确配置 FPGA,要在FPGA上电前 1毫秒开启,这一上电间隔保证了配置器件已完成上电,并准备好向FPGA发送来自存储器的配置。其他三路供电时序没有严格要求,但如果VCCINT 在 VCCAUX 之前,或与其同时上电,FPGA将消耗过多的内核电流。这一过度的电流拖曳将更快降低电池寿命,并导致负责功率分配的设计人员选择更大功率的调整器。

为验证不同上电时序对FPGA电路消耗电流的影响,使用安捷伦 N6705A直流功耗分析仪按图1所示与FPGA电路进行连接。

图1 使用多路电源为FPGA电路供电时的连接和设置

评论