基于TMS320DM642的视频监控系统的设计

摘要:该系统是以为核心,结合视频编解码芯片,并外扩大容量的存储器,实现4路视频输入与1路视频输出。本文主要介绍了基于TMS320DM642的视频监控系统的硬件设计,主要包括视频输入/输出模块的设计、电源模块的设计、外部存储器模块的设计,同时介绍了基本的硬件调试方法。该系统具有视频传输延迟短、处理速度快的优点,可应用于实时视频图像处理。

本文引用地址:https://www.eepw.com.cn/article/248193.htm关键词:TMS320DM642;视频监控;硬件设计

引言

本系统使用DM642作为核心,具有强大的运算能力和高速的数据通道。应用于如车牌识别、指纹识别、远程监控、智能化小区监控,图像算法研究均具有其他处理器难以抗衡的效果。

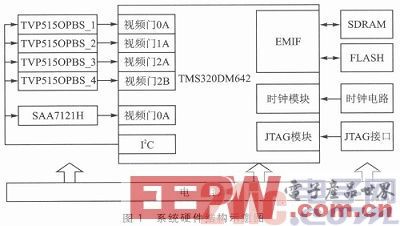

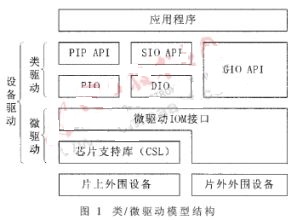

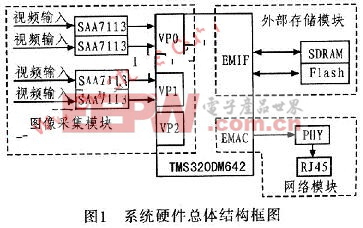

1 硬件总体设计

硬件结构如图1所示。输入的视频模拟信号经过解码芯片转换为数字信号,TMS320DM642的EDMA控制器将大量的视频数字信号存放在SDRAM内,供用户处理,然后将处理后的视频数字信号通过编码芯片SAA7121转换为PAL或NTSC标准制式的模拟电视信号输出。其中,可实现4路视频输入。

2 硬件各模块设计

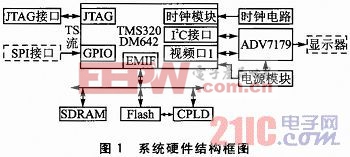

2.1 TMS320DM642

本系统选择的DSP为TMS320DM642,该处理器是专门为视频与图像应用量身定制的,能够满足各种类型视频客户端应用的需求,诸如VoIP视频、视频点播(VOD)、多信道数字视频录像以及高品质视频编解码等应用。

TMS320DM642具有高速并行处理内核,主频达到600MHz,计算能力达4 800 MPIS;采用高级甚长指令字结构,使得在一个指令周期内能够并行处理8条32位的指令,片内还集成了3个带视频FIFO的高速视频口(VP0~VP2)和1个McASP音频口。

TMS320DM642内部具有64通道的EDMA,保证CPU和外部器件可以高速并行的传输数据;它的EMIFA接口数据总线宽度为64位,最高数据存取频率为133 MHz,可直接与大容量、低成本的SDRAM芯片无缝连接。

TMS320DM642采用了两级缓存机制,CPU和一级程序高速缓存(LIP)及一级数据高速缓存(LID)直连,两块Cache分别为16 KB,工作在CPU全速访问状态。可配置的二级缓存(L2)有256 KB,它是数据和程序共用的。

2.2 电源管理模块

电源管理模块由2部分组成:供电电路和电源监测电路。

2.2.1 供电电路

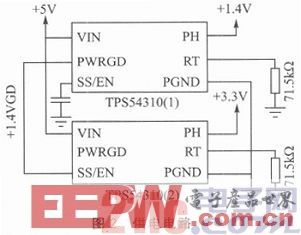

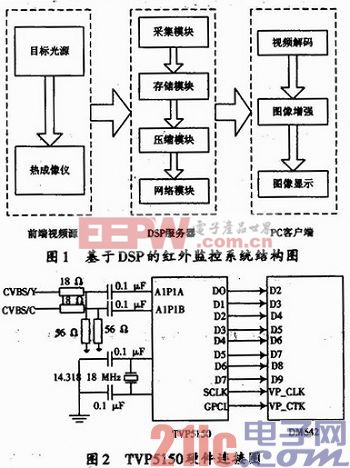

设计中采用2片TI公司的电源芯片0,分别给TMS320DM642提供Cvdd和Dvdd电压,如图2所示。

要解决Cvdd与Dvdd的上电顺序问题,将(1)的PWRGD引脚和TPS54310(2)的SS/EN引脚相连,当TPS54310(1)的输出电压达到稳定的+1.4 V后PWRGD引脚输出高电平送到TPS54310(2)的SS/EN引脚,当这个值高于1.2 V时,芯片(2)开始工作,这就保证了CPU内核的上电时间早于I/O的上电时间。

视频解码芯片TVP5150和编码芯片SAA7121采用+1.8 V和+3.3 V电压,由于涉及到模拟信号,因此这两个电压又分为数字(+1.8 V和+3.3 V)和模拟(+1.8 VA和+3.3 VA)两种;为了减小系统的功耗,用到的所有电平转换芯片都采用其输入容限(+5 V)内的+4.1 V电压。

设计选用TPS767D318芯片产生视频编解码时需要的+1.8VA和+3.3 VA模拟电压,通过片状铁氧体磁珠BLM18PG121SNl可以将+1.8VA转换为+1.8 V。将+5 V电压经过二极管MMBD4148降压,产生电平转换芯片所需的+4.1 V。

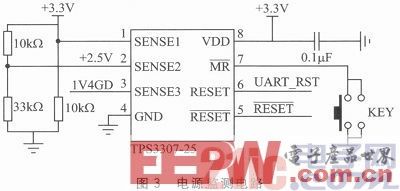

2.2.2 电源监测电路

设计中选用了TI公司生产的TPS3307-25芯片,它的固定复位信号时间长达200 ms,能满足系统中所有芯片的复位需求,可监控的电压范围包括2.5 V、3.3 V,本设计中对系统中+3.3 V电压和2.5 V电压以及TPS54310(1)的PWRGD引脚(1.4 V)进行监测。如图3所示,这个监测电路提供了两种复位方式:①在电源电压降到一定的门限值以下,将强制系统进入复位状态;②可以通过MR#引脚上的按键对系统进行手工复位。

2.3 外部存储器扩展模块

TMS320DM642的EMIFA是一个64位宽的接口,可以实现与多种同步和异步存储器的无缝连接。EMIFA最大的总线时钟可达133 MHz。

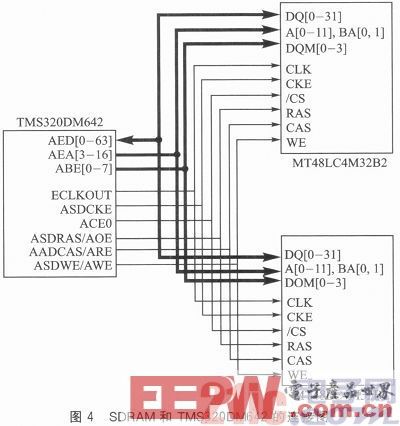

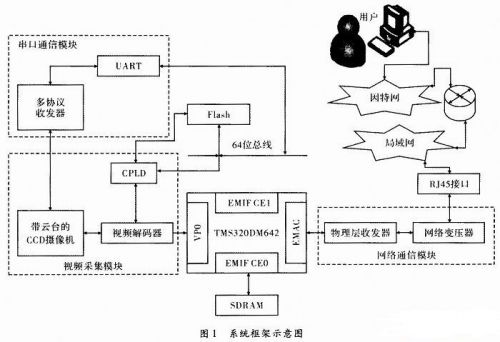

2.3.1 EMIFA与SDRAM的接口设计

本设计中选用2片Micron公司开发的32位数据总线的MT48LC4M3282芯片组成64位数据总线与EMFI直连。连接如图4所示。

SDRAM的地址线A[0-11]与TMS320DM642的地址线AEA[3-14]相连,由于该DSP的数据线是64位的,需要8个字节对齐,占用3位地址线,所以从TMS320DM642的地址线的第4位开始相连。两片SDRAM数据输入接口分别连接TMS320DM642的数据线AED[0-31]和AED[32-63]。字节使能引脚DQM[0-3]连接TMS320DM642的引脚ABE[0-7],其中,DQM0控制DQ[0-7]字节使能,DQM1控制DQ[8-15]字节使能,DQM2控制DQ[16-23]字节使能,DQM3控制DQ[24-31]字节使能。

2.3.2 EMIFA与FLASH的接口设计

本设计选用AMD公司生产的32 MB的AM29LV033C芯片。连接如图5所示。

AM29VL033C的输出使能(OE)和写使能(WE)与TMS320DM642的输出使能和写使能信号直接相连,AM29VL033C的芯片使能(CE)与TMS320DM642的ACE1相连,作为片选信号。8位数据总线直接与TMS320DM642数据总线相连,低19位地址总线A[18-0]与TMS320DM642的AEA[21-3]连接,A[19-21]三地址引脚用电阻下拉,保留待以后扩展应用。

存储器相关文章:存储器原理

评论