TMS320DM642的视频监控系统硬件设计

摘要:该系统是以TMS320DM642为核心,结合视频编解码芯片,并外扩大容量的存储器,实现4路视频输入与1路视频输出。本文主要介绍了基于TMS320DM642的视频监控系统的硬件设计,主要包括视频输入/输出模块的设计、电源模块的设计、外部存储器模块的设计,同时介绍了基本的硬件调试方法。该系统具有视频传输延迟短、处理速度快的优点,可应用于实时视频图像处理。

本文引用地址:https://www.eepw.com.cn/article/201610/309286.htm关键词:TMS320DM642;视频监控;硬件设计

引言

本系统使用DM642作为核心,具有强大的运算能力和高速的数据通道。应用于如车牌识别、指纹识别、远程监控、智能化小区监控,图像算法研究均具有其他处理器难以抗衡的效果。

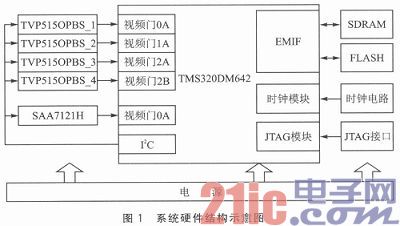

1 硬件总体设计

硬件结构如图1所示。输入的视频模拟信号经过解码芯片TVP5150转换为数字信号,TMS320DM642的EDMA控制器将大量的视频数字信号存放在SDRAM内,供用户处理,然后将处理后的视频数字信号通过编码芯片SAA7121转换为PAL或NTSC标准制式的模拟电视信号输出。其中,可实现4路视频输入。

2 硬件各模块设计

2.1 TMS320DM642

本系统选择的DSP为TMS320DM642,该处理器是专门为视频与图像应用量身定制的,能够满足各种类型视频客户端应用的需求,诸如VoIP视频、视频点播(VOD)、多信道数字视频录像以及高品质视频编解码等应用。

TMS320DM642具有高速并行处理内核,主频达到600MHz,计算能力达4 800 MPIS;采用高级甚长指令字结构,使得在一个指令周期内能够并行处理8条32位的指令,片内还集成了3个带视频FIFO的高速视频口(VP0~VP2)和1个McASP音频口。

TMS320DM642内部具有64通道的EDMA,保证CPU和外部器件可以高速并行的传输数据;它的EMIFA接口数据总线宽度为64位,最高数据存取频率为133 MHz,可直接与大容量、低成本的SDRAM芯片无缝连接。

TMS320DM642采用了两级缓存机制,CPU和一级程序高速缓存(LIP)及一级数据高速缓存(LID)直连,两块Cache分别为16 KB,工作在CPU全速访问状态。可配置的二级缓存(L2)有256 KB,它是数据和程序共用的。

2.2 电源管理模块

电源管理模块由2部分组成:供电电路和电源监测电路。

2.2.1 供电电路

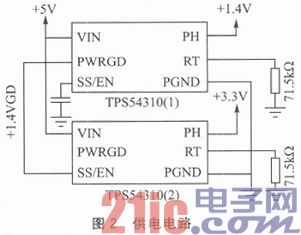

设计中采用2片TI公司的电源芯片TPS54310,分别给TMS320DM642提供Cvdd和Dvdd电压,如图2所示。

要解决Cvdd与Dvdd的上电顺序问题,将TPS54310(1)的PWRGD引脚和TPS54310(2)的SS/EN引脚相连,当TPS54310(1)的输出电压达到稳定的+1.4 V后PWRGD引脚输出高电平送到TPS54310(2)的SS/EN引脚,当这个值高于1.2 V时,芯片(2)开始工作,这就保证了CPU内核的上电时间早于I/O的上电时间。

视频解码芯片TVP5150和编码芯片SAA7121采用+1.8 V和+3.3 V电压,由于涉及到模拟信号,因此这两个电压又分为数字(+1.8 V和+3.3 V)和模拟(+1.8 VA和+3.3 VA)两种;为了减小系统的功耗,用到的所有电平转换芯片都采用其输入容限(+5 V)内的+4.1 V电压。

设计选用TPS767D318芯片产生视频编解码时需要的+1.8VA和+3.3 VA模拟电压,通过片状铁氧体磁珠BLM18PG121SNl可以将+1.8VA转换为+1.8 V。将+5 V电压经过二极管MMBD4148降压,产生电平转换芯片所需的+4.1 V。

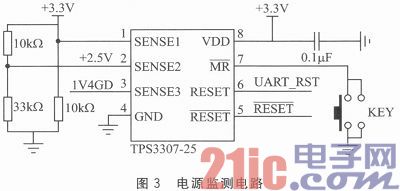

2.2.2 电源监测电路

设计中选用了TI公司生产的TPS3307-25芯片,它的固定复位信号时间长达200 ms,能满足系统中所有芯片的复位需求,可监控的电压范围包括2.5 V、3.3 V,本设计中对系统中+3.3 V电压和2.5 V电压以及TPS54310(1)的PWRGD引脚(1.4 V)进行监测。如图3所示,这个监测电路提供了两种复位方式:①在电源电压降到一定的门限值以下,将强制系统进入复位状态;②可以通过MR#引脚上的按键对系统进行手工复位。

2.3 外部存储器扩展模块

TMS320DM642的EMIFA是一个64位宽的接口,可以实现与多种同步和异步存储器的无缝连接。EMIFA最大的总线时钟可达133 MHz。

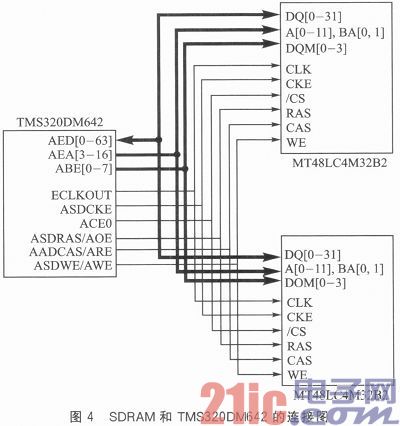

2.3.1 EMIFA与SDRAM的接口设计

本设计中选用2片Micron公司开发的32位数据总线的MT48LC4M3282芯片组成64位数据总线与EMFI直连。连接如图4所示。

SDRAM的地址线A[0-11]与TMS320DM642的地址线AEA[3-14]相连,由于该DSP的数据线是64位的,需要8个字节对齐,占用3位地址线,所以从TMS320DM642的地址线的第4位开始相连。两片SDRAM数据输入接口分别连接TMS320DM642的数据线AED[0-31]和AED[32-63]。字节使能引脚DQM[0-3]连接TMS320DM642的引脚ABE[0-7],其中,DQM0控制DQ[0-7]字节使能,DQM1控制DQ[8-15]字节使能,DQM2控制DQ[16-23]字节使能,DQM3控制DQ[24-31]字节使能。

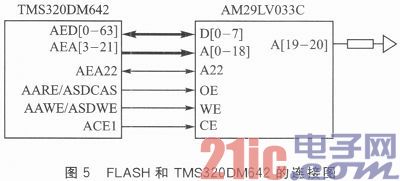

2.3.2 EMIFA与FLASH的接口设计

本设计选用AMD公司生产的32 MB的AM29LV033C芯片。连接如图5所示。

AM29VL033C的输出使能(OE)和写使能(WE)与TMS320DM642的输出使能和写使能信号直接相连,AM29VL033C的芯片使能(CE)与TMS320DM642的ACE1相连,作为片选信号。8位数据总线直接与TMS320DM642数据总线相连,低19位地址总线A[18-0]与TMS320DM642的AEA[21-3]连接,A[19-21]三地址引脚用电阻下拉,保留待以后扩展应用。

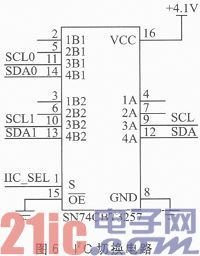

2.4 I2C总线模块

TMS320DM642集成有I2C总线接口,用于与I2C总线外设通信。本设计中TMS320DM642就是通过I2C总线模块对TVP5150、SAA7121进行配置的。由于需要对4个TVP5150进行不同的配置,而TVP5150只有两种I2C地址,所以一路I2C总线是无法实现对4路TVP5150的配置的。

如图6所示,采用信号分离器SN74CBT3257将I2C总线信号分离成两路,结合TVP5150的地址选择信号,分别对4路TVP5150进行配置。

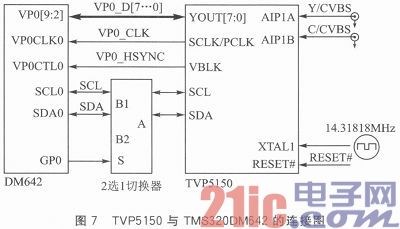

2.5 视频采集模块

本设计中TMS320DM642的3个视频口均采用了8位BT.656模式。其中VP0和VP1采用了单通道方式,VP2采用了双通道方式。

视频解码芯片选用了TI公司生产的TVP5150芯片。该芯片是一款超低功耗的视频解码器,正常工作时功耗仅为115 mW,在省电模式下功耗不超过1 mW,它支持PAL/NTSC/SECAM制式的视频信号。

视频采集部分的电路连接如图7所示,图中只给出了1个TVP5150芯片与VP0口连接的示意图,其他3个芯片的连接类似。

图中TVP5150的AIP1A和AIP1B是2个模拟视频输入,支持2路CVBS模拟信号或者1路S-Video模拟信号。图中的14.318 18 MHz时钟由CY223 81芯片提供,RESET#信号由电源监测模块提供,数据输出YOUT[7:0]与TMS320DM642的VP0[9:2]相连,SCLK引脚输出的27MHz时钟连接到TMS 320DM642的时钟输入引脚VP0CLK0,作为视频回放时的同步时钟使用,场消隐信号VBLK连接到TMS320DM642的VP0CTL0。

系统中使用了4片TVP5150来实现4路模拟视频的输入,TVP5150上与YOUT7复用的I2CSEL引脚通过接上拉或下拉电阻,可以进行从地址的选择(见表1),这样就可以将2个TVP5150芯片连接到同一组I2C总线上去。因此系统中用到了2组I2C总线,见I2C模块。

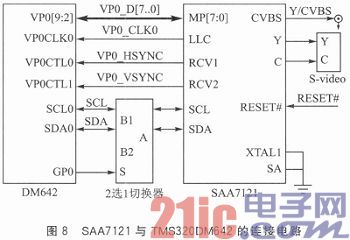

2.6 视频输出模块

本设计中使用TMS320DM643的VP0端口进行视频输出。视频编码芯片选用Philips公司生产的SAA7121芯片。该芯片是一款数字PAL/NTSC编码器,可将YUV数字化视频数据同时编码为NTSC/PAL制式的CVBS或S-video信号。系统的工作电压为3.3 V,可以接收MPEG解码数据,输入数据要求符合Cb-Y-Cr顺序的BT.656格式,每行720像素4:2:2 YUV复用数据。芯片包含1个同步时钟发生器和3个分别针对Y、C和CVBS的DAC,支持400 kHz的I2C总线协议。视频输出模块的电路连接如图8所示。

TMS320DM642的VP0口向SAA7121的MP口输出BT.656 4:2:2格式的数字视频信号,经过SAA7121芯片内部数据管理器模块分离出 Y信号和Cb、Cr信号,然后再送到相应的模数转换模块将数字视频信号变换成模拟视频信号,由CVBS(复合视频信号)或者Y、C(S-video信号)引脚输出。

2.7 时钟模块

本系统时钟源选择了50 MHz的高精度有源晶振。设计中TMS320DM642的CLKMODE1和CLKMODE0引脚分别接高电平和低电平,因此DSP倍频因子设置成12,即TMS320DM642的工作主频为50 MHz×12=600 MHz。另一方面,选择了133 MHz的高精度有源晶振为EMIF接口扩展SDRAM提供备用时钟。设计中TMS320DM642的ECLKINSEL1和ECLKINSEL0引脚分别接高电平和低电平,采用1/6×CPU时钟作为EMIF接口的同步时钟。

3 硬件调试

3.1 电源模块调试

焊接电源模块芯片及外围电路,输入5 V电压,测试3.3 V、1.8 V、1.4 V、4.1 V电压输出是否正常。上电后,检查各电压转换芯片是否发热,若发热则立即断开电源进行检查。

3.2 最小系统调试

在板上焊接TMS320DM642、SDRAM、FLASH、JTAG接口及各模块电路外围元件。仔细检查有无短路、断路、虚焊、漏焊、假焊等情况,无问题后上电,测量各芯片工作电压是否正常,用示波器测量各模块的工作时钟是否正常。利用JTAG口将硬件与计算机相连,配置好控制寄存器后,测试SDRAM读写功能是否正常,FLASH擦写功能是否正常。如果工作不正常,检查时序信号、硬件连接等情况。

3.3 视频输入输出调试

焊接TVP5150、SAA7121及外围相关元器件。测量各模块的工作时钟是否正常。利用TI公司提供的测试程序,测试系统能否正常地接收4路视频并输出视频。

结语

本系统充分利用DSP的高处理速度、大数据量处理能力的特点,结合编解码芯片,实现视频的快速多路输入与输出。扩展大容量的SDRAM利用TMS320DM642自身的EDMA,可以轻松地实现大数据量的存储与转移,方便对视频信号进行图像处理等操作。

评论