基于Nios II软核的多核处理器系统的设计与实现

摘要:本文设计了一个基于FPGA解决方案的多核处理器系统,整体上提高了系统性能,解决了单核处理能力提升受到的制约。通过对多核系统体系结构和核间通信技术的研究,最终实现了一个利用互斥核实现资源共享的双Nios II软核处理器系统,并在Altera公司的FPGA开发板DE2上进行测试,测试结果表明所设计的双核系统能稳定运行。

引言

多核处理器技术的研究源于工程师们认识到,在提高单核芯片速度的同时,会产生过多热量却无法带来相应的性能改善,传统的以提高主频提升性能的方法,会使处理器散发出巨大的热量,其性价比也令人难以接受,速度稍快的处理器价格更高。因此多核芯片应运而生,2001年IBM公司推出第一个商用的双核RISC(精简指令集计算机)处理器Power4。

目前关于多核技术的研究主要包括核结构研究(同构还是异构)、程序执行模型、Cache设计(多级Cache设计与一致性问题)、核间通信技术、总线设计、操作系统设计(任务调度、中断处理、同步互斥)、低功耗设计、存储器墙、可靠性及安全性设计。本文利用互斥核和共享存储器等技术实现多核系统共享资源的访问,使用Quartus II的Sopc Builder构建一个双NiosII软核处理器系统,最终在Altera的FPGA开发板DE2上验证了该系统的正确性。

1 系统总体设计方案

与单核处理器系统的设计所不同,在设计双核系统时有若干问题需要重新考虑:如何实现多处理器核之间的数据共享;在实现数据共享之后,双核系统必须提供有效的机制,以防止共享数据被破坏;为了提升整个系统的效率,必须仔细考虑系统任务的分配和调度如何进行,以免出现进程冲突或进程闲置,从而影响系统的整体性能。

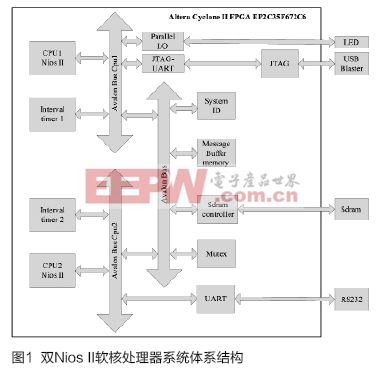

图1显示了双Nios II 嵌入式处理器核系统的体系结构。本系统中有两个Nios II处理器核,CPU1作为主要CPU用来负责控制和调度整个系统,CPU2作为从处理器用来负责具体任务的执行。其次,每个处理器都有独立的定时器作为看门狗使用,以防止处理器进入异常或死循环。此外,连接到CPU1的JTAG-UART接口,用于系统的各项测试。片上RAM作为共享存储器连接到两个处理器,提供处理数据的共享。而与CPU2相连的UART负责将处理结果传递到PC主机上显示。

2 系统软硬件设计

2.1 硬件设计

在双核系统中,为了实现并行处理应用程序的任务,系统必须为双核提供有效的数据处理和信息进程的共享机制。为此,本设计为系统配置了两种存储器的共享:一种处理器用来实现处理器之间状态的沟通,另一种用来实现处理数据的共享。此外由于两个处理器都会对共享数据存储器进行读写操作,这样就会产生一个问题:在不破坏存储器中数据的同时,如何确保系统正确地进行读写操作。因此硬件互斥核Mutex被嵌入双核处理器系统中。Mutex可以确保双核系统中只能有一个处理器来访问共享数据存储器。

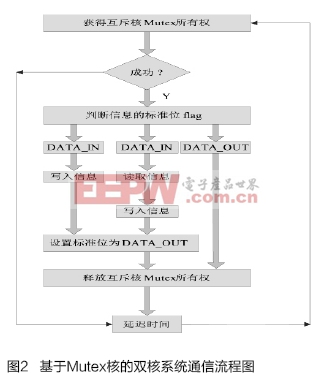

Mutex核实质上是一种共享资源,提供“测试和设置”操作。当处理器测试到Mutex核可用时,就会在一个具体操作中暂时占有Mutex核,之后当处理器完成对存储器的读写操作时就会释放Mutex核,具体过程如图2所示。对共享存储器的互斥访问是通过Mutex核的API函数来实现的:

Altera_avalon_mutex_open()

功能:声明一个Mutex句柄,允许所有其他函数访问Mutex核。

Altera_avalon_mutex_trylock()

功能:试图锁定Mutex核,若失败则立刻返回。

Altera_avalon_mutex_lock()

功能:锁定Mutex核,直到成功声明Mutex核才返回。

Altera_avalon_mutex_unlock()

功能:解锁Mutex核

Altera_avalon_mutex_is_mine()

功能:判断CPU是否拥有Mutex核

Altera_avalon_mutex_first_lock()

功能:测试复位后Mutex核是否被释放。

存储器相关文章:存储器原理

评论