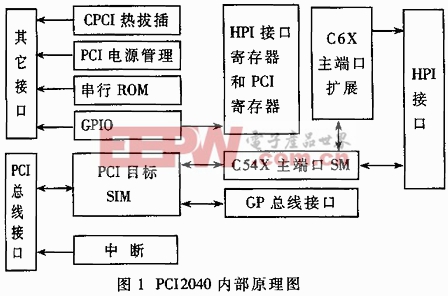

利用PCI2040将TMS320VC5420桥接到PCI总线上

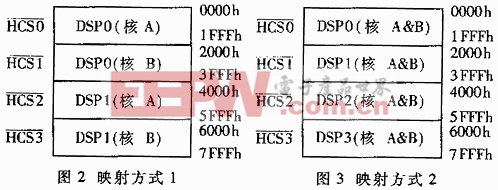

1 TMS320VC5420映射到主存的两种方式 TMS320VC5420是具有A、B两个核的DSP,根据TMS320VC5420的数量,有两种将TMS320VC5420映射到主存或PC存储空间的方式。若TMS320VC5420的数量少于三个,可用映射方式1(如图2)。如果TMS320VC5420的数量多于两个,可用映射方式2(如图3),这种方式将每个DSP映射到一个特定的存储器空间,每个DSP核或DSP子系统占用同样的存储空间。 值得注意的是:控制空间的偏移量是相对于PCI2040上的256字节PCI配置寄存器中的14H处控制空间基址寄存器所代表的值。 2 硬件方面的考虑 TMS320VC5420是一个双CPU设备,有两个独立的C54X子系统,能够实现核对核通信。尽管PCI2040不是专门设计用来与双CPU设备接口,但经过特殊的处理还是可以实现接口的。需要考虑的主要有三方面:①C6201HPI协议到TMS320VC5420 HPI-16协议的转换;②两个DSP核间的切换;③多个复位和多个断的处理。

1 TMS320VC5420映射到主存的两种方式 TMS320VC5420是具有A、B两个核的DSP,根据TMS320VC5420的数量,有两种将TMS320VC5420映射到主存或PC存储空间的方式。若TMS320VC5420的数量少于三个,可用映射方式1(如图2)。如果TMS320VC5420的数量多于两个,可用映射方式2(如图3),这种方式将每个DSP映射到一个特定的存储器空间,每个DSP核或DSP子系统占用同样的存储空间。 值得注意的是:控制空间的偏移量是相对于PCI2040上的256字节PCI配置寄存器中的14H处控制空间基址寄存器所代表的值。 2 硬件方面的考虑 TMS320VC5420是一个双CPU设备,有两个独立的C54X子系统,能够实现核对核通信。尽管PCI2040不是专门设计用来与双CPU设备接口,但经过特殊的处理还是可以实现接口的。需要考虑的主要有三方面:①C6201HPI协议到TMS320VC5420 HPI-16协议的转换;②两个DSP核间的切换;③多个复位和多个断的处理。 2.1 C6x HPI协议到TMS320VC5420 HPI-16的转换 TMS320VC5420对HPI总线提供了两种操作模式。 非多路复用模式(HMODE=1),TMS320VC5420 HPI接口提供一个18位地址总线,用来访问所有的内部存储器。 多路复用模式(HMODE=0),地址和数据复用同样的管脚。

2.1 C6x HPI协议到TMS320VC5420 HPI-16的转换 TMS320VC5420对HPI总线提供了两种操作模式。 非多路复用模式(HMODE=1),TMS320VC5420 HPI接口提供一个18位地址总线,用来访问所有的内部存储器。 多路复用模式(HMODE=0),地址和数据复用同样的管脚。 PCI2040只是完成多路复用模式,所以TMS320VC5420的HMODE脚必须被拖到地址。另外由于C6X HPI的HPDY信号低电平有效,而TMS320VC5420的HRDY信号高电平有效,所以针对TMS320BVC5420必须使用转换器(例如SN74ALCV04),这样才能将VCC_H端直接连接到VCC端。 2.2 两个DSP核间的切换 通过TMS320VC5420的SELA/B脚选择被访问的DSP子系统。例如可以将PCI2040的脚GPIO2连到SELA/B,这样就可以通过GPIO2的高低电平来选择核A或核B。 2.3 多个HRST TMS320BVC5420的两种方式控制每个子系统的复位功能。 第一种,在HPIRS脚从低电平过渡到高电平时,同时保持A_RS和B_RS脚处于低电平,可以在两个核处于复位状态的同时将应用程序代码下载到DSP中。下载完之后,可以将A_RS和B_RS重新设置成高电平而将两个子系统拖出复位状态。 在HPIRS脚从低电平过渡到高电平时,同时保持A_RS和B_RS脚处于高电平也可以在两个核处于复位状态的同时将应用程序代码下载到DSP中。下载完之后,可以通过对地址2FH的写操作将子系统拖出复位状态。另外,可以根据SELA/B的值选择指定的子系统。 第二种,使用Power-on复位逻辑复位每个子系统(A_RS和B_RS),这时需要将HPIRS脚连接到PIC2040的HRST脚。注意,当应用程序下载完成之后,必须有一个向地址2FH的写操作,以将子系统拖出复位状态。

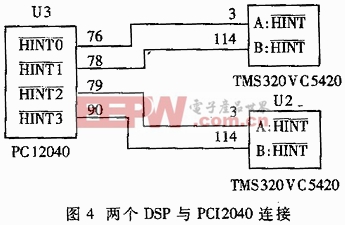

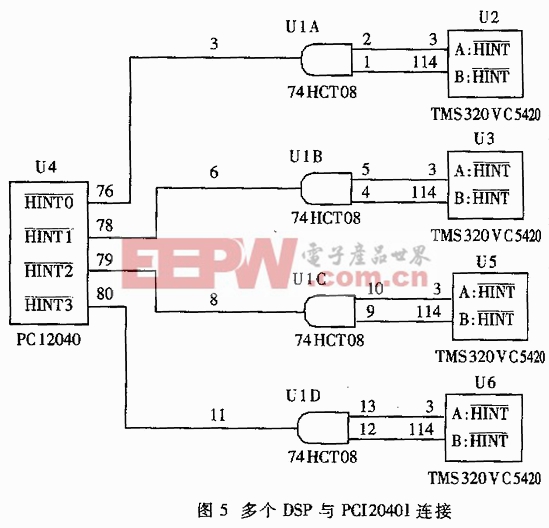

PCI2040只是完成多路复用模式,所以TMS320VC5420的HMODE脚必须被拖到地址。另外由于C6X HPI的HPDY信号低电平有效,而TMS320VC5420的HRDY信号高电平有效,所以针对TMS320BVC5420必须使用转换器(例如SN74ALCV04),这样才能将VCC_H端直接连接到VCC端。 2.2 两个DSP核间的切换 通过TMS320VC5420的SELA/B脚选择被访问的DSP子系统。例如可以将PCI2040的脚GPIO2连到SELA/B,这样就可以通过GPIO2的高低电平来选择核A或核B。 2.3 多个HRST TMS320BVC5420的两种方式控制每个子系统的复位功能。 第一种,在HPIRS脚从低电平过渡到高电平时,同时保持A_RS和B_RS脚处于低电平,可以在两个核处于复位状态的同时将应用程序代码下载到DSP中。下载完之后,可以将A_RS和B_RS重新设置成高电平而将两个子系统拖出复位状态。 在HPIRS脚从低电平过渡到高电平时,同时保持A_RS和B_RS脚处于高电平也可以在两个核处于复位状态的同时将应用程序代码下载到DSP中。下载完之后,可以通过对地址2FH的写操作将子系统拖出复位状态。另外,可以根据SELA/B的值选择指定的子系统。 第二种,使用Power-on复位逻辑复位每个子系统(A_RS和B_RS),这时需要将HPIRS脚连接到PIC2040的HRST脚。注意,当应用程序下载完成之后,必须有一个向地址2FH的写操作,以将子系统拖出复位状态。 2.4 对同一个DSP产生的两个HINT中断的处理 根据连接到PCI2040的TMS320VC5420数量可决定多个中断的处理方式。 如果有两个或更少的TMS320VC5420,可以将第一个TMS320VC5420的A_HINT连到HINT0,将B)HINT连到HINT1。将PCI2040的HINT2和HINT3连接到第二个TMS320VC5420的A_HINT和B_HINT(如图4),这种情况下存储器的设置利用映射方式1。 如果板子上含有多个两个的TMS320VC5420,此时需要将每个DSP上的两个中断相与(如图5)。每个DSP上的中断共享PCI2040的同一根中断线,这样就无法知道某个DSP上到底到个子系统申请的中断。此时必须向每个子系统中HPLC寄存器的HINT位写1,

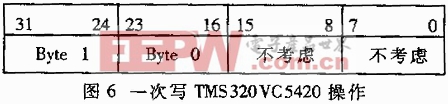

2.4 对同一个DSP产生的两个HINT中断的处理 根据连接到PCI2040的TMS320VC5420数量可决定多个中断的处理方式。 如果有两个或更少的TMS320VC5420,可以将第一个TMS320VC5420的A_HINT连到HINT0,将B)HINT连到HINT1。将PCI2040的HINT2和HINT3连接到第二个TMS320VC5420的A_HINT和B_HINT(如图4),这种情况下存储器的设置利用映射方式1。 如果板子上含有多个两个的TMS320VC5420,此时需要将每个DSP上的两个中断相与(如图5)。每个DSP上的中断共享PCI2040的同一根中断线,这样就无法知道某个DSP上到底到个子系统申请的中断。此时必须向每个子系统中HPLC寄存器的HINT位写1, 这种情况下存储器的设置利用映射方式2。 3 软件方面的考虑 C6X有一个16位的HPI接口,使用32位的字长,所以所有的HPI操作需要两个HPI周期。既然PCI2040的16位接口用来与C6X接口,所以PCI2040也需要两个HPI周期。与C6X不同,TMS320VC5420使用16位的字长,这样只需要一个HPI周期就可以完成一次操作。所以程序员通过PCI2040访问TMS320VC5420时,必须知道对DSP的读和写需要遵循特殊的原则。 3.1 向HPIA、HPIC和HPIC寄存器写数据 当向HPIA(HPI地址寄存器)、HPIC(HPI控制寄存器)和HPID(HPI数据寄存器)写数据时,由于PCI2040对HPI口两个周期的操作是针对同一个寄存器,所以第一个周期写的数据会在第二个周期被覆盖。故应将数据多次写到寄存器中,对保证写入数据的正确(如图6)。 3.2 从HPIA、HPIC、HPID寄存器读数据

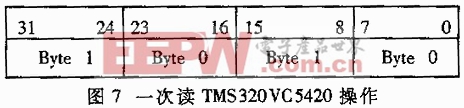

这种情况下存储器的设置利用映射方式2。 3 软件方面的考虑 C6X有一个16位的HPI接口,使用32位的字长,所以所有的HPI操作需要两个HPI周期。既然PCI2040的16位接口用来与C6X接口,所以PCI2040也需要两个HPI周期。与C6X不同,TMS320VC5420使用16位的字长,这样只需要一个HPI周期就可以完成一次操作。所以程序员通过PCI2040访问TMS320VC5420时,必须知道对DSP的读和写需要遵循特殊的原则。 3.1 向HPIA、HPIC和HPIC寄存器写数据 当向HPIA(HPI地址寄存器)、HPIC(HPI控制寄存器)和HPID(HPI数据寄存器)写数据时,由于PCI2040对HPI口两个周期的操作是针对同一个寄存器,所以第一个周期写的数据会在第二个周期被覆盖。故应将数据多次写到寄存器中,对保证写入数据的正确(如图6)。 3.2 从HPIA、HPIC、HPID寄存器读数据 当从HPIA、HPIC、HPID寄存器读数据时,PCI读这些寄存器两遍,返回PCI双字节的上下两部分(如图7)。 3.3 利用自动增特性 为了最大提高HPI的性能,在读和写HPID寄存器时,利用DSP寄存器在第一个和第二个HPI周期中HPIA的自动增特性。自动增特性使得经PCI总线可以对两个字连续的进行读和写,最终使得一次性可以读写32位的字长,这样就有效地加速了数据传输速率。

当从HPIA、HPIC、HPID寄存器读数据时,PCI读这些寄存器两遍,返回PCI双字节的上下两部分(如图7)。 3.3 利用自动增特性 为了最大提高HPI的性能,在读和写HPID寄存器时,利用DSP寄存器在第一个和第二个HPI周期中HPIA的自动增特性。自动增特性使得经PCI总线可以对两个字连续的进行读和写,最终使得一次性可以读写32位的字长,这样就有效地加速了数据传输速率。

评论