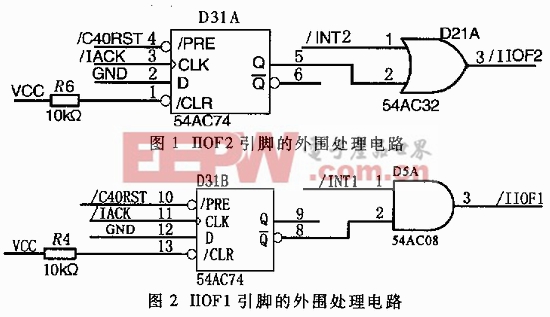

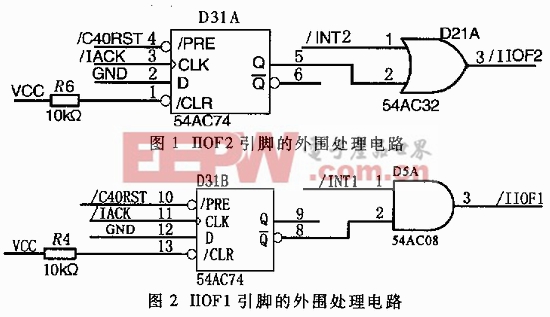

摘要:详细分析了TI公司TMS320C40和TMS320VC5402两类DSP芯片的系统引导特点。在了解机理的基础上,叙述了工程设计中创建系统引导表的具体步骤,给出了创建步骤中所需的键接文件范例,并进行了说明。关键词:TMS320C40 TMS320VC5402 系统引导 引导表 目前,DSP芯片正逐渐应用到电子设计中,其中应用最广泛的是TI公司生产的DSP系列产品。笔者在工程项目的开发中,对TMS320C40和TMS320VC5402(以下简称C40和C5402)进行了系统的研究,并成功的实现了DSP的脱机运行。本文希望通过对C40和C5402两种芯片系统引导的描述使大家了解设计DSP系列引导的步骤,能够利用DSP设计自己的设备。 1 C40和C5402的系统引导机理 TI公司的每一种DSP产品,都为用户设计了多种系统的引导方式,如串口、并行加载、HPI加载等。C40和C5402的引导方式如表1所示。表1 C40和C5402的引导方式 C40C5402程序执行地址IIOF3IIOF2IIOF1IIOF010030 0000H1101HPI口引导模式(由INT2引脚识别)24000 0000H1011串行8位EEPROM引导模式(INT3)36000 0000H1001并行引导模式48000 0000H0111标准8位串行口McBPSP15A000 0000H0101标准16位串行口McBPSP26C000 0000H0011I/O口引导模式7RESERVE0001HPI口引导模式(由入口点进行识别)8通讯口引导方式1111在工程中,使用最广泛的EEPROM并行加载方式。它又分为8位数据宽度和16位数据宽度两种,笔者采用的是8位数据宽度的并行加载方式。需要注意的是C40的数据总线宽度是32位,引导表中数据存放的原则是低字节在低地址。C5402的数据宽度是16位,引导表中数据的存放原则是高字节在低地址。 1.1 C40的并行引导模式 C40加电时,芯片塞满到ROMAN引脚为高电平,进入微处理器模式。再检测IIOF3~IIOF0引脚电平,决定系统的引导方式和选择并行引导的始地址。执行程序引导程序时,程序和数据存取等时间可以设置为最长7个等待周期。若软件延时不够用,则需要辅助硬件延时等待。程序引导完毕后,会在IACK引脚产生脉冲,使引脚可以作为中断引脚使用并转入到程序的入口地址开始执行程序。 C40由中断引脚的电平决定系统引导后的程序执行地址,或决定是否由通讯口进行程序的加载。采用0030 0000H作为主程序的入口地址,即将一片28C256地址设计为0030 0000H~0030 7FFFH。在系统引导时,需维持IIOF3~IIOF0四个引脚电平为1101。 下面以IIOF2引脚和IIOF1引脚为例,叙述一下系统引导前后的中断引脚的处理过程。图1电路是IIOF2引脚的外围处理电路。在系统加电时,D31A的/PRE=0、/CLR=1,置位端有效,所以Q=1、/IIOF2=1。加电完毕后,/PRE=1、/CLR=1,此时无/IACK信号,Q=1、/IIOF2=1,C40开始程序的加载工作。当C40程序加载完毕时,IACK引脚会产生一个脉冲,Q=D=0,/IIOF2=/INT2。C40会转入程序的入口地址执行程序,此时D触发器电路的工作已经完成,C40此时可以处理中断信号。图2电路是IIOF1引脚的外围处理电路。系统引导时,要求/IIOF1引脚电平为低电平。 1.2 C5402并行引导模式 C5402加电时,如果芯片检测到MP/MC引脚电平为低电平,系统从0FF80H开始执行代码。此处有一个分支指令(厂家编程设置的),可以跳转到引导程序的开始地址(0F800H)。这个程序可以在引导之前设置CPU状态寄存器的初始值。中断被全局禁止,OVLY设置为1,程序和数据存取等待时间被设置为7个等待周期,外部内存块被设置为4K的WOROS(16BIT),然后开始程序的引导。 当C5402检测到INT2引脚为高电平、INT3引脚为高电平,即两个引脚都无效时,C5402会转到并行引导方式。并行引导方式是通过扩展的内存接口从数据地址空间读取所需的引导表,再将代码传送到程序存储区。并行引导既支持8位的数据宽度,也支持16位的数据宽度。软件可编程等待寄存器(SWWSR)和块切换控制寄存器(BSCR)都可以在这两种模式中得到设置。 C5402数据存储区、程序存储区和I/O地址空间,用/DS、/PS和/IS三个引脚信号区分。系统的引导表设在数据存储区,考虑到C5402内部只有16K%26;#215;16的双存取RAM(DRAM),因此用于程序加载的EEPROM(EEPROM)中存放的是系统的引导表)可考虑使用28LV256。如果在设计中,使28LV256(+3.3V供电)占用系统的数据空间地址为8000H~0FFFFH,那么,C5402在系统引导时需从系统的数据地址0FFFEH和0FFFFH得到引导表的起始地址8000H。在设计系统引导表时要注意这两个单元的内容。如果设计EEPROM的首地址(系统引导表的首地址)为0C000H,那么数据地址0FFFEH和0FFFFH两个单元要存放C0和00H,也就是引导表的首地址。在设计中也可以使用其它EEPROM或FLASH,如29LE010(128K%26;#215;8BIT),但要正确配置它在系统中的地址。引导表的首地址(即EEPROM的在系统中的首地址)是通过系统数据地址0FFFEH和0FFFFH决定的,可以是08000H~0FFFDH之间的任意地址,但要保证能够存储系统引导表。 2 建立系统引导表的步骤 程序经过仿真器仿真无误以后,就要建立引导表,使系统能够脱机运行。下面介绍建立系统引导表的步骤: (1)编译文件。编写完程序代码以后,对源程序进行编译,生成.obj文件,对于C5402,编译时要采用-V548的编译描述符。 (2)链接文件,将.obj文件生成.out文件。.out文件中应包括初始化的段落。如.text,.const,.cinint等。以上两步在仿真时,也需要执行,以便得到仿真用的.out文件。 (3)使用数制转换工具生成.HEX文件或.BIN文件,C40使用的数据转换工具为hex30.exe,C5402使用数制转换工具编写命令文件,命令文件的编写很重要,下面分别例举了C40和C5402系统引导的两个CMD命令文件。 例1:C40系统引导的CMD文件 myfile.out /*要进行转化的COFF文件名*/ -i /*建立INTEL十六进制文件的输出*/ -image /*产生ROM所指出的内存映射*/ -o n_t_fcom.hex /*输出的文件名*/ -map n_t_hex.map /*输出的MAP文件名*/ -romwidth 8 /*EEPROM的数据宽度*/ -cg 000000000H /*全局数据总线控制字*/ -cl 3e3fbfd0H /*本地数据总线控制字*/ -datawidth 32 /*数据宽度*/ -memwidth 8 /*存储器的宽度*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM的0000H,系统的0030 0000H*/ -ivtp 00700000H /*IVTP指针的初始值*/ -tvtp 00000000H /*TVTP指针的初始值*/ -iack 0300000H /*IACK指令的响应地址*/ -e 00704000H /*程序的开始执行地址*/ ROMS /*ROM的映射范围*/ { EPROM:org=00300000h,len=8000H } 例2:C5402系统引导CMD命令文件 Myfile.out /*要进行转化的COFF文件名*/ -e 0300H /*程序运行的入口点*/ -i /*建立INTEL十六进制文件的输出*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM中引导表的始地址*/ -memwidth 8 /*EEPROM的数据宽度是8位*/ -o myfile.hex /*输出的文件名*/ 下面给出操作符的几点说明: (1)-bootorg指定引导表的地址,注意这里使用的是0000H,.HEX文件的始地址就是0000H。在C40中,EEPROM28C256的0000H地址单元,在系统中地址是0030 0000H。若改为-bootorg 0030 0000H,在用烧录器打开.HEX文件时,可以看到起始地址是0030 0000H,若将.HEX文件烧到EEPROM中,需要修改烧录芯片的起始地址,比较麻烦。但你可以将.HEX文件转化为.BIN文件,则地址就不必修改。 (2)输出文件的格式 -a 输出ASCII码的十六进制文件 -I 输出INTEL十六进制文件 -m1 输出Motrorola的S1数据格式文件 -m2 输出Motorola的S2数据格式文件 -m3 输出Motorola的S3数据格式文件 -t 输出TI的数据格式文件 -x 输出Tektronix数据格式文件 (3)检查.HEX文件正确与否,可以查看MAP映射文件,在.MAP文件里列出了.HEX文件中的一些具体配置。如32BIT数据位的排放顺序,即4个字节的排放顺序;系统引导表的参数:引导表的首地址、程序入口点、各个寄存器的初始值等;源程序中各段的起始地址、大小以及宽度等信息。对照它,就可以确定内存资源是否得到了合理的配置和有无地址冲突。 以下是C40 MAP文件的举例: ********************************************* TMS320C3x/4x Hex Converter Version 5.00 ******************************************** Fri Jun 8 09:47:33 2001 INPUT FILE NAME: OUTPUT FORMAT:Intel PHYSICAL MEMORY PARAMETERS Default data width:32 Default memory width:8(LS-->MS) Default output width:8 BOOT LOADER PARAMETERS Table Address: 00300000,PAGE 0 Entry Point: 00704000 Global Memory Configuration:00000000 Local Memory Configuration: 3e3fbfd0 Interrupt Vector Table Pointer(IVTP):00700000 Trap Vector Table Pointer(TVTP):00000000 IACK Location: 00300000 OUTPUT TRANSLATION MAP ------------------------------------- 00300000..00307fff Page=0 Memory Width=8 ROM Width=8 "EPROM" ------------------------------------- OUTPUT FILES:n_t_fcom.hex [b0..b7] CONTENTS:00300000..003013ff BOOT TABLE intvect:dest=00700000 size=00000040 width=00000004 .text:dest=00704000 size=0000048a width=00000004 .data:dest=00705000 size=00000026 width=00000004 003004f0..00307fff FILL = 00000000 (4)烧录芯片。C40可以直接将生成的INTEL格式的.HEX文件烧到28LV256中。或将十六进制的文件用hexbin.exe转化为二进制的.BIN文件,再烧录到芯片中。对于C5402,还需要手动添加EEPROM在系统中的起始地址。如果采用28LV256(32K%26;#215;8BIT),引导表的首地址为8000H,那么生成的.HEX文件用芯片烧录器加载到烧录器软件的内存后,手动修改28LV256的7FFEH和7FFFH单元(即系统的FFFEH和FFFFH单元)为80和00H,再绕到芯片中。 以上步骤的操作都是在DOS环境中执行的。新版本的DSP开发软件可以在WINDOWS环境中使用,其原理是一样的,这里不再多述。 源程序数据的存储格式(8位并行装载)如表2所示,当烧录时可以对比一下。表2 源程序数据的储存格式 C40引导程序C5402引导程序表格内存宽度(00000008H)32全局数据总线控制字32本地数据总线控制字32第一段的存储空间范围32第一段程序的目的地址32程序代码(1)32……程序代码(N)32……最后一段的存储空间范围32最后一段程序的目的地址32程序代码(1)32……程序代码(N)320000 0000H程序块装载结束标志IVTPTVTPIACK指令的响应地址0030 0000HC8AAH16软件可编程等待状态寄存器的初值SWWSR16块切换控制寄存器的初值BSCR16XPC16PC16第一段的存储空间范围16第一段的目的(XPC)16第一段的目的地址(PC)16程序代码(1)16……程序代码(N)16……最后一段的存储空间范围16最后一段的目的(XPC)16最后一段的目的地址(PC)16程序代码(1)16……程序代码(N)160000(指示引导表格的结束)本文详细介绍了C4X和C54XX两类DSP芯片系统引导的详细设计步骤,其它型号的DSP也大同小异,如C3X与C4X类似。笔者希望通过共享系统引导的经验,使系统引导不再成为DSP设计中的最大障碍,从而加速DSP的抗推广和使用。

2 建立系统引导表的步骤 程序经过仿真器仿真无误以后,就要建立引导表,使系统能够脱机运行。下面介绍建立系统引导表的步骤: (1)编译文件。编写完程序代码以后,对源程序进行编译,生成.obj文件,对于C5402,编译时要采用-V548的编译描述符。 (2)链接文件,将.obj文件生成.out文件。.out文件中应包括初始化的段落。如.text,.const,.cinint等。以上两步在仿真时,也需要执行,以便得到仿真用的.out文件。 (3)使用数制转换工具生成.HEX文件或.BIN文件,C40使用的数据转换工具为hex30.exe,C5402使用数制转换工具编写命令文件,命令文件的编写很重要,下面分别例举了C40和C5402系统引导的两个CMD命令文件。 例1:C40系统引导的CMD文件 myfile.out /*要进行转化的COFF文件名*/ -i /*建立INTEL十六进制文件的输出*/ -image /*产生ROM所指出的内存映射*/ -o n_t_fcom.hex /*输出的文件名*/ -map n_t_hex.map /*输出的MAP文件名*/ -romwidth 8 /*EEPROM的数据宽度*/ -cg 000000000H /*全局数据总线控制字*/ -cl 3e3fbfd0H /*本地数据总线控制字*/ -datawidth 32 /*数据宽度*/ -memwidth 8 /*存储器的宽度*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM的0000H,系统的0030 0000H*/ -ivtp 00700000H /*IVTP指针的初始值*/ -tvtp 00000000H /*TVTP指针的初始值*/ -iack 0300000H /*IACK指令的响应地址*/ -e 00704000H /*程序的开始执行地址*/ ROMS /*ROM的映射范围*/ { EPROM:org=00300000h,len=8000H } 例2:C5402系统引导CMD命令文件 Myfile.out /*要进行转化的COFF文件名*/ -e 0300H /*程序运行的入口点*/ -i /*建立INTEL十六进制文件的输出*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM中引导表的始地址*/ -memwidth 8 /*EEPROM的数据宽度是8位*/ -o myfile.hex /*输出的文件名*/ 下面给出操作符的几点说明: (1)-bootorg指定引导表的地址,注意这里使用的是0000H,.HEX文件的始地址就是0000H。在C40中,EEPROM28C256的0000H地址单元,在系统中地址是0030 0000H。若改为-bootorg 0030 0000H,在用烧录器打开.HEX文件时,可以看到起始地址是0030 0000H,若将.HEX文件烧到EEPROM中,需要修改烧录芯片的起始地址,比较麻烦。但你可以将.HEX文件转化为.BIN文件,则地址就不必修改。 (2)输出文件的格式 -a 输出ASCII码的十六进制文件 -I 输出INTEL十六进制文件 -m1 输出Motrorola的S1数据格式文件 -m2 输出Motorola的S2数据格式文件 -m3 输出Motorola的S3数据格式文件 -t 输出TI的数据格式文件 -x 输出Tektronix数据格式文件 (3)检查.HEX文件正确与否,可以查看MAP映射文件,在.MAP文件里列出了.HEX文件中的一些具体配置。如32BIT数据位的排放顺序,即4个字节的排放顺序;系统引导表的参数:引导表的首地址、程序入口点、各个寄存器的初始值等;源程序中各段的起始地址、大小以及宽度等信息。对照它,就可以确定内存资源是否得到了合理的配置和有无地址冲突。 以下是C40 MAP文件的举例: ********************************************* TMS320C3x/4x Hex Converter Version 5.00 ******************************************** Fri Jun 8 09:47:33 2001 INPUT FILE NAME: OUTPUT FORMAT:Intel PHYSICAL MEMORY PARAMETERS Default data width:32 Default memory width:8(LS-->MS) Default output width:8 BOOT LOADER PARAMETERS Table Address: 00300000,PAGE 0 Entry Point: 00704000 Global Memory Configuration:00000000 Local Memory Configuration: 3e3fbfd0 Interrupt Vector Table Pointer(IVTP):00700000 Trap Vector Table Pointer(TVTP):00000000 IACK Location: 00300000 OUTPUT TRANSLATION MAP ------------------------------------- 00300000..00307fff Page=0 Memory Width=8 ROM Width=8 "EPROM" ------------------------------------- OUTPUT FILES:n_t_fcom.hex [b0..b7] CONTENTS:00300000..003013ff BOOT TABLE intvect:dest=00700000 size=00000040 width=00000004 .text:dest=00704000 size=0000048a width=00000004 .data:dest=00705000 size=00000026 width=00000004 003004f0..00307fff FILL = 00000000 (4)烧录芯片。C40可以直接将生成的INTEL格式的.HEX文件烧到28LV256中。或将十六进制的文件用hexbin.exe转化为二进制的.BIN文件,再烧录到芯片中。对于C5402,还需要手动添加EEPROM在系统中的起始地址。如果采用28LV256(32K%26;#215;8BIT),引导表的首地址为8000H,那么生成的.HEX文件用芯片烧录器加载到烧录器软件的内存后,手动修改28LV256的7FFEH和7FFFH单元(即系统的FFFEH和FFFFH单元)为80和00H,再绕到芯片中。 以上步骤的操作都是在DOS环境中执行的。新版本的DSP开发软件可以在WINDOWS环境中使用,其原理是一样的,这里不再多述。 源程序数据的存储格式(8位并行装载)如表2所示,当烧录时可以对比一下。表2 源程序数据的储存格式 C40引导程序C5402引导程序表格内存宽度(00000008H)32全局数据总线控制字32本地数据总线控制字32第一段的存储空间范围32第一段程序的目的地址32程序代码(1)32……程序代码(N)32……最后一段的存储空间范围32最后一段程序的目的地址32程序代码(1)32……程序代码(N)320000 0000H程序块装载结束标志IVTPTVTPIACK指令的响应地址0030 0000HC8AAH16软件可编程等待状态寄存器的初值SWWSR16块切换控制寄存器的初值BSCR16XPC16PC16第一段的存储空间范围16第一段的目的(XPC)16第一段的目的地址(PC)16程序代码(1)16……程序代码(N)16……最后一段的存储空间范围16最后一段的目的(XPC)16最后一段的目的地址(PC)16程序代码(1)16……程序代码(N)160000(指示引导表格的结束)本文详细介绍了C4X和C54XX两类DSP芯片系统引导的详细设计步骤,其它型号的DSP也大同小异,如C3X与C4X类似。笔者希望通过共享系统引导的经验,使系统引导不再成为DSP设计中的最大障碍,从而加速DSP的抗推广和使用。

2 建立系统引导表的步骤 程序经过仿真器仿真无误以后,就要建立引导表,使系统能够脱机运行。下面介绍建立系统引导表的步骤: (1)编译文件。编写完程序代码以后,对源程序进行编译,生成.obj文件,对于C5402,编译时要采用-V548的编译描述符。 (2)链接文件,将.obj文件生成.out文件。.out文件中应包括初始化的段落。如.text,.const,.cinint等。以上两步在仿真时,也需要执行,以便得到仿真用的.out文件。 (3)使用数制转换工具生成.HEX文件或.BIN文件,C40使用的数据转换工具为hex30.exe,C5402使用数制转换工具编写命令文件,命令文件的编写很重要,下面分别例举了C40和C5402系统引导的两个CMD命令文件。 例1:C40系统引导的CMD文件 myfile.out /*要进行转化的COFF文件名*/ -i /*建立INTEL十六进制文件的输出*/ -image /*产生ROM所指出的内存映射*/ -o n_t_fcom.hex /*输出的文件名*/ -map n_t_hex.map /*输出的MAP文件名*/ -romwidth 8 /*EEPROM的数据宽度*/ -cg 000000000H /*全局数据总线控制字*/ -cl 3e3fbfd0H /*本地数据总线控制字*/ -datawidth 32 /*数据宽度*/ -memwidth 8 /*存储器的宽度*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM的0000H,系统的0030 0000H*/ -ivtp 00700000H /*IVTP指针的初始值*/ -tvtp 00000000H /*TVTP指针的初始值*/ -iack 0300000H /*IACK指令的响应地址*/ -e 00704000H /*程序的开始执行地址*/ ROMS /*ROM的映射范围*/ { EPROM:org=00300000h,len=8000H } 例2:C5402系统引导CMD命令文件 Myfile.out /*要进行转化的COFF文件名*/ -e 0300H /*程序运行的入口点*/ -i /*建立INTEL十六进制文件的输出*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM中引导表的始地址*/ -memwidth 8 /*EEPROM的数据宽度是8位*/ -o myfile.hex /*输出的文件名*/ 下面给出操作符的几点说明: (1)-bootorg指定引导表的地址,注意这里使用的是0000H,.HEX文件的始地址就是0000H。在C40中,EEPROM28C256的0000H地址单元,在系统中地址是0030 0000H。若改为-bootorg 0030 0000H,在用烧录器打开.HEX文件时,可以看到起始地址是0030 0000H,若将.HEX文件烧到EEPROM中,需要修改烧录芯片的起始地址,比较麻烦。但你可以将.HEX文件转化为.BIN文件,则地址就不必修改。 (2)输出文件的格式 -a 输出ASCII码的十六进制文件 -I 输出INTEL十六进制文件 -m1 输出Motrorola的S1数据格式文件 -m2 输出Motorola的S2数据格式文件 -m3 输出Motorola的S3数据格式文件 -t 输出TI的数据格式文件 -x 输出Tektronix数据格式文件 (3)检查.HEX文件正确与否,可以查看MAP映射文件,在.MAP文件里列出了.HEX文件中的一些具体配置。如32BIT数据位的排放顺序,即4个字节的排放顺序;系统引导表的参数:引导表的首地址、程序入口点、各个寄存器的初始值等;源程序中各段的起始地址、大小以及宽度等信息。对照它,就可以确定内存资源是否得到了合理的配置和有无地址冲突。 以下是C40 MAP文件的举例: ********************************************* TMS320C3x/4x Hex Converter Version 5.00 ******************************************** Fri Jun 8 09:47:33 2001 INPUT FILE NAME:

2 建立系统引导表的步骤 程序经过仿真器仿真无误以后,就要建立引导表,使系统能够脱机运行。下面介绍建立系统引导表的步骤: (1)编译文件。编写完程序代码以后,对源程序进行编译,生成.obj文件,对于C5402,编译时要采用-V548的编译描述符。 (2)链接文件,将.obj文件生成.out文件。.out文件中应包括初始化的段落。如.text,.const,.cinint等。以上两步在仿真时,也需要执行,以便得到仿真用的.out文件。 (3)使用数制转换工具生成.HEX文件或.BIN文件,C40使用的数据转换工具为hex30.exe,C5402使用数制转换工具编写命令文件,命令文件的编写很重要,下面分别例举了C40和C5402系统引导的两个CMD命令文件。 例1:C40系统引导的CMD文件 myfile.out /*要进行转化的COFF文件名*/ -i /*建立INTEL十六进制文件的输出*/ -image /*产生ROM所指出的内存映射*/ -o n_t_fcom.hex /*输出的文件名*/ -map n_t_hex.map /*输出的MAP文件名*/ -romwidth 8 /*EEPROM的数据宽度*/ -cg 000000000H /*全局数据总线控制字*/ -cl 3e3fbfd0H /*本地数据总线控制字*/ -datawidth 32 /*数据宽度*/ -memwidth 8 /*存储器的宽度*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM的0000H,系统的0030 0000H*/ -ivtp 00700000H /*IVTP指针的初始值*/ -tvtp 00000000H /*TVTP指针的初始值*/ -iack 0300000H /*IACK指令的响应地址*/ -e 00704000H /*程序的开始执行地址*/ ROMS /*ROM的映射范围*/ { EPROM:org=00300000h,len=8000H } 例2:C5402系统引导CMD命令文件 Myfile.out /*要进行转化的COFF文件名*/ -e 0300H /*程序运行的入口点*/ -i /*建立INTEL十六进制文件的输出*/ -boot /*将所有的输入文件创建引导表*/ -bootorg 0000H /*EPROM中引导表的始地址*/ -memwidth 8 /*EEPROM的数据宽度是8位*/ -o myfile.hex /*输出的文件名*/ 下面给出操作符的几点说明: (1)-bootorg指定引导表的地址,注意这里使用的是0000H,.HEX文件的始地址就是0000H。在C40中,EEPROM28C256的0000H地址单元,在系统中地址是0030 0000H。若改为-bootorg 0030 0000H,在用烧录器打开.HEX文件时,可以看到起始地址是0030 0000H,若将.HEX文件烧到EEPROM中,需要修改烧录芯片的起始地址,比较麻烦。但你可以将.HEX文件转化为.BIN文件,则地址就不必修改。 (2)输出文件的格式 -a 输出ASCII码的十六进制文件 -I 输出INTEL十六进制文件 -m1 输出Motrorola的S1数据格式文件 -m2 输出Motorola的S2数据格式文件 -m3 输出Motorola的S3数据格式文件 -t 输出TI的数据格式文件 -x 输出Tektronix数据格式文件 (3)检查.HEX文件正确与否,可以查看MAP映射文件,在.MAP文件里列出了.HEX文件中的一些具体配置。如32BIT数据位的排放顺序,即4个字节的排放顺序;系统引导表的参数:引导表的首地址、程序入口点、各个寄存器的初始值等;源程序中各段的起始地址、大小以及宽度等信息。对照它,就可以确定内存资源是否得到了合理的配置和有无地址冲突。 以下是C40 MAP文件的举例: ********************************************* TMS320C3x/4x Hex Converter Version 5.00 ******************************************** Fri Jun 8 09:47:33 2001 INPUT FILE NAME:

评论