CoolRunner-Ⅱ器件的微处理器接口逻辑

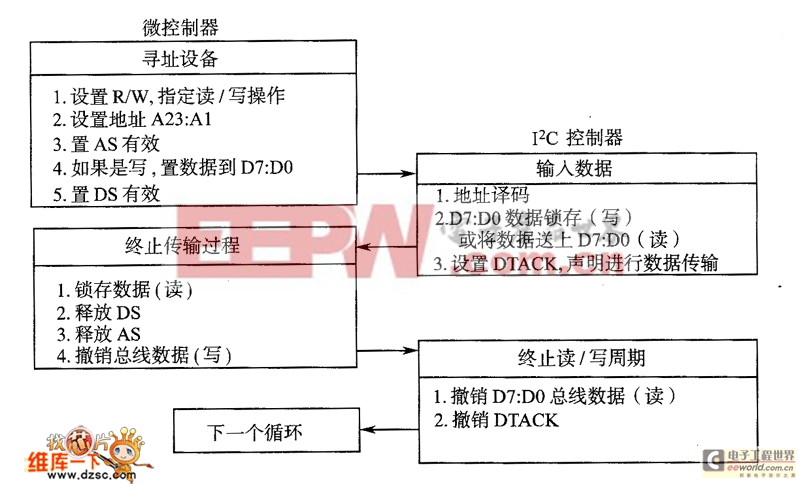

如图 uC与I2C之间的交互流程

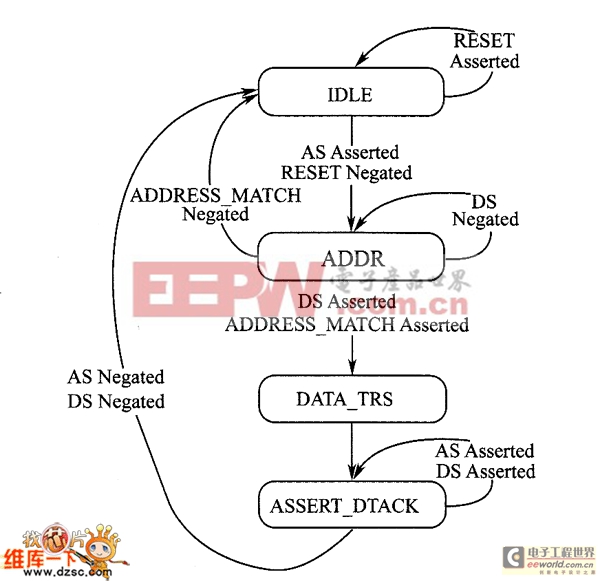

uC总线协议在Coo1Runner-Ⅱ中是由一个状态机实现的,如图2所示。

在空闲状态,微控制器将地址送上地址总经,并设置R_W、AS和DS状态。如果在定周期,微控制器也会将待写数据送上数据总线。AS有效表示地址总线上的地址有效,DS有效表示数据总线上数据有效;如果是在读周期,微控制器驱动数据总线为三态。同样,AS有效表示地址总线上的地址有效,但是DS有效表示I2C控制器可以将数据送到数据总线。

图2 uC总线接口状态机

在AS有效的情况下,I2C控制器状态进入ADDR状态。在此状态,一方面进行地址译码;另一方面将判断此设备是不是被寻址的设备,并使能内部寄存器。如果被寻址的是CoolRunner-Ⅱ I2C设备,并且DS有效,则I2C控制器将进入DATA_TRS状态。如果是读操作,被请求的数据会被送到数据总线;如果是写操作,则数据总线上的数据被锁存在内部被寻址的寄存器中,CoolRunner-II I2C设备自动进入ASSERT_DTACK状态,DTACK有效。读操作时表示总线上数据准各好,写操作时表示数据已经被接收到。

在DTACK有效的情况下,写操作时,uC将撤销数据;读操作时,uC锁存总线上的数据。R_W信号线被置为读,并且释放AS和DS,表明数据传输完毕。AS和DS的释放会促使CoolRunner-II I2C控制器释放DTACK,状态机进入IDLE状态。

评论