用双MicroBlaze监控汽车应用

基于软核处理器的多处理器片上系统(MPSoC)设计正日益风靡于嵌入式系统设计领域。为了向多个处理器提供一致的数据,存储区架构和管理已成为设计工作中非常重要的组成部分。在原型汽车应用中,我们准备构建一个双MicroBlaze系统,用于在两个MicroBlaze上支持赛灵思(Xilinx)公司嵌入式处理器内核Xilkernel。

在开发自主汽车原型转向平台前,我们根据Xilinx技术规范、参考设计和双处理器设计套件,研究出一套通用的设计工作流和工艺。该设计结合了多种功能,比如:防碰撞、行车道检测和自动停放。Xilkernel设计提供了诸如Posix线程这样的库函数,可重复利用基于QNX的防碰撞应用以及对其进行分割。

紧密连接

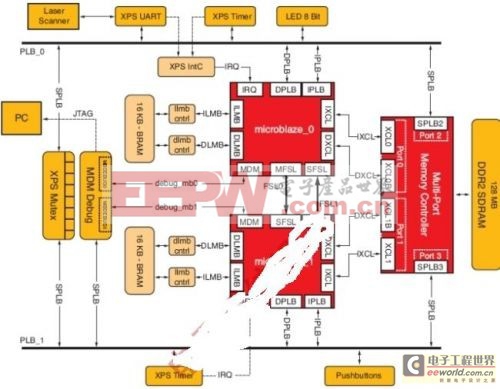

我们构建了一个紧密连接的处理器系统,内含两个配置完全相同的MicroBlaze处理器,在Harvard架构中,每个处理器都与一个16KB的局部块RAM(BRAM)相连(图1)。另外,这两个处理器还与一个128MB的DDR存储器模块相连,用于存储代码和数据交换。Xilinx平台工作室(XPS)Mutex内核负责对两个MicroBlaze共享的存储器访问进行同步。两个处理器还能通过一对快速单工链路(FSL)直接通信,FSL支持主/从和流水线处理器设计概念。采用FSL实现这两个MicroBlaze的互联,而不采用XPS Mailbox实现,可以提高性能,并降低资源耗用。

图1:面向XtremeDSP开发平台的双MicroBlaze Xilkernel配置。

两个定时器外设负责为Xilkernel的调度实现提供中断源。开发阶段的第一步,我们通过UART接口将激光扫描仪连接到系统,为防碰撞系统提供目标检测。为以中断控制器而非直接连接的时钟中断部署Xilkernel,我们在板支持包(BSP)设置中调整了与Xilkernel相关的参数sysintc_spec。

我们把两个MicroBlaze连接到MicroBlaze调试模块进行调试,并通过microblaze_1的JTAG UART输出ST.DIO。我们分析了系统的两种实现方案,一种用XtremeDSP开发平台搭配Spartan-3A DSP 1800A FPGA,另一种用ML605评估板搭配Virtex-6 XC6VLX240T FPGA。

存储器和高速缓存架构

多端口存储器控制器(MPMC)通过Xilinx缓存链路(XCL)将Microblaze与外部DDR2存储器相连,并分配直接存储访问。由于采用统一的存储器架构,每个处理器具有相同的存储延迟和访问方式。我们为每个MicroBlaze配置了8KB指令和8KB数据缓存,均连接到单一MPMC PIM。这种布线方式可以让我们将最多8个MicroBlaze关联到一个MPMC。

单一MPMC地址总线连接和数据总线连接,会导致MPMC与外部存储器之间出现数据流和取指瓶颈。但内部的时间片轮转仲裁,能够保证所有请求都能顺序访问存储器。另外,MicroBlaze还能通过处理器局部总线(PLB)保持与MPMC的连接,以提供对无缓存共享存储区的访问。

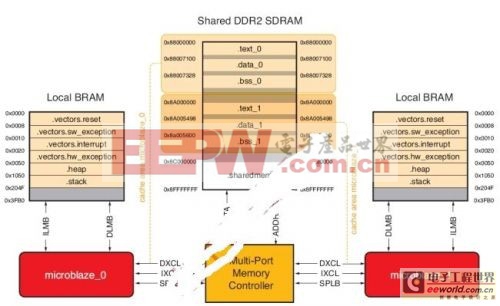

在多处理器环境中,确保数据高速缓存的一致性非常重要。因此,我们将外部存储的地址范围分为三段(图2)。每个MicroBlaze占有自己的地址空间,而只有数据存储在其特定的区域,XCL才会缓存数据。第三个地址空间提供一个独立段,可通过PLB访问,而用于交换未缓存的共享数据。通过在链接脚本中预定义变量,软件工程师可以得到一个指向该段基址的指针。我们用写通策略配置高速缓存,因为如果采用回写策略,处理多个写访问会导致更多延迟。

图2:DMX系统的内存印象图。

连接器脚本的配置

连接器脚本的作用是,根据硬件设计信息,正确的板支持包和软件应用本身,来定义处理器系统的存储分段。XPS工具负责为每个MicroBlaze的复位、中断和异常向量分配固定段,这些向量将存储在处理器的BRAM中。常用的方法是把.heap和.stack段也存储在局部BRAM中,以便在执行线程的时候快速访问局部变量。

评论