基于Avalon总线接口的UPFC控制器IP核设计

0 引言

统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不至于过负荷。控制系统是UPFC的核心部分,它的主要功能是监测交流电网的传输和控制输出逆变波形,不但能使输出波形的频率跟定电网频率,而且可对输出波形的幅值和相位进行调节。

随着微电子技术的不断发展,各种新器件和新的设计方法不断出现,使得UPFC的控制系统设计也在不断发展。近年来,随着IC集成度的不断提高而出现的现场可编程逻辑阵列(FieldProgrammable Gate Array,简称FPGA)就是由可编程逻辑器件PLD(Programmable Logic Device)发展而来的新型器件,FPGA不但可以用于单个控制器件,而且可以用于整个系统。因而又诞生了一种新的系统设计方法――片上可编程系统SOPC(System on a Programmer ChIP)。这是一种基于IP核(Intellectual Property core)的新系统。它既具有软件的灵活性,又同时具有硬件的处理速度,更重要的是,它可以和微处理器软核等IP核构成整个系统,还可以根据需要对该系统进行重新设计,从而提高系统的灵活性、可靠性,以及抗干扰能力。本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

1 UPFC控制器IP的主要功能

UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波形数据和3路相位分别相差2π/3的三角载波波形数据。由于UPFC控制系统采用SPWM调制技术,所以要求UPFC控制器IP输出的正弦波频率应跟电网频率保持一致,输出的正弦波幅值和相位可以根据需要进行调节;而输出的三角载波频率、幅值和相位则保持不变。

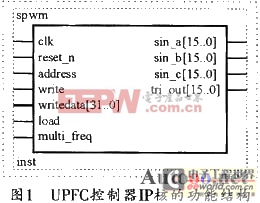

UPFC控制器IP核主要基于Avalon总线接口,其结构如图1所示。它有7种输入信号和2组输出信号。其中输入信号分别为时钟信号clk、低有效复位信号reset_n、地址信号address、高有效写信号write、32位的数据信号writedata[31..0]、同步信号load、激励信号multi_freq等;输出信号主要是三路相位分别相差2π/3的正弦波(sin_a,sin_b,sin_c)和1路三角载波(tri_out)。

2 IP核结构

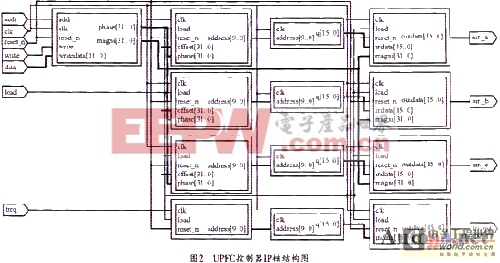

UPFC控制器的IP核主要由以下6个模块构成:设置正弦波幅值和相位模块,正弦波寻址模块,正弦波数据查找模块,正弦幅值计算模块,三角波寻址模块和三角波数据查找模块。图2是利用uartus工具对其进行综合后的RTL整体结构图。

由于正弦波和三角波都是通过查找预先存储在ROM表中的数据来实现相应的波形;唯一不同的是正弦波的频率跟电网频率保持一致,幅值和相位可以根据需要进行调节,而三角载波的频率、幅值和相位保持不变。鉴于实现三角波形相对简单。下面主要阐述正弦波寻址模块、正弦波数据查找模块和正弦幅值计算模块的实现方法。

2.1 正弦波幅值和相位模块

UPFC控制器IP核含有相位寄存器、幅值寄存器以及3个相位偏移参数。其中相位寄存器主要用于保存设置的初始相位值,它的实际变化范围为0~719。幅值寄存器则用于保存设置幅值相对于存储波形幅值的变化量,它的变化范围为0~64。相位偏移参数是指某一路正弦波在初始相位为0时,相对标准正弦波的相位偏移量,流量通常是个常量,分别为0、2π/3、4π/3。

2.2 正弦波寻址模块

要使输出的正弦波的频率跟电网频率fe保持一致,可通过锁相环PLL把电网频率fe倍频720倍后作为正弦波输出的激励信号feq。虽然Altera的Cyclone系列也带有PLL,但是它的PLL功能非常有限。由于它只能对固定频率信号进行一定的倍频,而不能对变化的频率信号在一定范围内任意倍频。所以必须用模拟锁相环PLL把电网频率fe倍频后作为UPFC控制器IP核的multi_freq输入信号。当电网频率fe的第一个上升沿到来时,load为高电平,此后UPFC控制器IP核开始计算正弦波的地址。正弦波的地址等于电网频率fe个数的累加值与相位寄存器、相位偏移参数之和。下面为其实现的伪代码:

2.3 正弦波数据查找模块

正弦波数据查找模块由正弦信号发生器和正弦数据存储器ROM构成。构成ROM的初始化数据文件有两种格式:Memory Initialization File(.mif)和Hexadecimal (Intel-Formal)File (.hex),应用时可选其中任意一种。但设计之前必须考虑所用FPGA片上ROM的大小,同时也要考虑输出数据的分辨率。因为UPFC控制器IP核的地址变化范围为0~719,输出的波形数据是16位,所以正弦数据ROM应由720个16位数据构成。

为了输出数据的分辨率,同时也为了能使正弦波的幅值得到调整,必须预先存储一组合适的正弦波形数据。选取的正弦波形函数为:

f(x)=1023×[sin(πx/360)+1]/2

正弦波的数值可在0~1023中变化。在设计正弦信号发生器时,可以利用Quartus提供的MegaWizard。Plug -In Manage工具提供的LPM_ROM来定制正弦信号数据ROM宏功能块,然后将其在上层文件中实例化。

2.4 正弦波幅值计算模块

由于定制的正弦数据存储器ROM的最大数据是1023,即只占用了10位数据宽度,还有6位数据宽度用于调节正弦波形的幅值。正弦波形的幅值最大调节量是其选择波形的64倍。实际上,输出正弦波形的数据等于查找到的正弦信号数据与幅值寄存器的乘积。虽然Verilog语言提供了乘法功能,但是它在有的综合器中是不能被综合的,所以必须自己设计一个乘法器。该乘法器同样可以利用MegaWizard Plug-In Manage工具提供的LPM_MULT来定制一个16×16的乘法器。

评论