基于多环锁相宽带细步进频率合成器的设计

1 多环锁相宽带频综设计原理

1.1 单环锁相频率合成器

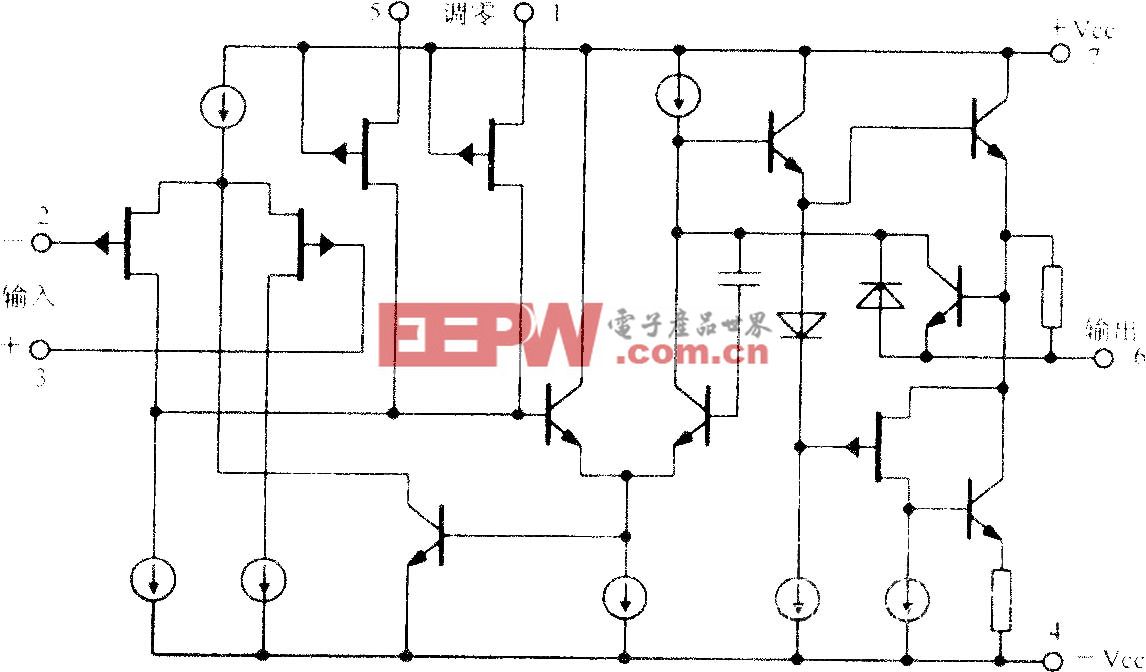

锁相环(PLL)是一个负反馈的相位控制系统,基本的锁相环路包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可变分频器几个基本部分组成。其原理图如图1所示。

式中,PNSYNTH为频率合成器带内相位噪声,PNTOT为锁相环芯片底噪。

为保证能够得到较高的频率分辨率,一般只能通过降低鉴相频率实现,造成N值加大,由(1)式可知,相位噪声将恶化。因此,对于单环锁相频率合成器,相位噪声和频率分辨率是相互制约的指标。

1.2 直接数字频率合成器

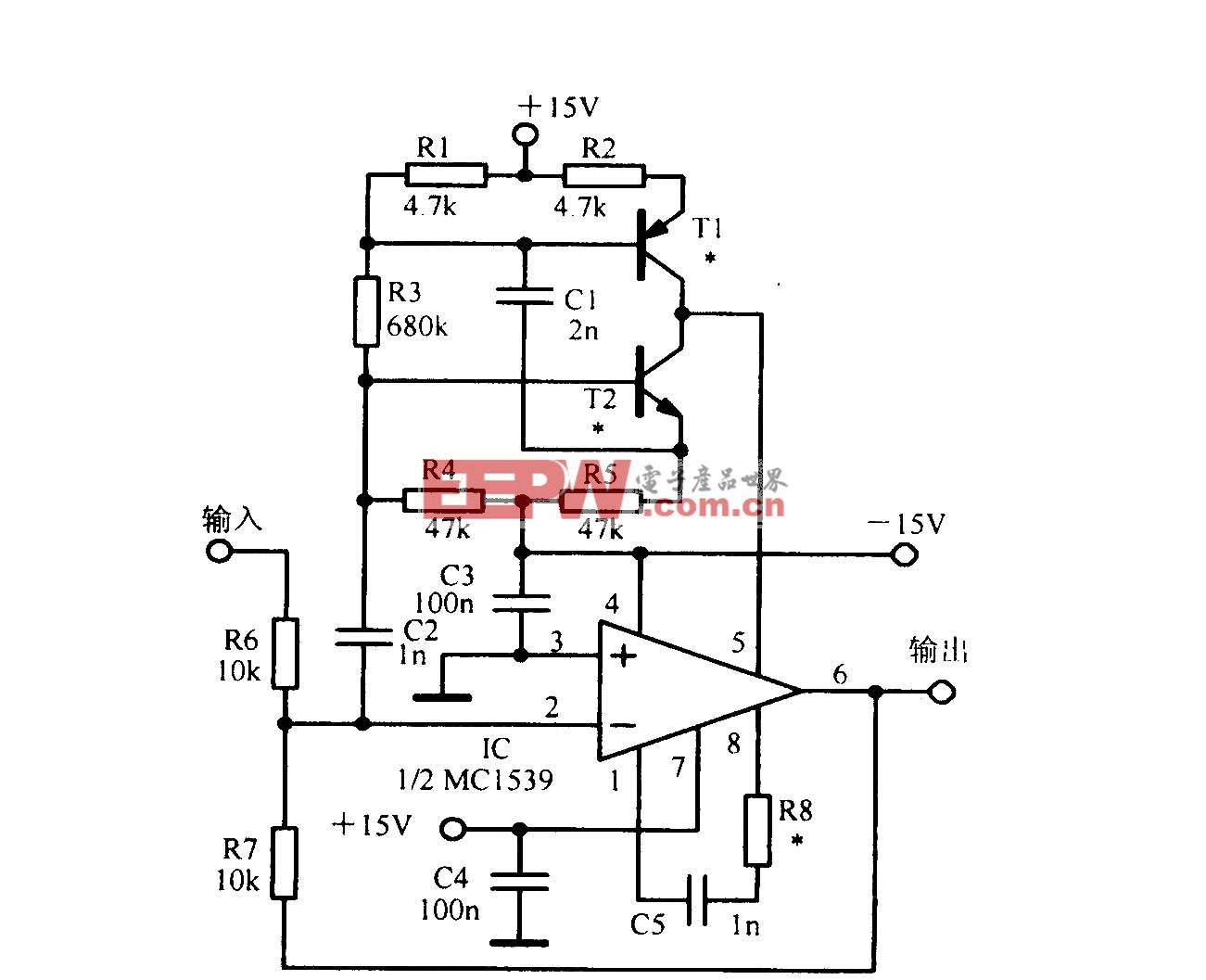

直接数字频率合成器(DDS)由相位累加器,波形存储器,数模转换器,低通滤波器和参考时钟五部分,如图2所示。在参考时钟的控制下,相位累加器对频率控制字K进行线性累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,进过数模变换器得到相对应的阶梯波,最后经低通滤波器得到连续变化的所需频率的波形。

DDS利用了相位反馈控制原理控制频率输出,不需要外部辅助频率捕获,易于集成,可实现很高的频率分辨率,但是工作频率有限,杂散水平较难控制。因此,将PLL和DDS组合起来,综合运用两者的优势,可以既保证高频率输出,又能实现很高的频率分辨率。

1.3 多环锁相频率合成器

多环锁相频率合成器有多种组成结构,包括PLL组合、DDS+PLL等,其中DDS+PLL的结构因频率分辨率高和低相噪等优点,应用最为广泛。本文中选用的实现结构的设计思想是,利用DDS产生基带信号,经与PLL两次混频扩频,产生宽频带的高分辨率参考信号,进入锁相环倍频拓宽输出频率范围,同时利用的PLL良好的窄带载波跟踪特性对DDS参考信号的杂散分量进行跟踪滤波器,最终实现低相噪宽带细步进频综输出。

2 多环锁相宽带频综设计方案

2.1 设计目标

下面以1个工程实例为目标,介绍基于DDS+PLL多环锁相技术设计宽带频综的工作原理。该工程实例的主要技术指标要求为:

输出频率:10~13 GHz;

频率步进:10 kHz;

输出功率:>12d Bm;

相位噪声:≤-90 dBc/Hz@1 kHz;

≤-90 dBc/Hz@10 kHz;

谐波抑制:-15 dBc;

杂散抑制:-65 dBc;

2.2 设计方案

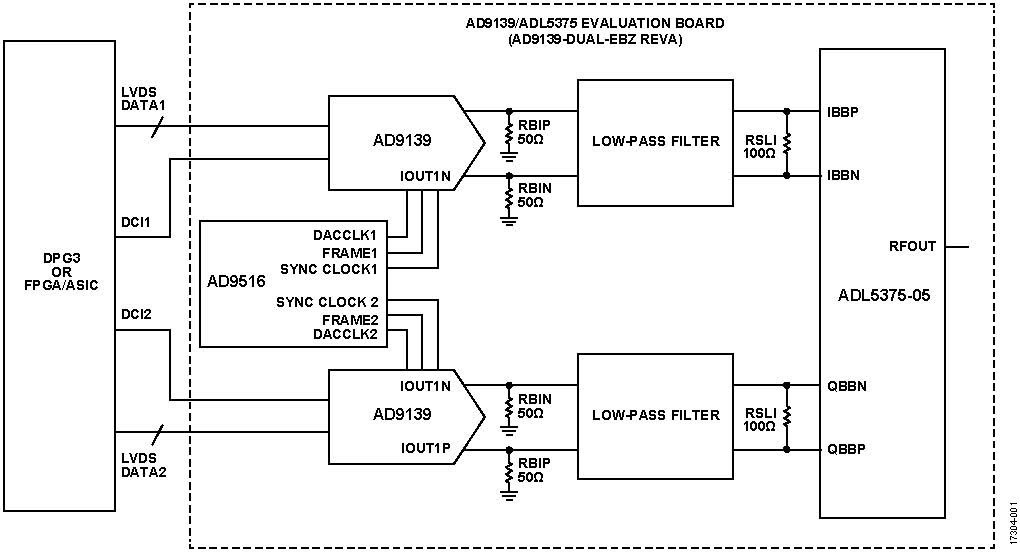

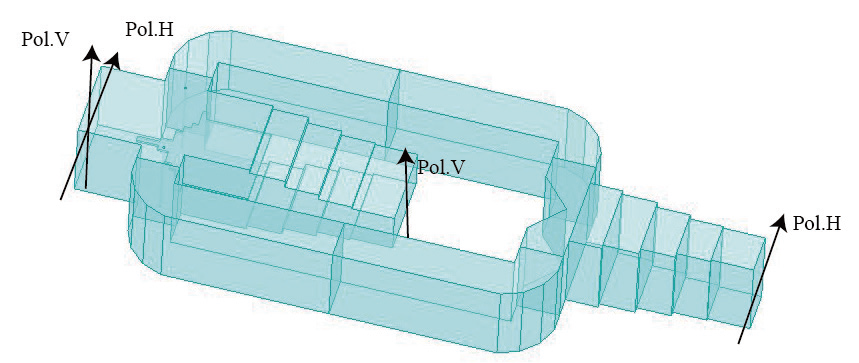

经分析,同时满足细频率步进和低相位噪声、低杂散是设计难点。文中采用DDS+PLL多环锁相频率合成技术实现,工作原理如图3所示。

这是由多个锁相环组成的电路结构。环路A为直接数字频率合成环路,主要功能是产生步进细调的频综基带,通过DDS产生步进10 kHz、带宽100 MHz的基带频率信号;环路B为锁相点频源,产生S波段低相噪点频,通过与DDS信号混频,把细步进基带频谱搬移到S波段,带宽不变;环路C为锁相频综,产生L波段步进100 MHz的大步进频综,与第一级混频输出信号再次混频,将窄带细步进信号扩频,输出带宽可大幅提高。环路D为通过锁相倍频N倍,实现X波段的宽带细步进频综输出。输出信号与各功能环输出信号的关系为:

fout=[(fDDS+fLO1)-fLO2]xN (2)

该多环电路结构的主要优点是通过对DDS基带信号的多级混频,最终实现了宽频段细步进的覆盖。同时,通过合理的频段分配,将各个锁相环路的倍频次数N控制在相对较低的水平,使相位噪声的恶化量较小,保证了各个锁相环及最终输出信号相位噪声的良好水平。

输出信号的相位噪声由单环A、B、C的相位噪声和锁相倍频环D的倍频次数决定。A、B、C环中,输出相位噪声由输出频率最高的B环(输出频率3.6 GHz)决定。鉴相器底噪为-233 dBc/Hz@10 kHz,鉴相频率100 MHz,反馈分频比N=3 600/100=36,根据(1)式可以估算,B环输出信号相位噪声为-233+10lg(100x106)+20lg72=-120 dBc(离载波10 kHz处)。环路D最大倍频次数约为6,最终输出相位噪声为-120dBc+20lg6=-104 dBc/Hz。考虑闪烁噪声和电路中其他器件热噪声及工程实现性,实际信号输出满足-90 dBc/Hz@1 kHz@10 kHz的指标要求。

3 多环锁相宽带频综的电路设计与仿真

3.1 DDS电路设计

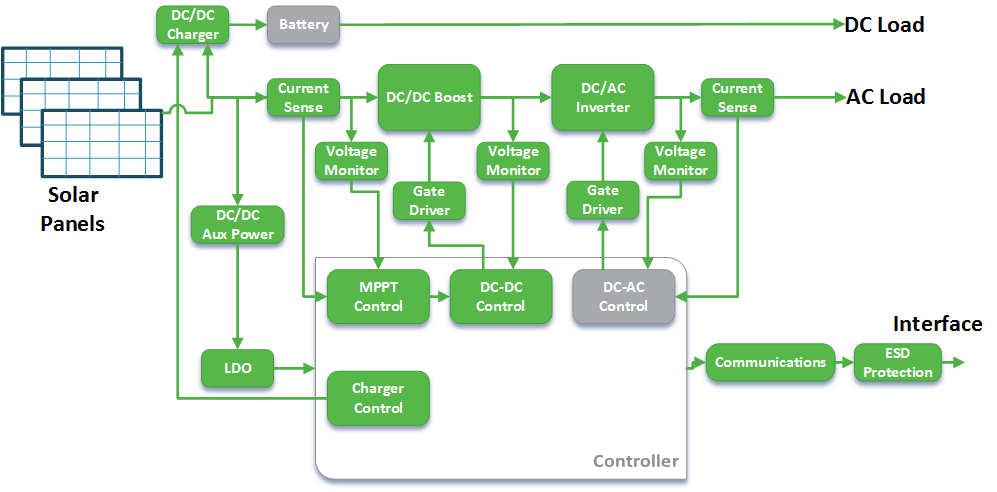

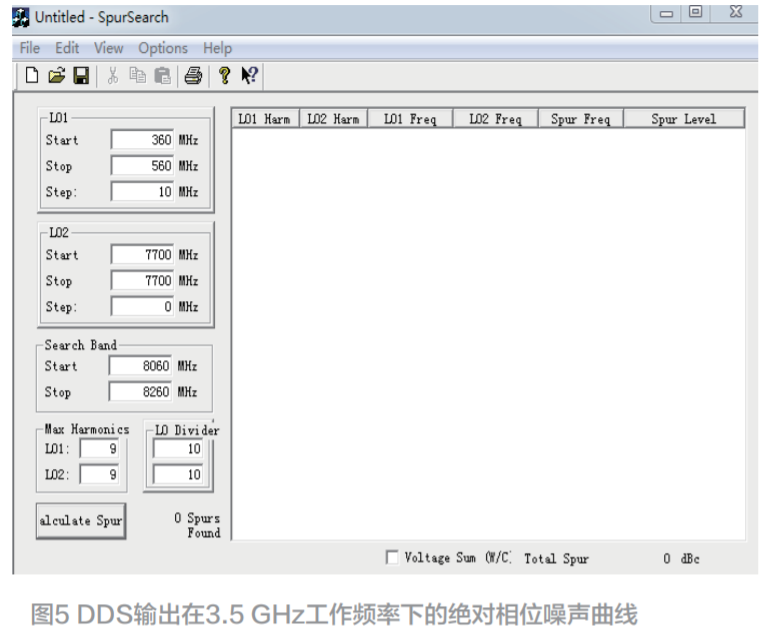

环路A采用了采用高性能DDS芯片AD9912。AD9912内置14 bit DAC;支持高达1GPS的采样速率;采用1.8 V和3.3 V电源供电,在器件性能大幅提高的前提下也极大地降低了器件功耗;能够生成高达400 MHz的捷变频率正弦波形,最高频率分辨率达到4μHz。目前AD9912已广泛用于频率合成器、时钟发生器、雷达以及各类测量装置等。

在环路A的设计中,100 MHz参考信号通过锁相环倍频至1 GHz,提供DDS参考时钟,在频率控制码控制下实现细步进基带输出。

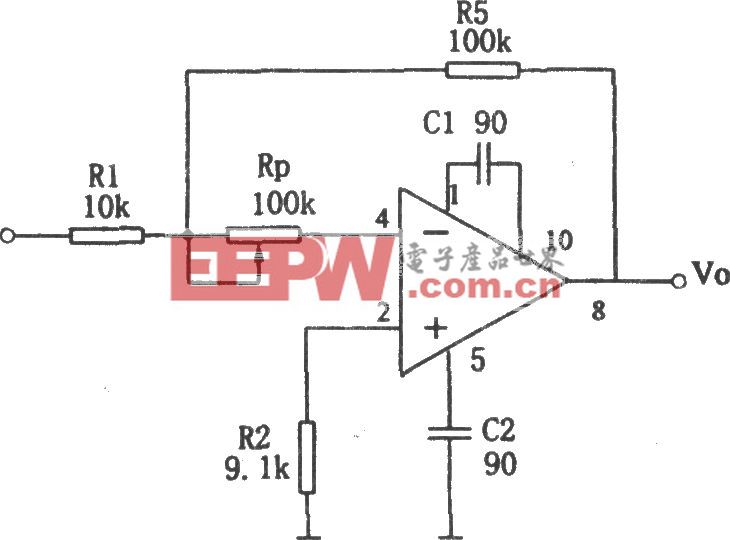

3.2 锁相环电路设计

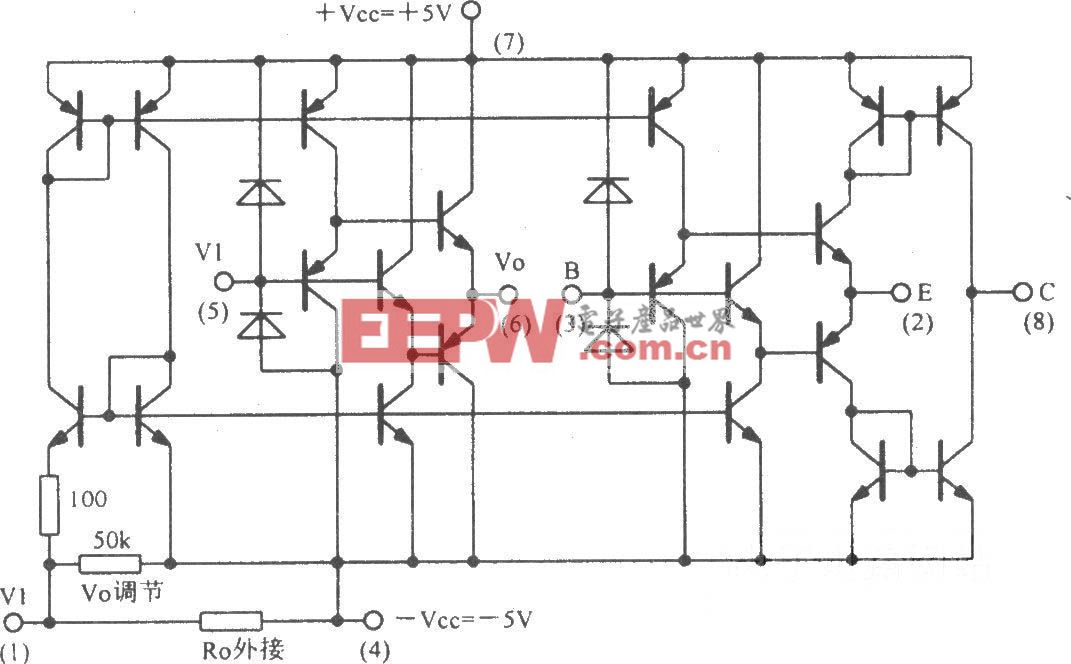

锁相环路B、C采用了HITTITE公司的数字锁相环芯片HMC440。该芯片具有很低噪声基底(-233 dBc/Hz@10kHz)和很高的鉴相频率(1 300 MHz),集成5 bit数控程序分频器,在本方案中的环路B、C使用,用于产生超低相位噪声的fLO1和fLO2。

dc相关文章:dc是什么

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理

鉴相器相关文章:鉴相器原理

锁相环相关文章:锁相环原理

锁相放大器相关文章:锁相放大器原理

评论