高速ADC电源设计方案

当今电子业界的时髦概念是新设计在降低成本的同时还要“绿色环保”。具体到便携式应用,它要求降低功耗、简化散热管理、最大化电源效率并延长电池使用时间。然而,大多数ADC的数据手册建议使用线性电源,因为其噪声低于开关电源。这在某些情况下可能确实如此,但新的技术进步已经证明,开关电源也可以用于通信和医疗应用。

本文介绍对于了解高速ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使ADC实现预期性能,有两种测试十分有用:一般称为电源抑制比(PSRR)和电源调制比(PSMR)。

何谓电源抑制

当供电轨上有噪声时,决定ADC性能的因素主要有两个,它们是PSRR-dc、PSRR-ac和PSMR。PSRR-dc指电源电压的变化与由此产生的ADC增益或失调误差的变化之比值,它可以用最低有效位(LSB)的分数、百分比或对数dB (PSR = 20 × log10 (PSRR))来表示,通常规定采用直流条件。

但是,这种方法只能揭示ADC的一个额定参数随电源电压可能会如何变化,因此无法证明转换器的稳定性。更好的方法是在直流电源之上施加一个交流信号,然后测试电源抑制性能(PSRR-ac),从而主动通过转换器电路耦合信号(噪声源)。这种方法本质上是对转换器进行衰减,将其自身表现为杂散(噪声),它会以某一给定幅度提升至超过转换器的噪声基底值。其意义是表明在注入噪声和幅度给定的条件下转换器何时会崩溃。同时,这也能让设计人员了解到多大的电源噪声会影响信号或加入到信号中。PSMR则以不同的方式影响转换器,它表明当与施加的模拟输入信号进行调制时,转换器对电源噪声影响的敏感度。这种影响表现为施加于转换器的IF频率附近的调制,如果电源设计不严谨,它可能会严重破坏载波边带。

总之,电源噪声应当像转换器的任何其它输入一样进行测试和处理。用户必须了解系统电源噪声,否则电源噪声会提高转换器噪声基底,限制整个系统的动态范围。

电源测试

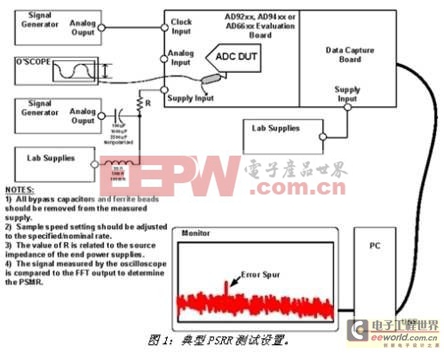

图1所示为在系统板上测量ADC PSRR的设置。分别测量每个电源,以便更好地了解当一个交流信号施加于待测电源之上时,ADC的动态特性。开始时使用一个高容值电容,例如100uF非极化电解质电容。采用1mH的电感来充当直流电源的交流阻断器,一般将它称为“偏置-T”,可以购买采用连接器式封装的产品。

使用示波器测量交流信号的幅度,将一个示波器探针放在电源进入待测ADC的电源引脚上。为简化起见,将施加于电源上的交

评论