挑战更低待机功耗,NXP专家来支招

节能减排已经成为全球的大趋势,在这一个趋势下,现在,除了把电子设备运行时的功耗降低外,标准组织、半导体厂商也在把电子设备的待机功耗进一步,以节省更多的能耗和资金,数年前,如果说要将电子设备待机个功耗降低到几十毫瓦,很多人会你认为是疯狂的想法,而现在这已经成为现实,而且,实际上,这还有进一步降低的空间,近日,恩智浦半导体资深产品市场经理张锡亮分享了降低功耗的四个重要举措。

待机功耗=惊人的浪费

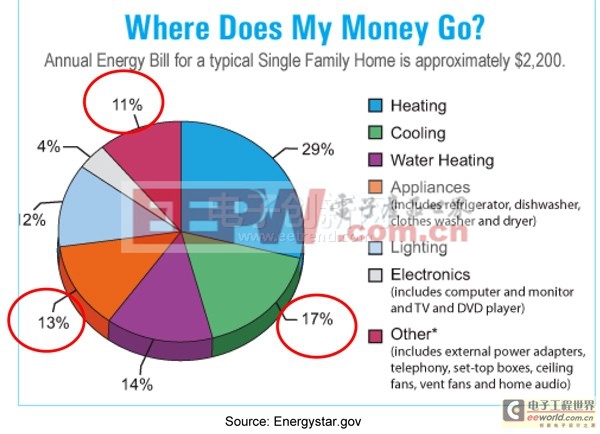

据张锡亮介绍,数据显示,平均下来,每个家庭每年仅在制冷、白家电、小家电等方面的支出就占到了40%左右,从待机功耗上测试,家庭电视机顶盒在一天待机状态下的耗电量为0.131度,一个月按照30天算就是3.93度电,一年按365天算就是47.82度电,按照目前一度电0.52元计算,一年将多支出电费24.87元。

如果按每个笔记本每天待机功耗0.5W计算,每年消耗的电能和资金就是

200M*0.5W*365*24=876,000M Wattage/Hour=876M度=4,380MNT$=931.9MRMB=9亿3千万人民币!

如果按每个手机充电器待机功耗0.3W来计算,每年都消耗就是:

1500M*0.3W*365*24=3,942,000M wattage/hour =3,942M度=19,710MNT$=4,194MRMB=41亿9千万人民币

可见待机功耗造成的浪费是非常惊人的!实际上,在日常生活中,我们是经常把电脑、笔记本、电视机、机顶盒、充电器置于待机状态的,所以这些消耗是实实在在发生的。

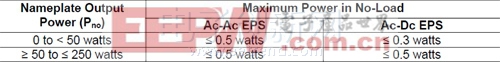

针对待机功耗惊人的浪费,标准组织早就着手制定严格的规定,这是欧盟的能效星级标准

能源之星也有类似的规定,不过张锡亮表示,这个规定还不够严苛,所以他预计能源之星会出台更严苛的标准。

降低功耗的四大举措

面对严格的待机功耗标准需求,半导体厂商各出奇招,努力降低待机功耗,张锡亮分享了NXP的四大举措,就是:

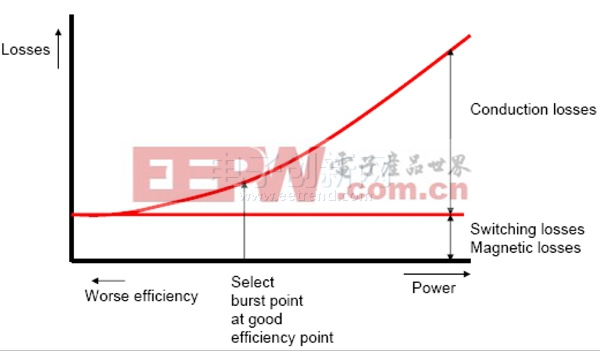

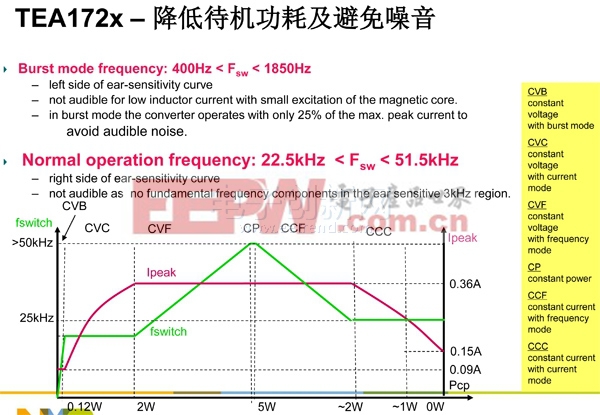

1、采用burst模式提供轻载时的效率

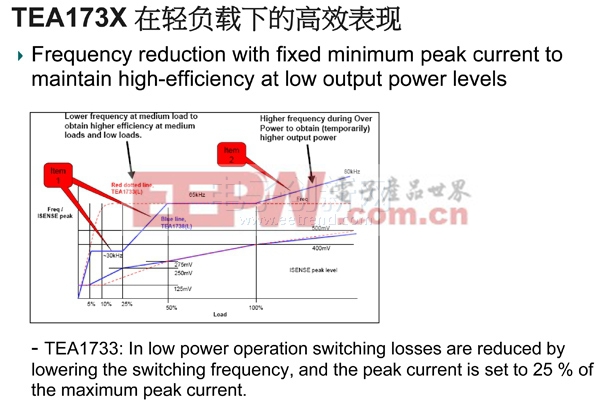

所谓的Burst Mode就是间歇振荡模式,是降低待机损耗的常用手段,当开关频率降低到20K附近的时候如果还要继续减小损耗,就可以进入Busrt mode,此时的开关波形是振一会停一会,这样就可以进一步减小开关损耗。张锡亮解释说,从下图可以看出,电源的损耗在低功耗时主要由开关损耗来主导,可以用burst模式来降低损耗,不过,他说要注意选择一个好的效率平衡点。

BURST 模式的主要是通过对电感电流峰值最小值的钳位来实现的。使能BURST 模式要将MODE接低电平,让BL」RST信号通过选择器到SLEEP。

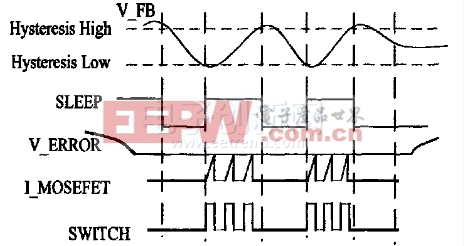

BURST 模式的具体工作过程见下图,在轻载时,主功率管对负载是过充的,电感充向负载的电流大于负载电流,多余的电流就流向输出大电容,这导致输出电压的升高。V而的升高到Bt)RST迟滞比较器的高值时,输出BUSRr信号翻转,传输至SLEEP信号,关断主功率管,等电感电流反向时关断同步管,同时还关断系统中其他的大部分电路,使静态功耗降低。当主功率管被关断,负载电流由输出滤波电容提供,所以输出电压下降,当降到BURST迟滞比较器的低值时,BUSRf信号使能主功率管,系统重新进入峰值电流钳位状态工作。高负载用同步整流轻负载的情况下效率要高。

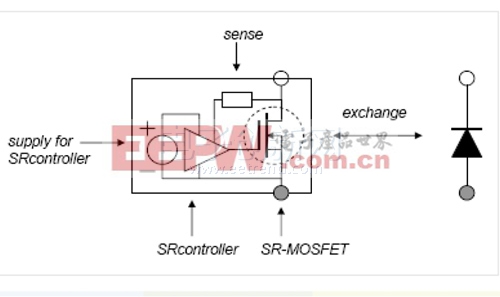

2、在高负载时采用同步整流技术

同步整流是采用通态电阻极低的专用功率MOSFET,来取代整流二极管以降低整流损耗的一项新技术,它能大大提高DC/DC变换器的效率并且不存在由肖特基势垒电压而造成的死区电压。因为功率MOSFET属于电压控制型器件,它在导通时的伏安特性呈线性关系。用功率MOSFET做整流器时,要求栅极电压必须与被整流电压的相位保持同步才能完成整流功能,故称之为同步整流。

实际上,开关电源的损耗主要由3部分组成:功率开关管的损耗,高频变压器的损耗,输出端整流管的损耗。在低电压、大电流输出的情况下,整流二极管的导通压降较高,输出端整流管的损耗尤为突出。快恢复二极管(FRD)或超快恢复二极管(SRD)可达1.0~1.2V,即使采用低压降的肖特基二极管(SBD),也会产生大约0.6V的压降,这就导致整流损耗增大,电源效率降低。

目前笔记本电脑普遍采用3.3V甚至1.8V或1.5V的供电电压,所消耗的电流可达20A。此时超快恢复二极管的整流损耗已接近甚至超过电源输出功率的50%。即使采用肖特基二极管,整流管上的损耗也会达到(18%~40%)PO,占电源总损耗的60%以上。因此,传统的二极管整流电路已无法满足实现低电压、大电流开关电源高效率及小体积的需要,成为制约DC/DC变换器提高效率的瓶颈。

3、采用SOI工艺提升系统能效

实际上,NXP 的Green chip芯片都是采用了其独有的SOI工艺和设计,可以大幅度提升电源系统的能效,与普通电源相比,可以节能达20~30%,NXP的MOSFET也是采用这个工艺技术,可以将导通电阻做的很低。

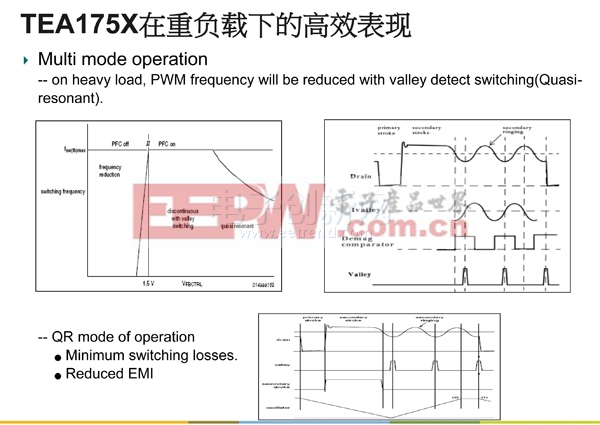

4、采用Multi mode 实现能效的均衡

这实际上是一种变频的技术,具体说来,就是在重负载下,减小PWM的频率,这样把开关损耗降到最低,还可以减少EMI。

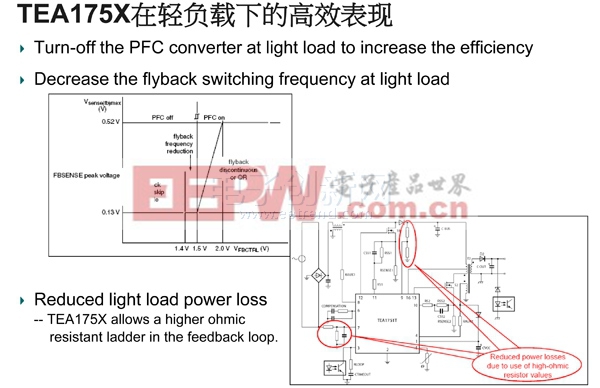

在轻负载时,则关掉PFC转换器,提升能效,这是通过轻载是降低反激式开关电源频率来实现的,另外,张锡亮也表示可以在反馈环路中接一个更高欧姆值的梯形电阻来降低轻载时的损耗。

他也指出,在降低待机功耗的时候要注意消除噪声

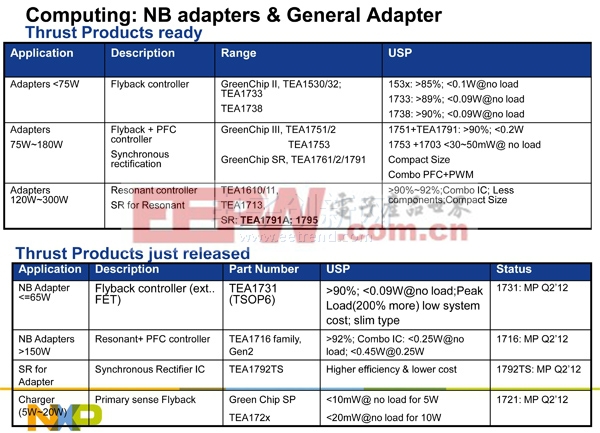

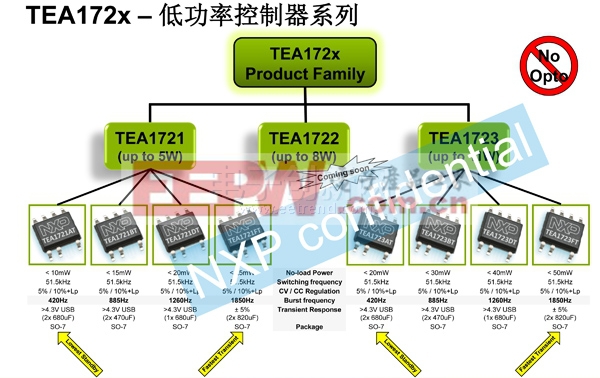

目前NXP green chip芯片的待机功耗测试指标

NXP融合了上述四种技术的各类控制器产品

未来,待机功耗标准会越来越严格,半导体厂商还会从哪些途径降低待机功耗?张锡亮表示,NXP已经研发出了新的技术来降低待机功耗,这个技术预计在今年下半年发布。有兴趣的可以关注下。

评论