XILINX在Transceiver用户手册里提出了对模拟电源的文波噪声要求:10mV p-p 10kHz~80Mhz。大多数客户一看到该指标要求的第一反应是——我做不到,XILINX的Transceiver不好,对电源要求太严了!

事实是这样的吗?不是。XILINX在其用户手册里给出该指标,是为了方便客户作电源设计。因为,有数据可以参考了。很多其他供应商没有给出该指标要求,不等于没有要求。他们往往是通过应用笔记等其他形式规定具体的滤波网络来达到他们的要求,这样反而减小了客户的应用灵活性,往往是不可能严格实现的。因为客户的器件库不见得有供应商推荐的器件。

随着Transceiver的工作速率越来越高,通道数越来越多,需要的电源电流越来越大。原来的LDO+LC滤波网络架构受到挑战,电源效率太低,散热是大问题。因此,在实际的应用中不得不考虑用DC/DC给Transceiver供电,选择怎样的DC/DC?没有技术指标,看来是不可接受的了。

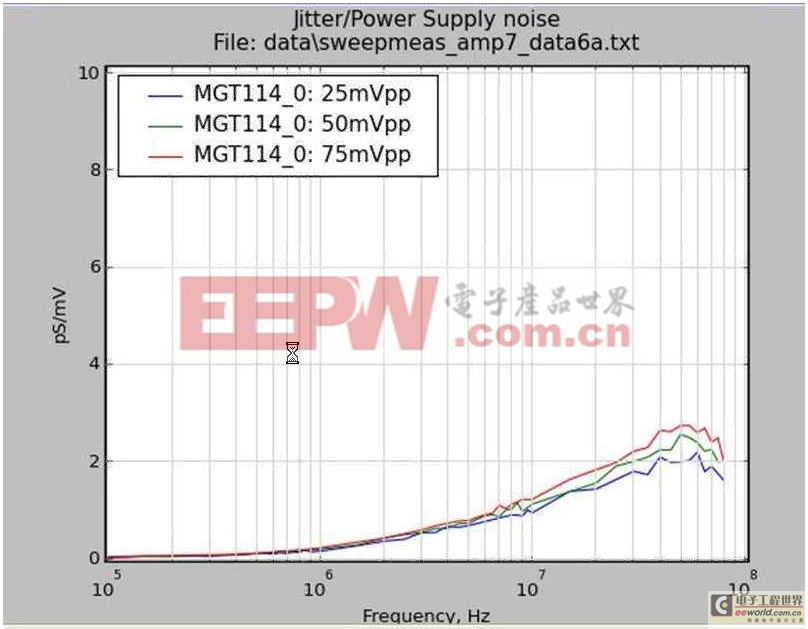

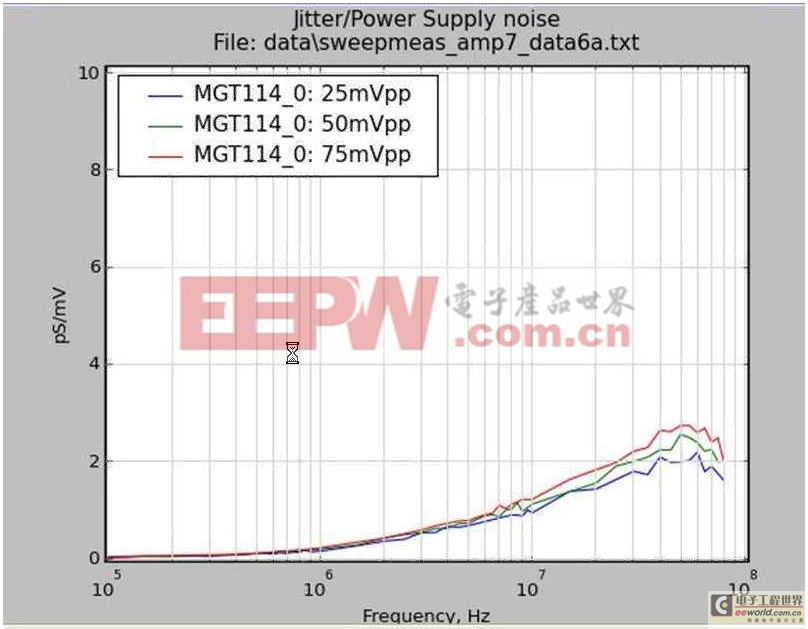

XILINX给出10mV p-p 10kHz~80Mhz的指标是有依据的,可实现的。XILINX最早在UG366里给出该指标时做过电源噪声到输出Jitter的传递函数测试,结果如图1:

图1 电源文波噪声到输出Jitter的传递函数曲线

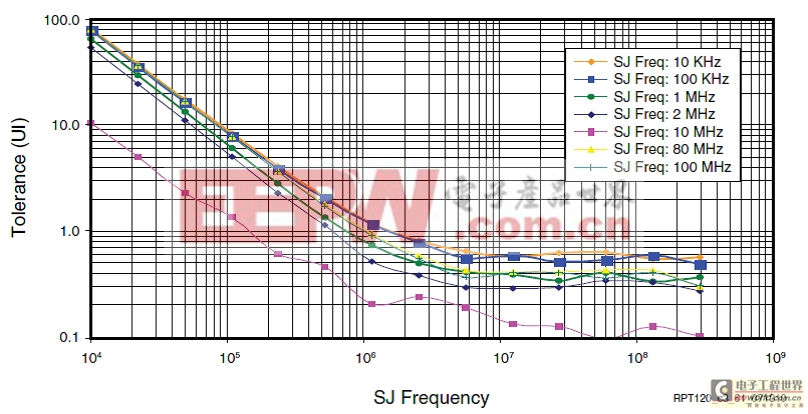

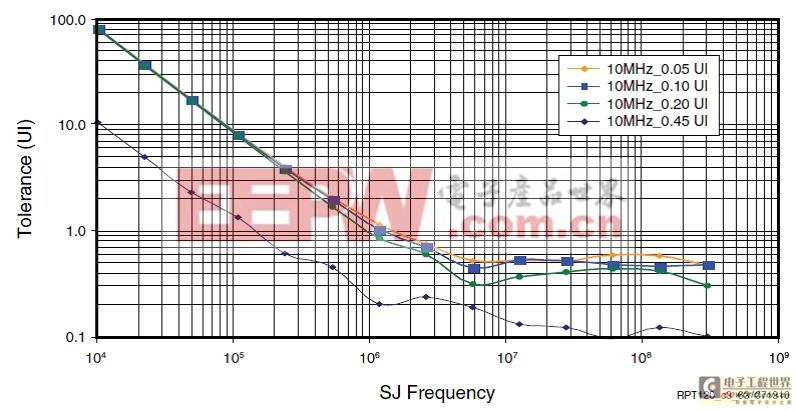

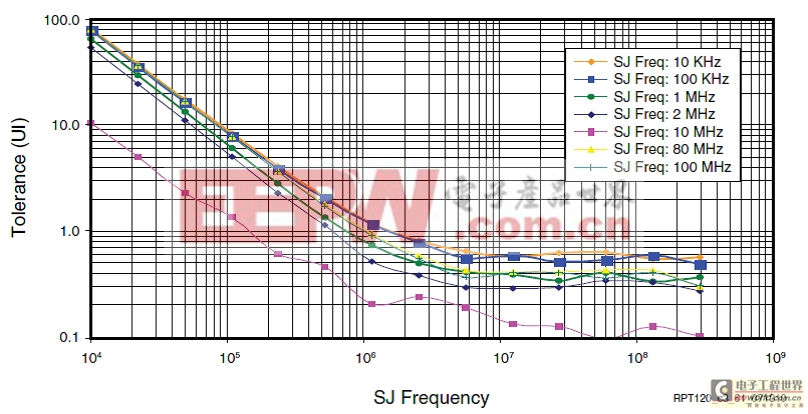

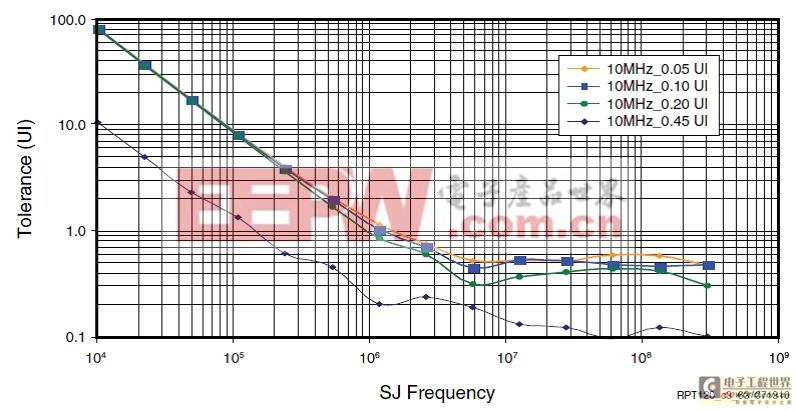

可见,随着频率的升高,每毫伏产生的输出Jitter增加。在10MHz时的灵敏度大约是1.5pS/mV。我们再来看看Tranceiver对哪个频点的Jitter最敏感?能容忍多少Jitter恶化?根据GTX的特性报告RPT120, 10MHz的Jitter对CDR的性能恶化最敏感(图2)。根据GTX的特性报告RPT120,可以接受约0.1UI(16pS @6.5Gbps)的Jitter恶化(图3)。此时,对CDR的性能只有微弱影响。

图2.在不同频点注入0.4UI的Jitter的CDR 抖动容忍度曲线

图3. 在10MHz频点注入不同Jitter的CDR 抖动容忍度曲线

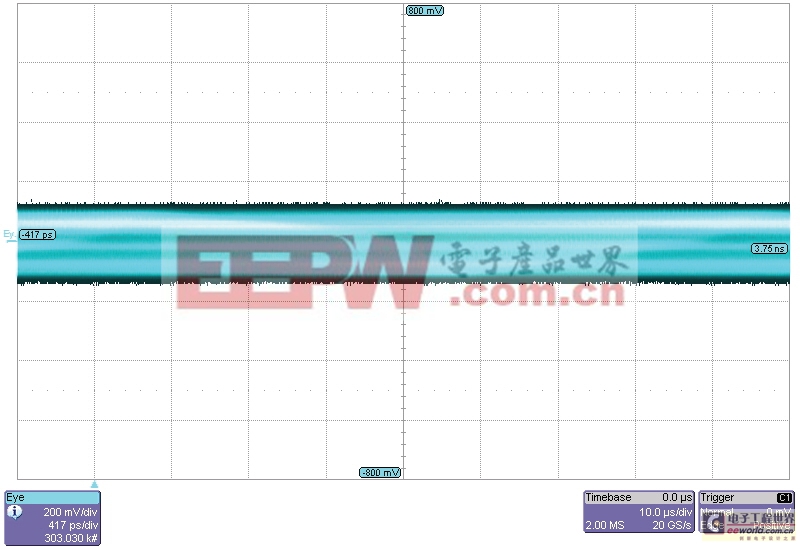

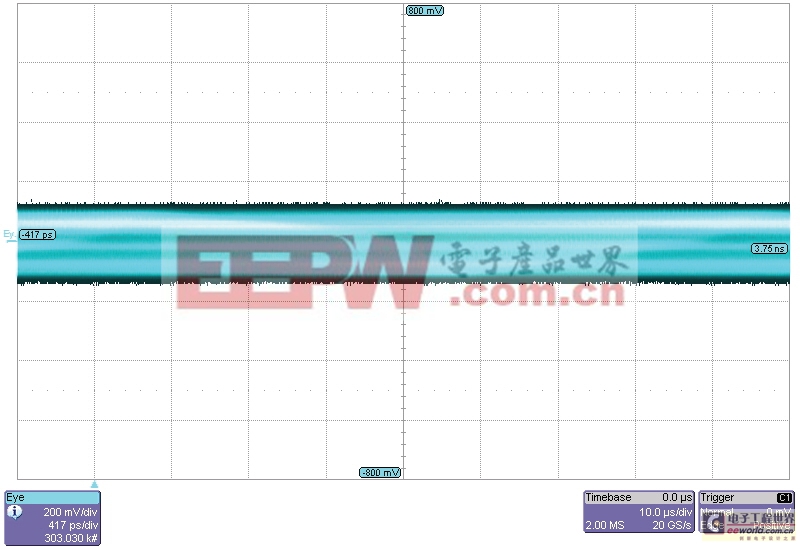

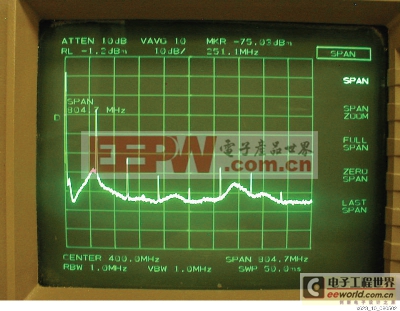

但是,对于电源测试来说,10mV p-p 10kHz~80Mhz的指标确实是挑战。很多仪表(示波器)的本底噪声可能已经接近5mV,如果探头系统不用细同轴线加DC Block的办法,从探头引入的噪声可能已经超过了10mV p-p。因此,需要选用本底噪声低的示波器,最好有可调频点的滤波器,只测10kHz~80Mhz频率段。将示波器的垂直分辨率调到5mV/格,水平方向设成100uS/格,作长余辉测试(见图4)。量其最大峰峰值,要求不超过10mV。如果发现最大峰峰值有少量超过10mV,我们可以用频谱仪作一个附加测试,看看主要的噪声频谱在什么地方(见图5)?如果不在敏感频率上(比如10MHz),而是在低频段(比如1MHz以下),对系统的性能就不会有较大的影响。可以不处理,因为在低频段对电源滤波作处理的代价很大。比如,需要换用LDO,增加系统散热负担。

图4 长余辉法测试电源噪声

图5 频谱仪法测试电源噪声谱

从最近几年的工程实践来看,即使是没有使用单独的DC/DC模块给SERDES供电,也没有引起SERDES问题。即使测量发现问题,也都是测量本身未按正确方法测引入的问题。因此,XILINX给出的电源文波噪声的要求是科学的、合理的可以实现和验证的。

电源滤波器相关文章:电源滤波器原理

评论