四冗余通信板的仿真 少不了CAN总线技术辅助

随着电子技术、计算机应用技术和EDA技术的不断发展,利用FPGA进行数字系统的开发已被广泛应用于通信、航天、医疗电子、工业控制等领域,FPGA成为当今硬件设计的首选方式之一。PC/104是一种专门为嵌入式控制而定义的工业控制总线,以其独特的堆栈式结构、低功率等优点,得到了广泛的应用。作为主流的现场总线,工业控制局域网CAN(Controller Area Network)总线抗干扰能力强,易于组网,具有非常广阔的应用前景。独特的PC/104总线与CAN总线的结合,进一步拓宽了CAN总线的应用领域。

本文引用地址:https://www.eepw.com.cn/article/226552.htm1 基于FPGA的CAN核设计

本设计采用了Altera公司的Cyclone III系列FPGA EP3C25,开发平台采用了Altera公司的Quartus II软件。CAN核的设计以SJA1000功能结构为基础。

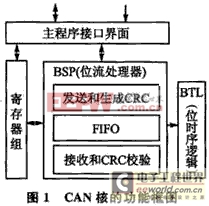

CAN核的功能框图如图1所示。该CAN总线控制器IP核,遵循CANbus 2.0标准,其功能和寄存器操作与SJA1000兼容。IP核采用VHDL编码,并采用容错设计,可抑制存储性器件的数据位翻转,大大提高了IP核的可靠性。CAN核可在FPGA中实现,也可以实现为ASIC。其中包含3个主要模块:寄存器组(can_registers),位时序逻辑 (can_btl),位流处理器(can_bsp)。

寄存器组(CAN Register):外部微处理器可以通过地址直接访问这些寄存器。发送数据时,微处理器将要发送的数据写入发送缓冲器,置位命令寄存器的发送请求位来启动发送。接收到数据后,核心控制器将其存在接收缓冲器,并通知位控制器将其取走。同时,CAN寄存器中还有1个64字节的接收FIFO,可以1次存储至少 2个数据帧。

位时序逻辑(BTL):用来监视CAN总线并处理与CAN总线相关的位时序。在消息的开始处,当位时序逻辑检测到总线上由隐性位(recessive)到显性位(dominant)的跳变时,就会将其内部逻辑同步到位流,称之为硬同步;随后,在接收消息的过程中,检测到隐性位到显性位的跳变时,便会重同步到位流,称之为软同步。位时序逻辑还要根据总线定时寄存器0和总线定时寄存器1的值来决定每个位周期采样点的位置,以补偿传输延迟和相位漂移所造成的误差;同时,根据总线定时寄存器1的设置采取相应的采样模式(单次采样或3次)对总线上的数据采样。

位流处理器 (BSP):根据其实现的功能分为3个模块:数据接收模块、数据发送模块和错误处理模块。数据接收模块将从位时序逻辑送过来的采样数据去除位填充后送到移位寄存器进行串并转换,之后对并行数据进行CRC校验,在消息接收完时发送应答信号,表示接收无误。最后将接收到的消息的特征码与验收屏蔽寄存器的内容进行比较,以决定是否将接收的消息写入接收FIFO。数据接收模块将要发送的数据组成帧并进行CRC计算,之后送入移位寄存器进行并串转换,然后将串行数据编码(位填充)后送到总线上。错误监视模块根据协议规范中描述的错误监视机制检测系统错误,并设置相应的寄存器,通知设备控制器。模块根据协议描述的12 种错误监视规则,在适当情况下对计数器进行加、减或清除。控制器根据这两个计数器的值以及错误限制寄存器的值来决定自己的故障状态:错误激活(Error Active),错误认可(Error Passire)或总线关闭(Bus off On)。2 硬件电路设计

根据系统的总体设计方案,因为现有的CAN总线收发器最大的工作频率为1 MHz,在提高CAN的通信速度后,现有的CAN总线收发器就不能满足需要了,因此改用RS485收发器。由于RS485收发器是差分传输,不能完成通信卡的自发自收功能,因此需要外置的CAN Hub。另外,要进行光纤传输,要完成光的逻辑总线结构,也需要外置Hub。因此,本硬件设计分为CAN通信板的设计和CAN Hub的设计两部分。

(1)CAN 通信板硬件电路设计

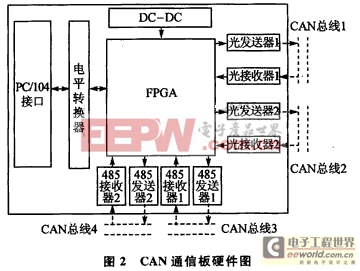

CAN通信板的核心器件是FPGA,同时完成“双光双电”通信,硬件通信板结构如图2所示。

作为PC/104系统的模块,要接在PC/104总线上,所以要在数据、地址、控制总线上与PC/104标准规定的总线标准一致。

本设计要进行四冗余设计,在设计中要添加4个CAN核,选用Altera公司 Cyclone II系列的FPGA EP3C25。

由于PC/104的工作电压为5 V,而FPGA的工作电压为3.3 V,因此在PC/104和FPGA之间要加入1个电平转换器74LVC245来保护FPGA。

(2)光收发电路

本系统的高速光发射器采用HFBR-1414低功耗高速光发射器件,其光发射波长为820 nm。此发射器能够与以下4种光纤配合使用:50/125 μm、62.5/125 μm、100/140 μm、200 μm(HCS)。HFBR-1414采用了双镜片的光学系统,光发射效率高,当驱动电流为60 mA时,在50/125 μm光纤上可得到-15 dBm的光功率。光接收器采用HFBR-2412,其内部集成了光电二极管、直流电路和开集电极的肖特基晶体管。HFBR-2412光接收器能与光发射器 HFBR-1414及50/125 μm、62.5/125 μm、100/140 μm、200 μm

评论