一种数字控制的三相移相触发电路的设计

1 概述

目前,我国的可控硅触发电路分为三类:第一类是模拟型。该类型是80年代初出现的专用集成触发电路产品,此类可控硅触发电路易受元件参数分散性、同步电压波形畸变、温度变化等因数影响,电路较为复杂,可靠性低,抗干扰性差,而且输出不稳定,装置功率大等缺点;第二类是可编程数字型。此类型采用单片机、CPLD等设计,采用编程设置同步和移相.但该类型触发电路具有电路规模较大,技术要求高,软件抗干扰能力差等缺点,而且不易实现小型化、小量产,限制了其广泛应用;第三类是采用数字移相的集成电路。该类触发电路克服了以上两类的一些缺点,大大提高了移相精度和对称度,且易于控制,提高电路的稳定性和可靠性。这里给出一款用于可控硅的集成电路数字控制的三相移相触发电路。针对点电网及现场出现的噪声干扰问题,提出一种去抖动电路设计方案.阐述了移相电路的基本设计思路。

2 电路设计

2.1 电路框架

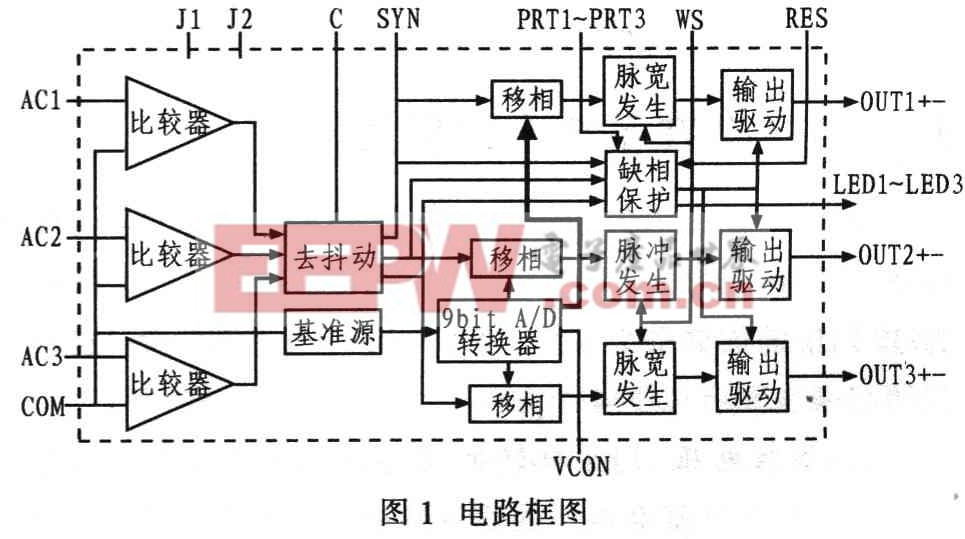

三相正弦输入(ACl~AC3)经比较器,转换成与输入同步的方波信号,再经去抖动电路消除输入信号噪声,生成干净的同步方波信号,进入移相电路。移相控制信号由外部电压输入提供,移相控制电压经9 bit A/D转换器转换,作为移相电路中计数器的初始值,当计数器计数满时,产生一个移相脉冲,该移相脉冲再次触发脉宽发生电路,产生所需的脉宽信号,经调制后输出。该电路框图如图1所示。表l给出了各引脚功能说明。

2.2 噪声消除电路

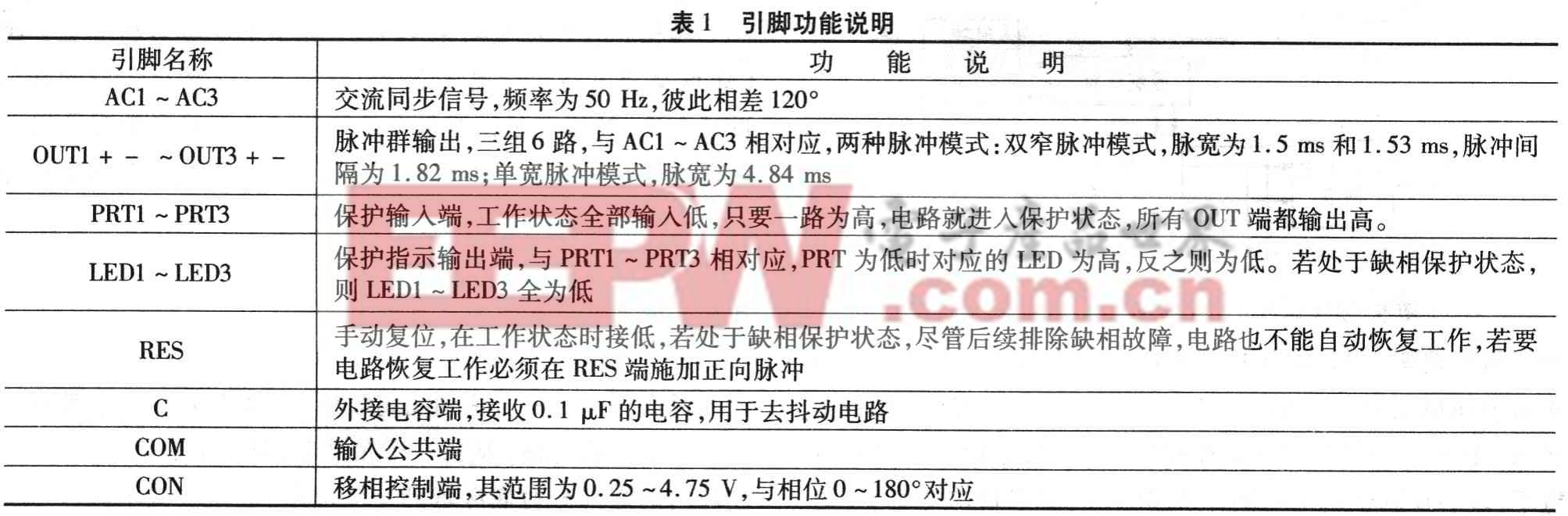

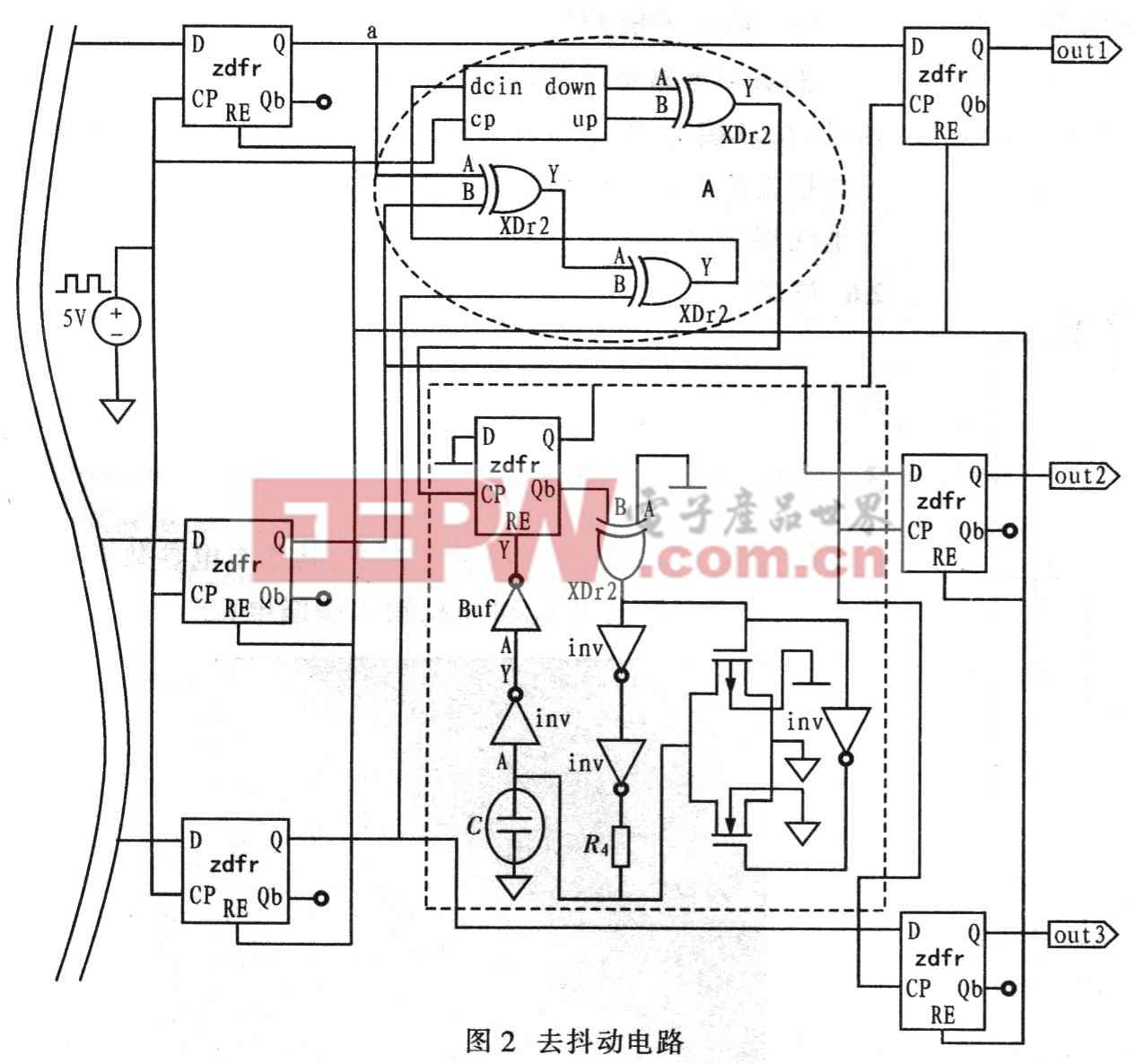

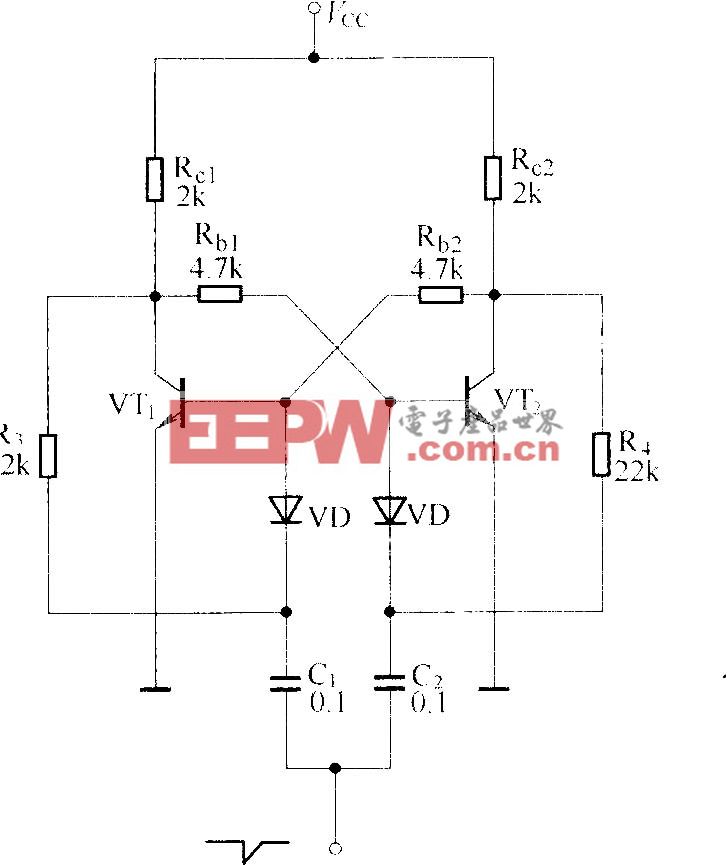

图2是去抖动电路。三相交流电同步信号经比较器后,通过触发器使其与内部时钟同步,同步信号a.b和c分别对应图3中的/net63./net58和/net43,可见这3个信号的上升沿和下降沿都具有毛刺抖动信号。图2中的电路A部分是边沿检测电路,其功能是利用a,b和c所有上升沿和下降沿产生小脉冲。电路A部分的输出作为时钟信号进入电路B,实现去抖动电路。当第一个脉冲到来时,触发器输出高电平,同时启动电阻电容的充电电路,电容充电,当充电达到使其后面的反相器翻转,触发器复位,触发器输出低电平。电容充电波形如图3中的/net90,触发器输出信号波形为/net52。再利用该输出信号作为时钟信号对同步信号a,b和c采样,滤除信号中的所有毛刺抖动成分,最终输出信号为/out3,/out2和/outl。

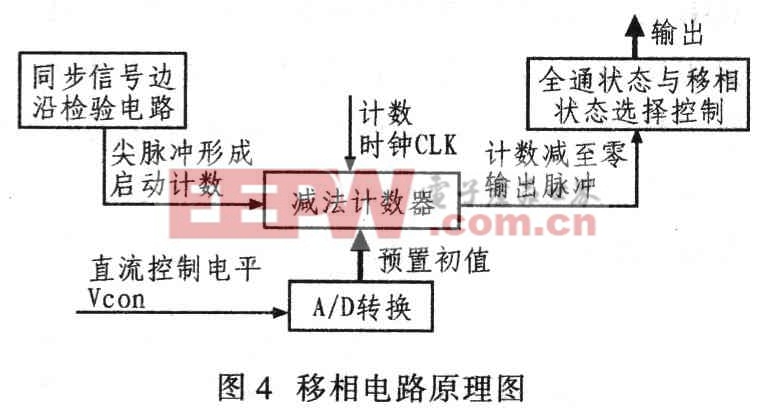

2.3 移相电路

移相电路是数字三相移相触发电路的主要部分。其原理如图4所示,同步信号、正弦信号通过过零比较器变为相位与周期一致的同步方波,上升沿和下降沿检验电路检验出同步方波的上升沿和下降沿,产生的两个尖脉冲分别对应同步信号正负半周的的触发信号。采用该触发信号启动计数器进行减法计数,A/D转换器输出置为计数器的初值,当减法计数器为零时则产生移相后的尖脉冲,减法计数器的启动和停止脉冲之间的相位差,即对应于脉冲群与正弦波之间的相位差△φ。

2.3.1 移相范围

计数器的时钟CLK(晶体振荡器)是由晶体振荡器提供的恒定值。假设A/D转换器的位数为N,分辨率即为2N。滞后时间最大值为:![]() 时可以选择适当的N和晶振,晶体振荡器,使2N/f晶振≥T工频/2(10 ms)。因此,当直流控制电平Vcon从5一OV调节时,脉冲群与正弦波之间的相位差△φ对应于O~(T工频/2)。因此,一般情况下,触发电路的相移范围为:△φ∈[0,(T工频/2)]。但由于集成电路的制作工艺的差异、电网的频率波动和比较器检测过零点的精确度不高.实际移相范围要比以上的范围窄一些,只要移相范围不小于178°即可满足较高的要求。

时可以选择适当的N和晶振,晶体振荡器,使2N/f晶振≥T工频/2(10 ms)。因此,当直流控制电平Vcon从5一OV调节时,脉冲群与正弦波之间的相位差△φ对应于O~(T工频/2)。因此,一般情况下,触发电路的相移范围为:△φ∈[0,(T工频/2)]。但由于集成电路的制作工艺的差异、电网的频率波动和比较器检测过零点的精确度不高.实际移相范围要比以上的范围窄一些,只要移相范围不小于178°即可满足较高的要求。

2.3.2 控制精度

控制精度是指A/D转换器输出的数字量变化一位时。输出角度的变化值,设A/D转换器的位数为N位,那么A/D转换器输出最大的数字量为2N,故触发器的控制精度![]() 若A/D转换器的位数为9位(N=9),那么控制精度为180°/2°=0.35l 6°/bit。

若A/D转换器的位数为9位(N=9),那么控制精度为180°/2°=0.35l 6°/bit。

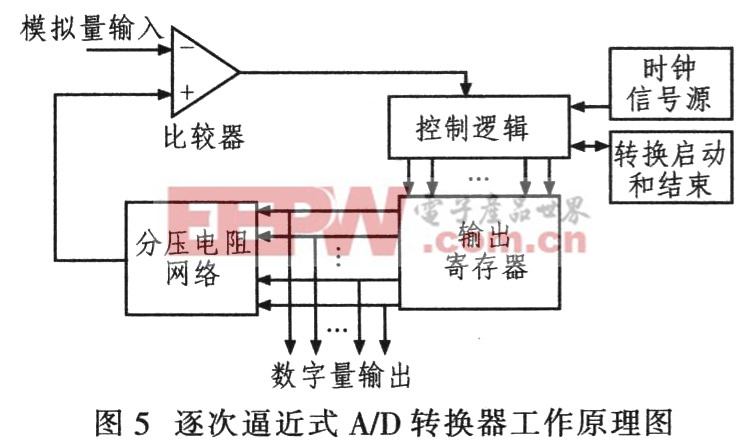

2.4 A/D转换电路

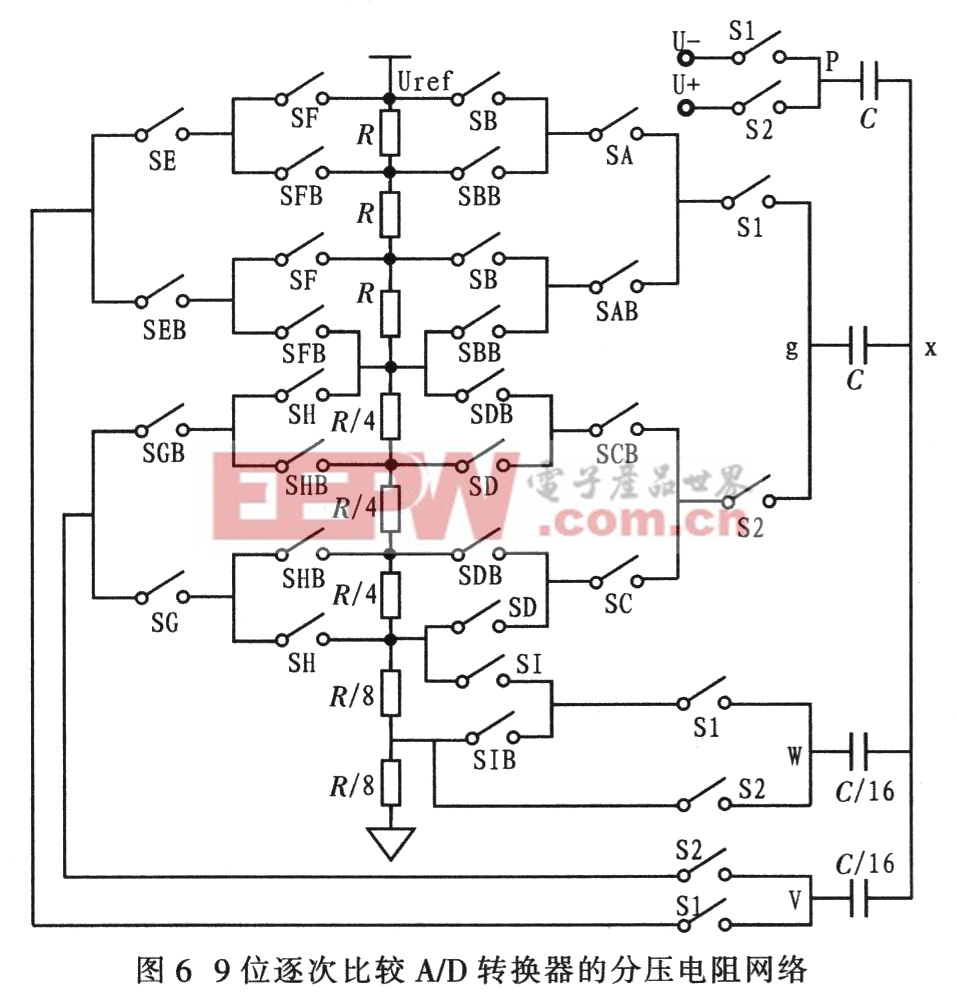

考虑到设计要求,由于处理时钟频率不高,因此采用中速逐次逼近式A/D转换器,其工作原理如图5所示,包含比较器、D/A转换器、寄存器、时钟信号源和控制逻辑等5部分。

转换周期从采样所需转换的输入模拟信号开始。数字控制逻辑电路假设MSB为1,其他所有码元为0。将此数字字作为分压电阻网络的输入,产生0.5UREF的模拟信号,如图6所示。比较该模拟信号和采样模拟信号。如果比较器输出高电平,数字控制逻辑电路则令MSB为1;如果输出低电平,则MSB为0。这样实现逐次逼近的第一步.并确定MSB值。然后猜想次高位为1,其余位为0,并和已知数值的MSB位组成数字量,输入分压电阻网络。再比较分压电阻网络输出和采样输入信号,如果比较器输出高电平,则次高位为1;反之则为0。直到所有数字量的位在逐次逼近中确定为止。

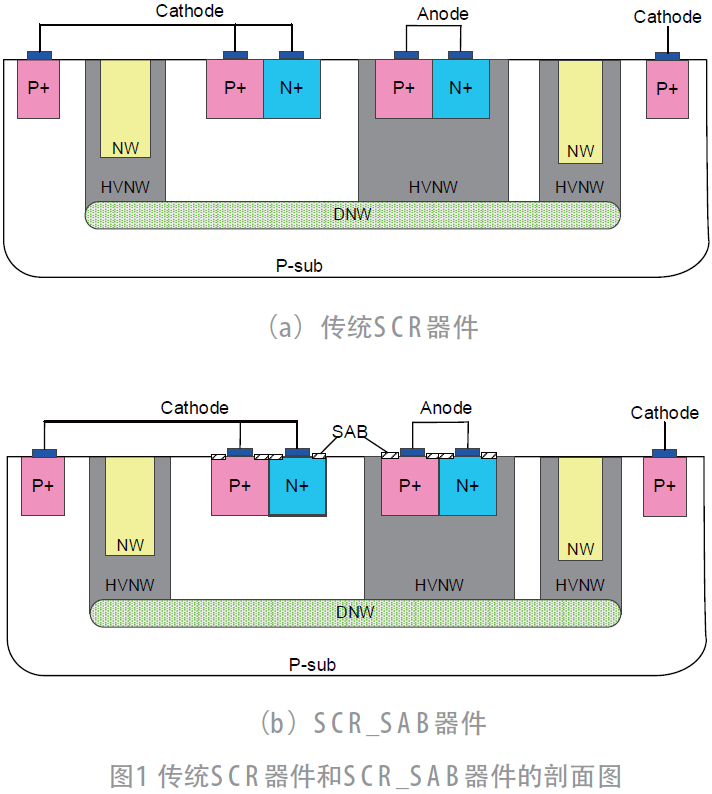

2.5 电路布局

移相触发集成电路采用1.2μm N阱双层多晶单层金属CMOS集成电路设计规则设计电路布局。采用全定制的布局设计方法。其特点是针对每个晶体管优化电路参数和布局以获得最佳性能以及最小面积。布局设计需解决的关键问题是减少衬底耦合噪声的影响,可通过以下途径解决:

(1)阱隔离环低掺杂的衬底中,物理隔离通过增加注入孔和感应孔间的距离来增加两者间的电阻,增强隔离效果。

(2)用P+扩散层形成隔离 P+扩散层通过吸收数字器件注入衬底的噪声电流达到隔离效果,隔离环用于包围数字电路或者是模拟电路。从另一个角度看,引入了P+隔离环后,减少环内的那部分衬底区域到地的电阻,也相应减小该区域受到的耦合噪声干扰。

(3)数字电路地与衬底分离将数字电路的N管的源极通过Metal接地,而不与衬底相连。衬底为模拟地,因此通过这种措施将模拟电路和数字电路地分开.模拟和数字电路通过地线耦合抑制噪声。

2.6 仿真结果

仿真结果如图7所示,输入为三相正弦信号,输出为6路移相触发脉冲。

3 测试结果

图8给出该系统测试结果。其中,其基本电参数测试结果如下:静态电源电流IDO8 mA,输入端漏电流IILlμA,输入端漏电流IIHlμA,输出吸收电0流IOL1(VOL=0.8 V)>25 mA,输出驱动电流IOH1(VOH=4 V)一25 mA,输出吸收电流IOL2(VOL=0.5 V)>3 mA,高阻态漏电流IOZlμA。其功能测试结果为:移相范围为0~178°,移相精度为0.35°/mV。

4 结语

设计了一款用于可控硅控制的三相移相触发电路。针对点电网及现场出现的问题,提出了一种去抖动电路解决方案,给出了移相电路的基本设计思路。通过仿真和实际测试.该电路的移相范围达到178°,移相精度为0.35°/mV。该电路采用数字控制方式,使得移相精度和对称度大大提高,且控制方便,提高了电路的稳定性和可靠性,并克服以往电路精度差、可靠性低以及技术复杂等缺点。

评论