具有PCM和DSD双功能的DAC芯片PCM1738

摘要:PCM1738是B-B公司生产的高级数模转换数码音响芯片,利用它可以同时对SACD音频格式的DSD数据流和DVD-Audio用的PCM编码进行数据变换和解码。文中介绍了PCM1738的基本原理、主要性能指标及应用信息,同时对其高级段DAC和电流段DAC的新技术做了描述。

1 概述

PCM1718是B-B公司继24bit/192kHz正弦量方式DAC解码芯片PCM1704和SACD的DSD解码芯片PCM1700之后,最新开发的又一片应用于高档音响设备的双功能解码芯片。该芯片既可对DVD-Audio的24bit/192kHz的PCM编码数字音频信号进行解码,又可以对SACD的64fs/1bit的DSD编码数字音频进行解码,而且性能良好。因此,它是目前开发高档音频播放机或进行音响数模变换的理想器件。

2 PCM1738的特点和性能

图1所示是PCM1738的结构功能框图,其各引脚的功能说明如表1所列。PCM1738的主要特点如下:

●上有24bit分辨率;

●取要频率达10~192kHz;

●具有多种接口格式功能,其中16/20/24bit为后接格式,16/20/24bit I2S,24bit为前接格式;

●系统时钟有128/192/256/384/512/768fs多种选择,其中fs的范围为32kHz~192kHz;

●模拟输出差动电流为±2.5mA(Iout端输出);

●内含8倍超取样数字滤波器,可选择快慢两种斜降,并且无域外噪声上升现象;

●具有数字音量衰减、软静噪、零检出门闩和去加重等功能;

●具备DSD模式,并具有四种滤波模式可供选择;

●具备DF旁路模式,可隔离PCM1738内部的数字滤波器,从而使输入信号可以和更高档的外部数字滤波器进行连接;

●采用模拟5V和数字3.3V的电源;

●采用28脚SSOP封装形式。

表1 PCM1738管脚功能表

| 管脚编号 | 名 称 | I/O | 功 能 |

| 1 | RST | I | 复位输入 |

| 2 | ZEROL | O | L声道0标识 |

| 3 | ZEROR | O | R声道0标识 |

| 4 | LRCK | I | DFTH模式时为WDCK时钟输入;DSD模式时接地 |

| 5 | DATA | I | L声道音频数据输入 |

| 6 | BCKI | I | DFTH模式时为位时钟输入;DSD模式时接地 |

| 7 | SCKI | I | DFTH模式时为系统时钟输入;DSD模式时为接地 |

| 8 | DGND | - | 数字地 |

| 9 | VDD | - | 数字电源(+3.3V) |

| 10 | SCKO | O | 系统时钟输出 |

| 11 | MDO | O | 功能控制寄存器串数据输出 |

| 12 | MDI | I | 功能控制寄存器串行数据输入 |

| 13 | MC | I | 功能控制寄存器移位时钟 |

| 14 | SC | I | 功能控制寄存器锁存使能端 |

| 15 | MUTE | I | DFTH模式时为静音;DSD模式时为R声道音频数据输入 |

| 16 | IoutR- | O | 右声道负电流输出 |

| 17 | IoutR+ | O | 右声道正电流输出 |

| 18 | AGND1 | 模拟地线1 | |

| 19 | VCOM1 | - | 内部偏置去耦端 |

| 20 | VCOM2 | - | I/V公共电压 |

| 21 | Iref | - | 输出电流基准偏置端,接16kΩ电阻到地 |

| 22 | VCOM3 | - | I/V公共电压 |

| 23 | Vcc1 | - | 模拟电压+5.5V |

| 24 | Vcc2 | - | 模拟电压+5.5V |

| 25 | IoutL+ | O | 左声道正电流输出 |

| 26 | IoutL- | O | 左声道负电流输出 |

| 27 | AGND2 | - | 模拟地线2 |

| 28 | Vcc3 | 模拟电压+5.5V |

3 PCM1738的高级段工作原理

PCM1738的高级段(Advance Segment)DAC和电流段DAC是B-B公司专门为PCM1738新开发后种新颖的数模变换方法。由于24bit分辨精度高达1/1677216=0.00000006,因此,元件精度和电路结构都制约最终的实际精度。在现有集成电路制作的工艺水平条件下,开发新型电路是一种能较快提高水准的捷径。

PCM1738高级段DAC的总体原理如图2所示。其高级段的DAC方式主要由反相被偿失调双极型ICOB解码部分、5电平三阶Δ-∑调制、高级段数据加权平均DWA和67个电平差动电流段构成。当经过格式变化后的数字输出数据进入数字滤波器后,它首先通过八倍超取样变换成为24bit/8fs数据,然后再将其分割成上位和下位两段。其中上位段为除去最高位MSB的6bit数据,而下位段则是MSB和后17bit组成的一共18个bit的数据。运行时,将上位6bit输入ICOB解码部分,而将下位18bit数据则输入5电平三阶Δ-∑调制器。这样利用上位6bit即可调制出64个台阶的粗波形(m=2的6次方=64),而下位18bit即是数据中的6位所不含的残留量。

解码器ICOB(Inverted Complementary Offset Binary)称反相补偿失调二进制,它把不含MSB的6bit数据变换成64电平数据,然后再分割成适合于电流段工作的63电平工作码输出。

5电平三阶Δ-∑调制器的等效电路见图3所示,在对输入幅度较大的信号进行调制时,每个取样点在振幅方向上的移动设定在1个电平之内。这样支使振幅对时间轴的误差(主时钟引起)相对小一些。

63电平的ICOB数字输出和5电平三阶Δ-∑调制器输出的电平量均为1,在求和电路中可以直接相加成为67电平的ICOB码,然后再加上Δ-∑调制信号传送下去,最后进行数码变换操作。

数码变换的操作分为两步,分别为高级DWA和电流段DAC。高级DWA(Advance Data Weighted Averaging)可用来产生数模变换之后的电流段中需要的最合适的工作时钟。为了最大限度地抑制模拟误差,PCM1738用独立的定时控制和一阶噪声整形操作相组合来实现高精度的低抖动(jitter)。

电流段(Segment)DAC由对模拟量相同加权的平衡差动电流部分和对此电流段进行开/关控制的电流开关构成。它是从数字信号变换到模拟信号的DAC的心脏。图4是电流段的简化等效电路。它共有75对差动电流源,可用来自高级DWA的67种电平按输入量和控制时钟来对其进行控制以完成变换工作。由于这75对电流源处理67种电平有足够的余量,因而各个电流源都能工作在最佳状态,而不会出现无声音调或特大振幅时的失配误差。

PCM1738除了可以对DVD-Audio的24bit/192kHz PCM编码进行数模变换外,还具有对SACD的DSD直接数据流进行数模变换的能力。

图4的电流源结构也可以用于64fs/1bit的DSD信号的数码变换,如果将其作为模拟FIR滤波器使用,基功能相当于图5所示的FIR滤波器。其中延迟单元D和各种电流段的数值即为各节之权重,此时各电流源采用差动方式工作,以便获得高品质的DSD/模拟变换。

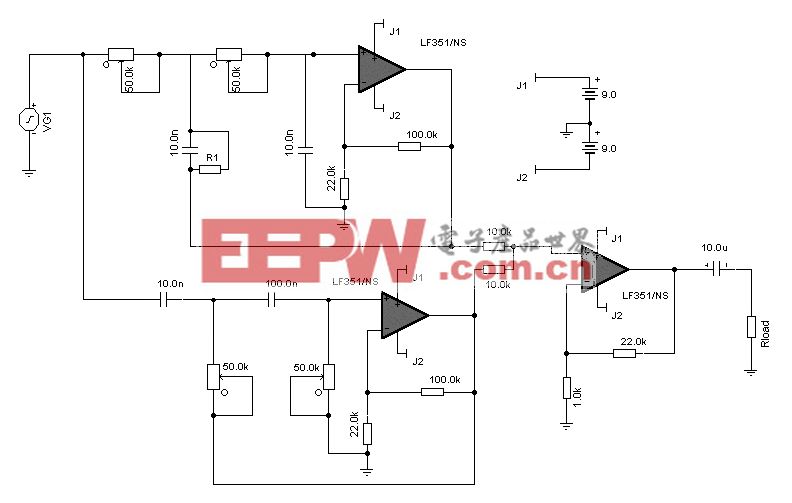

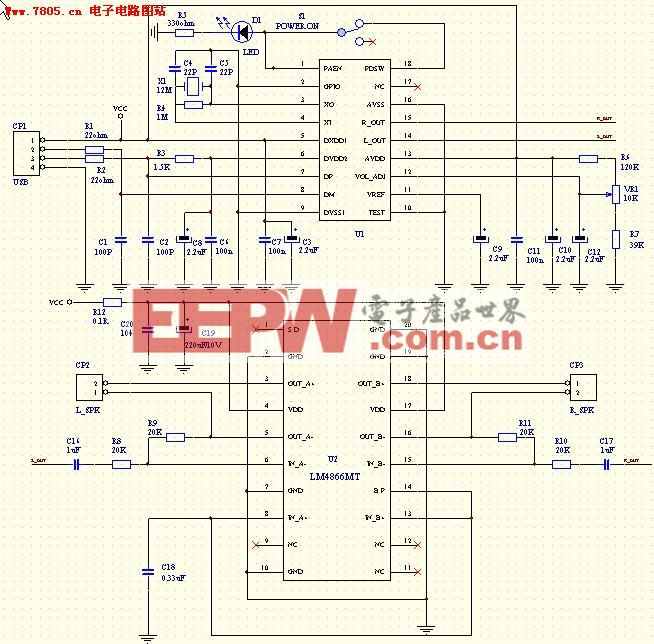

4 PCM1738的应用电路

图6是PCM1738的应用电路。其中音频数据接入、工作时钟、控制用串行数据接口等部分在图中已经略去,模拟输出部分公司评估板的实际电路。PCM1738中D/A变换器的模拟输出为平衡差动电流,其满幅度(0dB)时为±2.5mA,峰峰值为5mA。所以使用时必须外加电流/电压(I/V)变换电路,而且同时需要进行双端/单端变换。当I0端子处于满幅度时,其输出Iout为±2.5mA,图中的反馈电阻R11,R12,R21,R22均为620Ω,这样,I/V变换出的电压V0将为±(2.5Rf)mA。另外,由于后段部分带滤波作用的双端/单端变换输出的增益为1,所以实际输出电压变为两输入信号之差。即:

Vout=Vo-(-Vo)=2Vo,

这样可得出输出峰-峰值Vp-p应为2.192Vrms。

频率响应由与反馈电阻并联的电容决定,按照DVD-Audio和SACD标准,其信号的带域要求应达到100kHz。但实际上仍可根据需要在一定范围内调整,本电路中的电容电阻值所决定的最终带宽为70kHz。

按一般播放机的输出电平(2Vrms)和信噪比(-120dB)要求折合出的噪声电平只有2μv,这就是说,运放和电阻电容等器件的噪声是决定最终设备的杂音电平的主要因素,因而必须注意每个环节的品质指标以便获得最佳的音质。

评论