串行输入电压输出的14位DAC数模转换器芯片AD5551/AD5552

摘要:美国ADI公司生产的数模转换器AD5551/AD5552是一种串行输入电压输出的DAC,具有14位分辨率,并具有施密触发输入和快速稳定时间等特点。可用于自动控制、数据获取和工业过程控制系统中。

关键词:DAC 3线串行接口 施密特触发 AD5551/AD5552

1 概述

AD5551/AD5552是单极电源、14位分辨率、串行输入、电压输出的数模转换器,它们采用了多功能3线接口技术,能与SPI、QSPI、MICROWIRE和DSP接口兼容。该DAC的无缓冲输出减少了输出缓冲所引起的功耗和偏离误差。AD5552有一个外部运算放大器,能够在双极模式下工作,具有±VREF的输出电压摆范围。其主要特点如下:

●单电源运算,可在5V±10%单极电压下工作;

●功耗低,5V情况下通常为1.5mW;

●采用3线串行接口;

●具有驱动60Ω负载的无缓冲输出能力,能减少输出缓冲而引起的功耗;

●内含加电复位电路系统。

图1和图2分别是AD5551/AD5552的引脚图,表1是AD5551/AD5552的引脚功能说明。

表1 AD5551/AD5552的引脚功能

| 引脚名 | 引脚号 | 描 述 | |

| AD5551 | AD5552 | ||

| RFB | 1 | 反馈电阻。在双极模式时与外置大器输出相连 | |

| VOUT | 1 | 2 | DAC的模拟输出电压 |

| AGNDF | 2 | 3 | 模拟电路系统的接地参考点(压力) |

| AGNDS | 2 | 4 | 模拟电路系统的接地参考点(温度) |

| VREFS,VREFF | 3 | 5,6 | DAC的电压参考输入。与2V~VDD的外部参考电压相连 |

| CS | 4 | 7 | 有源低逻辑输入信号。该片选信号可用来限制串行数据输入 |

| SCLK | 5 | 8 | 时钟输入。数据在SCLK的上升沿被时钟引入输入寄存器 |

| NC | 9 | 悬空引脚 | |

| DIN | 6 | 10 | 串行数据输入 |

| LDAC | 11 | LDAC输入。当输入为低电位时,DAC寄存器同时更新为输入寄存器的内容 | |

| DGND | 7 | 12 | 数字地。数字电路系统的接地参考 |

| INV | 13 | 与DAC的内部电阻相连。在双极模式下,该引脚也外部运放的转置输入端相连 | |

| VDD | 8 | 14 | 模拟电压源。5V±10% |

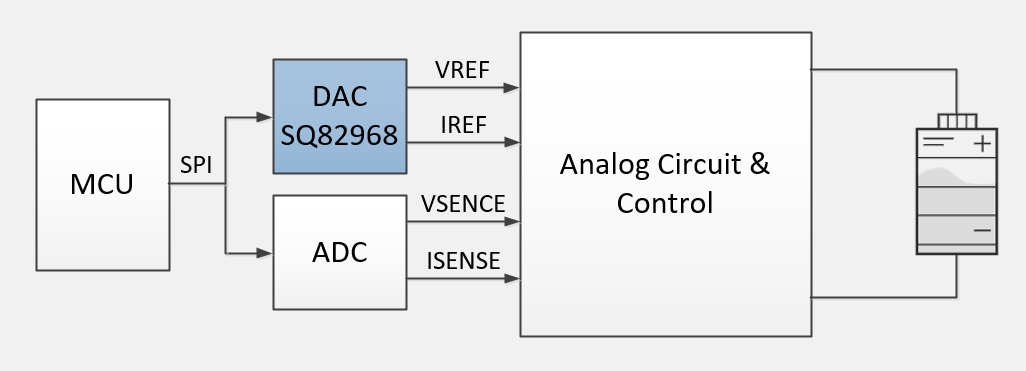

2 与微处理器的接口电路

AD5551/AD5552与微处理器的接口通常采用与DSP处理和微控制器协议标准相兼容的串行总线相连。其会话通道需要一个由时钟信号、数据信号和同步信号组成的3线接口。AD5551/AD5552需要在SCLK的上升沿引入有效的14位数据字。当所有数据时钟引入时,DAC能自动更新数据,否则它将在LDAC的控制下更新(只对AD5552而言)。

2.1 与ADSP2101/ADSP2103的接口

图3是AD5551/AD5552与ADSP2101/ADSP2103之间的串行接口示意图。利用该电路可通过串行端口控制寄存器对ADSP2101/ADSP2103进行编程。ADSP2101/ADSP2103被配置成内部时钟、低电平帧信号和16位字长。由于AD5551/AD5552只保留最后14位,所以前两位不用考虑。在串行端口开始工作后,可通过给Tx寄存器写入一个字开始发送数据库。由于边沿触发的相位相反,所以在DSP和DAC的SCLK端口之间需要一个反相器。

2.2 与80C51/80L51的接口

图4是AD5551/AD5552和80C51/80L51之间的串行数据接口电路。图中,微控制器的TxD引脚用于驱动AD5551/AD5552的SCLK引脚,同时RxD驱动DAC的串行数据线。P3.3既可用来驱动CS引脚,又可在串行端口上编程。

80C51/80L51开始时提供的是最低有效位,但AD5551/AD5552希望开始时得到14位字的最高有效位。传送数据时应考虑这一点。通常这可用软件来实现。在输入DAC之前,应将每一位移出数据按正确顺序排列好。由于DAC只保留最后14位字,所以80C51的前两位在重新调整后不用考虑。

当数据开始传送到DAC时,PC3.3为低电平。RxD上的数据TxD下降沿有效。由于DAC时钟数据在串行时钟的上升沿时进入输入移位寄存器,所以TxD的时钟必须翻转。由于在传送周期仅出现8个时钟不降沿,所以80C51/80L51应按8位字节来传输数据。因为DAC需要14位字且P3.3(或其他可编程引脚)可作为DAC的CS引脚输入信号,因此,P3.3在2×8位字的16位写周期的开始为低电平,并保持低电平到2×8位写周期完成,在这之后P3.3变为高电平并完成DAC的新数据读入。同样,在数据重新调整之后,前两位不用考虑。通过使用另外一个可编程引脚P3.4,可使AD5552的引脚由80C51/80L51的串行端口输出来控制。

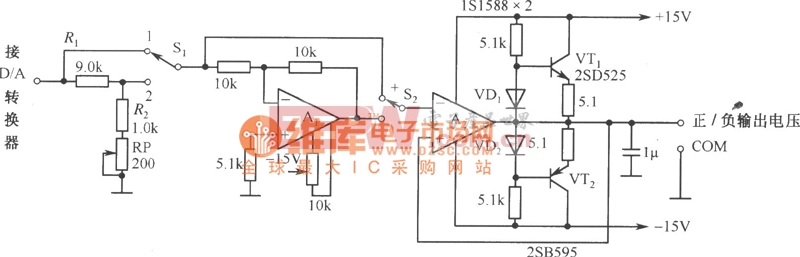

3 AD5551/AD5552的应用电路

3.1 光耦合接口电路

AD5551/AD5552的数字输入为施密特触发,适用于缓慢传送的数据输入。因此,它们能够适用需要DAC通过光耦合器与控制器隔离的工业应用中。图5是一个应用接口电路示意图。

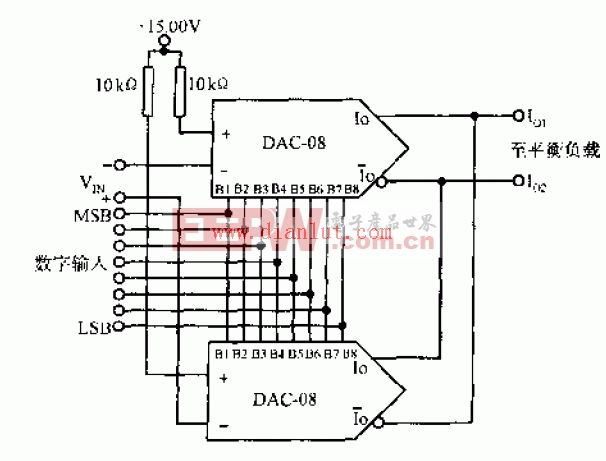

3.2 译码多个AD5551/AD5552

AD5551/AD5552的CS引脚可用来选择任何一种CS。所有装置均可接收同样的串行时钟和数据,但只有其中一个装置在某个时刻接收CS信号。DAC的地址由译码器决定,可在数字输入线上产生一些数字反馈。采用脉冲时钟可以降低模拟通道数字反馈的影响。图6是这种应用的典型电路。

评论