基于DSP和CPLD的宽带信号源的设计

1 引 言

信号源是雷达系统的重要组成部分。雷达系统常常要求信号源稳定、可靠、易于实现、具有预失真功能,信号的产生及信号参数的改变简单、灵活。本文采用dsp和cpld来设计信号源的控制部分,一方面能利用dsp软件控制的灵活性,另一方面又能利用cpld硬件上的高速、高集成度和可编程性。使用这种方法可以充分利用软件支持来生成和加载任意波形数据,并能方便地实现对信号参数的控制和对波形数据的随意修改,同时又能保证信号产生的高速、灵活可控。

2 系统结构

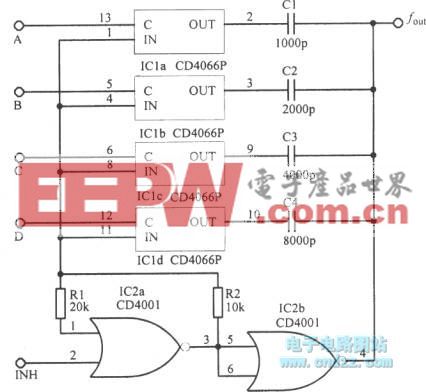

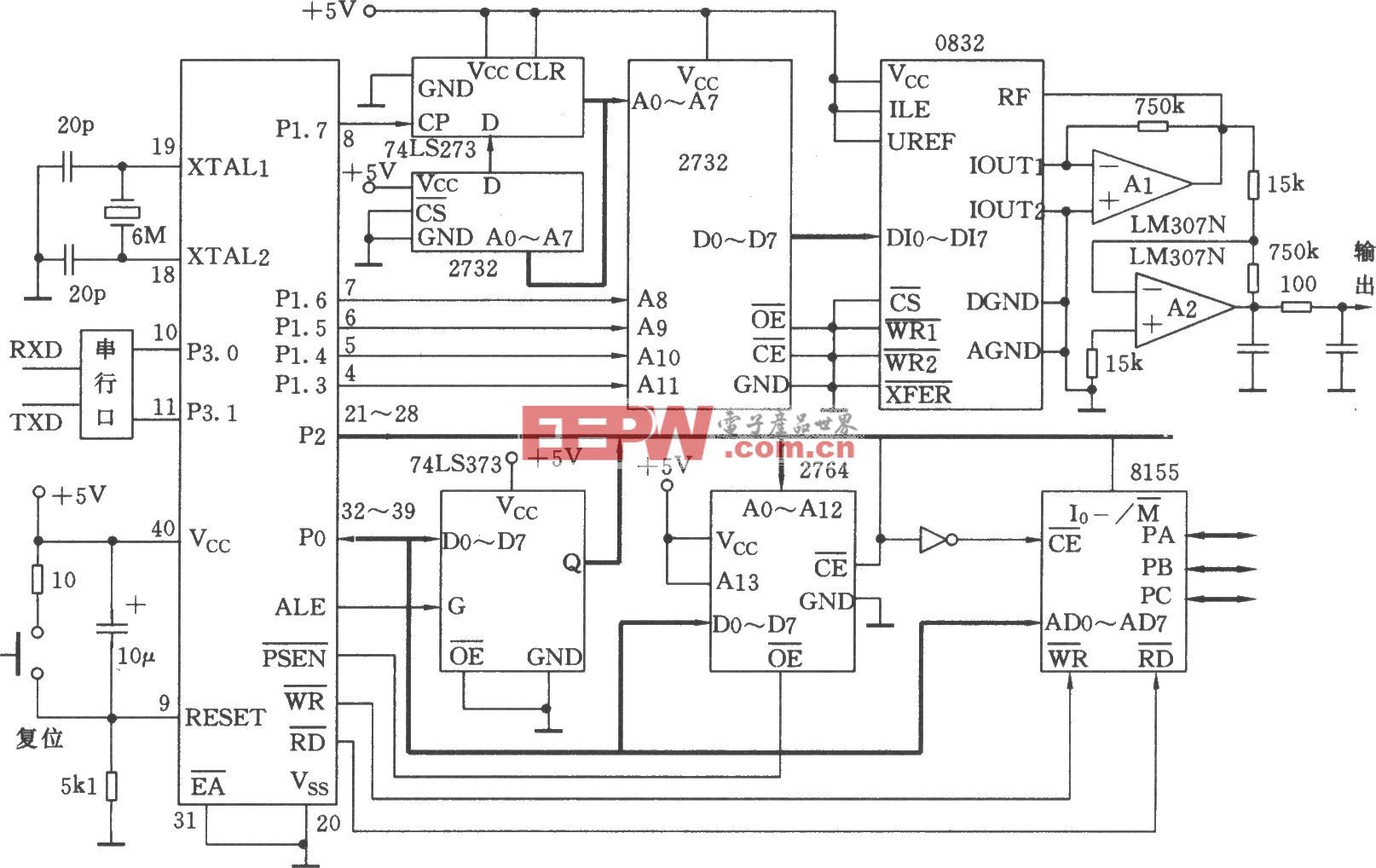

采用波形存储直读法,即通过对存储的波形采样数据进行数模变换,直接生成模拟信号的一种方法。图1为信号源的系统结构。本信号源可工作于联机和脱机两种方式。联机工作时,波形数据从微机加载,由dsp控制,通过cpld内的数据通道写入sram,经回读、校验后,从sram内高速送入到数/模转换器件产生雷达信号。脱机工作时,波形数据可在系统上电时由eeprom加载,eeprom中可存放一组波形数据,也可存储多组数据以方便应用。

3 硬件实现

3.1 tms320f206与eeprom的接口设计

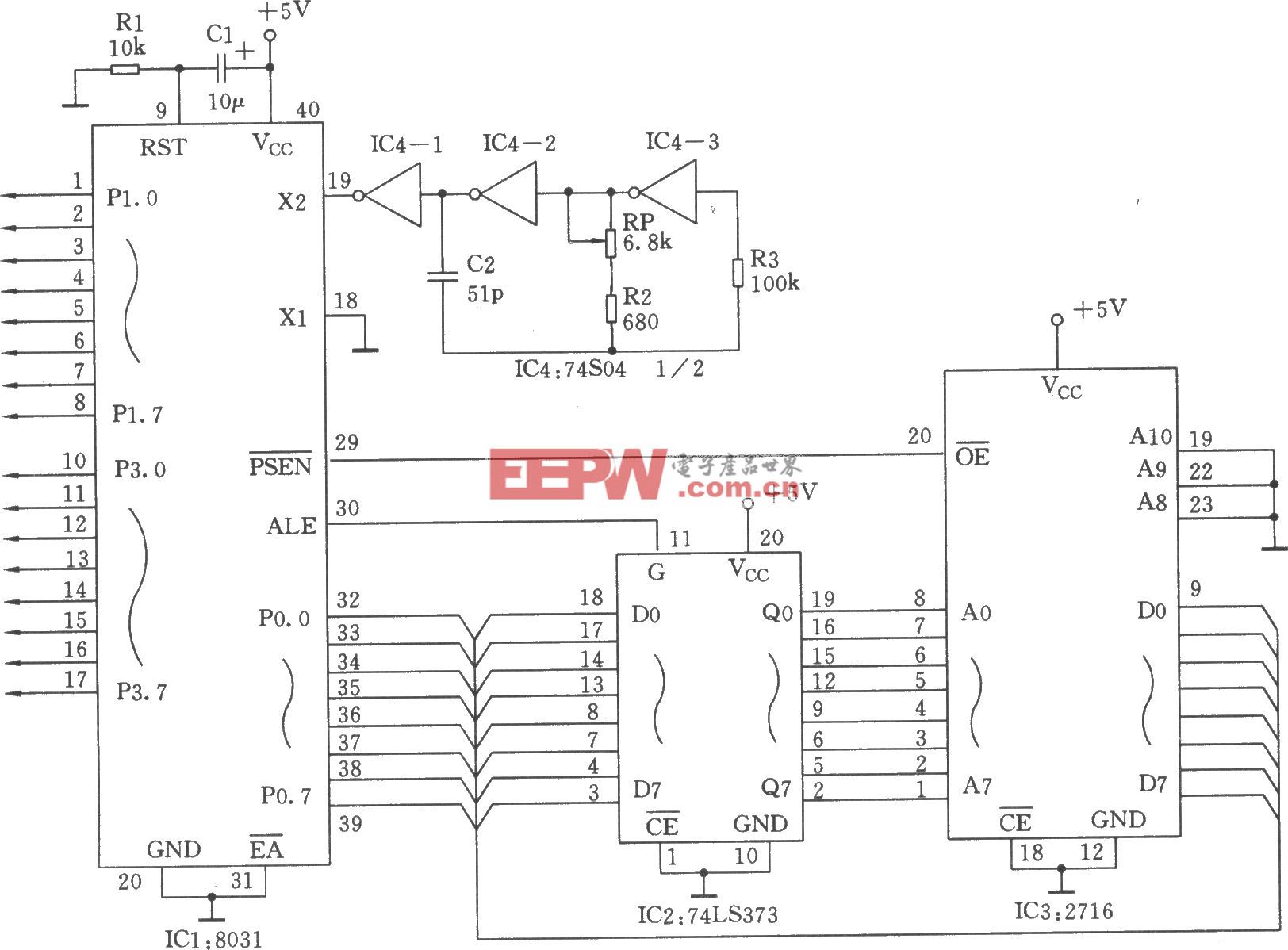

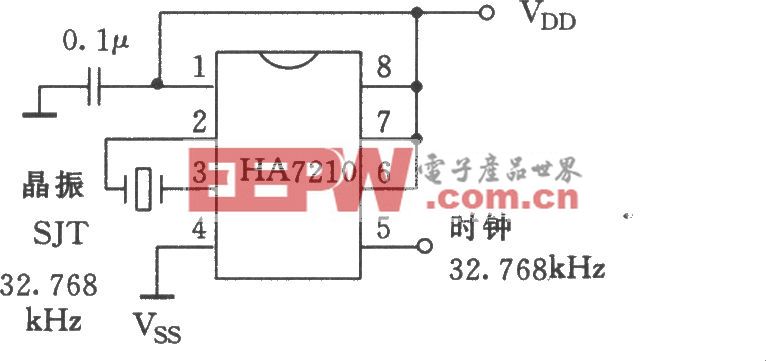

在实际系统中,dsp采用ti公司的tms320f206芯片,eeprom采用microchip公司的24lc256 cmos串行eeprom(图2)。tms320f206属于定点、静态cmos数字信号处理器。它采用先进的哈佛结构,具有片内外设、片内存储器及专用的运算指令集,这些特点使得此器件使用灵活方便。24lc256工作电压为2.5v~5.5v,容量为32k×8bit,为两线串行接口总线,标准与i2ctm兼容。scl为24lc256的时钟输入管脚,sda为其串行地址/数据输入/数据输出管脚。24lc256提供读顺序地址内容的操作方式,其内部的地址指针在每次读操作完成之后加1,此地址指针允许在一次读操作期间,连续顺序地读出整个存储器的内容。其时序如图3所示。

设计中将tms320f206的通用i/o端口io2模拟出scl的时钟,io3负责将数据写入和从24lc256读出(tms320f206与24lc256的接口如图1所示)。脱机工作时,其流程如图4。

3.2 cpld设计

可编程逻辑器件采用xilinx公司的cpld,型号为xc95288xl-6tq144c。该器件为144-pin tqfp封装,内部有288个宏单元,最高工作时钟为151mhz。xc95288xl内部逻辑分为三部分:tms320f206与微机接口的通信、高速地址计数、sram片选读写信号的产生。

3.2.1 tms320f206经过cpld与微机接口的通信

tms320f206与微机接口的通信采用并行接口协议(epp),主要完成从微机加载数据到sram、将数据从sram回读到微机,整个过程对于并行接口来说采用查询方式,对于tms320f206来说采用中断方式。tms320f206使用引脚接收由cpld发出的中断,通过设置tms320f206片内寄存器irm与icr,使tms320f206响应中断而不响应。其时序如图5和6所示。

脱机工作状态下,从并口加载数据时,微机将数据发送到并口,并发出低脉冲,cpld接收stb到后,置busy=1,发出中断信号,tms320f206接收到中断后,控制cpld锁存数据,并将数据写入sram,置busy=0;从并口回读数据时,微机设置并口为输入状态,然后发出autofeedxt低脉冲,cpld接收到后,置=1,发出中断信号给tms320f206,tms320f206控制cpld从sram读取数据并送到并口,置=0。

3.2.2 高速地址计数器设计

信号源中sram在产生雷达波形时工作在100mhz的高速时钟下,这就要求设计的地址计数器也工作在100mhz的时钟下。在同步计数器中,采用超前进位(prescalar)技术来提高其性能,即将前端的、高速计数器的超前输出作为后面的低速计数器的计数使能。实现时我们利用xilinx公司的eda软件中提供的高效宏单元clbmap优化布线,从而使计数器内部延时最小。图7为计数器输出q0~q6的仿真结果。实验表明,上述措施对于提高同步计数器的速度

非常有效。

3.2.3 sram片选读写信号的产生

波形存储单元由两片高速、低功耗,容量为128k×18bit的静态双口sram构成。该器件支持单次读写、流水线读写、触发式读写等多种方式,既可对同一地址单元的高低字节分别读写,也可同时操作。因此片选读写信号时序十分复杂。

本设计中sram片选读写信号直接由tms320f206由数据线送入到cpld,而不必由cpld内部经过复杂的译码逻辑电路产生,由此可见dsp+cpld设计的简单。由于高速读出波形数据送入d/a是在高速时钟(100mhz)下进行,因此高速读出时,片选读信号一直有效。而在写入时,由于会有较长时间不对sram进行操作,为避免因时钟信号线上的毛刺而写入错误数据,因此在写入sram时,片选写信号只在写入的单个时钟周期有效。

4 tms320f206软件设计

信号源有联机和脱机两种工作方式,pcb板上有一个模式选择开关,tms320f206通过i/o端口io1检测工作模式。tms320f206控制程序首先使tms320f206初始化,设置各个片内寄存器。然后根据io1的值决定从eeprom加载还是从微机加载。程序流程略。

5 实验结果

用示波器对信号源所产生结果进行测试,其结果如图8和图9所示,图8为产生的正弦波和锯齿波波形,图9为脱机模式下产生的线性调频信号的基带波形,其时宽为25μs,基带带宽为37.5mhz,经过4倍频后,带宽能达到300mhz。

实验结果表明,运用dsp+cpld来设计信号源的控制部分有很大的优越性,系统灵活可调、性能稳定,复杂的控制用软件实现简单,系统的高速特性也得到满足。

评论