基于IEEE1149.4的测试方法研究

关键词:混合信号,边界扫描,IEEE1149.4,测试方法

1 引 言

边界扫描体系结构及测试访问端口IEEE1149.1标准,对纯数字电路来讲,无疑是十分成功的。它虽主要是为了解决电路板互连测试(Interconnect Testing)而设计的〔1〕,亦可进一步延伸到IC(IntegratedCircuit)级、板级和系统级测试。由于IEEE1149.1被广泛地接受和使用,所以,混合信号测试总线标准IEEE1149.4〔2〕必须与1149.1标准兼容(准确地说,1149.4应当是1149.1的超集)。它们的主要目的是支持互连测试、参数测试和功能测试。

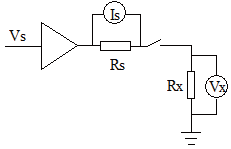

在如图1所示的模拟/混合信号电路板上,IC间的互连可能是简单的连线(IEEE1149.4将其定义为简单互连测试),也有可能是无源元件组成的阻抗网络(IEEE将其定义为扩展互连测试),甚至可能是有源网络(但这种情况极少,一般都将有源元件集成到IC中了)。本文根据混合信号边界扫描测试的工作机制,提出了符合1149.4标准的测试方法,并用本研究室开发的混合信号边界扫描测试系统进行了测试验证。

2 测试方法

边界扫描技术支持多种测试操作,不同操作其测试机理有所不同,下面分别加以讨论。

2.1 简单互联测试

互联测试,可分为简单互连、扩展互连和差分互连等。简单互连测试是指对直接通过导线连接的管脚进行的互联测试,主要用来测试器件连线间的开路、短路和网络间的桥接等故障。进行测试时,先用SAMPLE/PRELOAD指令给输出型的边界扫描单元预置测试激励。执行EXTEST指令之后,捕获该连接线上输入型边界扫描单元的测试响应。然后通过比较激励和响应来判断、定位故障。

对于数字引脚的简单互连测试,首先根据PCB(Printed Circuit Board)网表、器件BSDL(Boundary-Scan Description Language)等相关文档资料选择合适的互连测试算法,如等权值抗误判算法和极小权值-极大相异算法,WALK“0”、WALK“1”等,生成互连测试矢量,用SAMPLE/PRELOAD指令将测试激励施加给输出型的边界扫描单元,然后执行EXTEST指令进行互连测试。这样,互连信号就被捕获到与之相连的另一边界扫描器件的相应的输入型边界扫描单元中。再通过扫描链将边界扫描寄存器的内容移出则可得到测试响应。不过,必须通过一组测试矢量全集的测试,才能保证故障定位的正确。

在模拟引脚的简单互联测试中,为了使模拟管脚的简单互连测试与数字管脚兼容,IEEE1149.4标准 在ABM(Analog Boundary Module)中增添了VH、VL、VTH三种不同的电平,分别代表高电平、低电平和门阙电平。在控制逻辑的控制下,将VH或VL电平施加到输出型的模拟管脚上作为预置测试激励(相当于数字管脚加入高电平或低电平激励)。执行EXTEST指令之后,通过捕获该连接线上的输入型模拟管脚上的电压,并与VTH门阙电平进行比较,将模拟量数字化为一位数字值“0”或“1”,作为输入型模拟管脚上的测试响应,交边界扫描链移出。这样,就可将模拟电路的简单互联测试转化为数字电路的互联测试。通过对预置测试激励和测试响应进行比较,就可以分析出该模拟简单互连线是否发生了短路、断路、桥接等故障,并且可将故障定位到管脚级。

这里有个问题值得注意,即简单互连线发生桥接故障就相当于线与,而线与的结果与电路的具体实现方式有关,这在实例分析中可以看到。

2.2 差分测试

从边界扫描技术角度来看,差分电路可分为数字差分电路和模拟差分电路。差分电路的测试有三种,即数字差分互连电路的测试、模拟差分电路的简单互连测试和模拟差分电路的扩展互连测试等。对于数字差分互联测试,显然,只需将数字差分输入或输出的两个DBM(DigitalBoundary Module)看成两单独的DBM,采用数字管脚简单互连的测试方法即可。

对于模拟差分边界扫描结构,在进行简单互连测试时,标准规定其差分输入端至少须有五种组态:即H-L(High Level-Low Level)、L-H、CD-CD(CoreDisconnect)、CD-G(Ground)和G-CD。所以,在进行差分简单互连测试时,从差分输出端所施加的测试激励不能违反这些规定,除非你确知该测试对象还允许有其它组态。由于差分输出的两ABM具备施加VH或VL电平的能力(只是须注意,当一个脚加VH则另一个脚须加VL,或反之),另一端又可捕获其数字化值,所以可按非差分ABM进行简单的互连测试,只是激励的施加稍有不同。

若模拟差分互连是扩展的差分互连,可以采用完全差分测试或非完全差分测试两种方法。若被测对象只有AT1(Analog Test)和AT2两根模拟测试线且带有差分电路,则只能采用非完全差分测试。首先让差分输入的一端(如“+”端)连接AB1(Internal AnalogBus)、TBIC(Test Bus Interface Circuit)的S5,通过AT1脚输入模拟测试激励,差分输入的另一端(如“-”端)则通过其ABM控制逻辑连其VH、VL或VG来提供模拟测试激励。对差分输出响应的获取,先是让差分输出的一端经AB2、TBIC的S6、AT2输出,再让差分输出的另一端经AB2、TBIC的S6、AT2输出。然后再反过来,让差分输入“+”端接固定电平VH、VL或VG,让差分输入的“-”端通过AB1、TBIC的S5、AT1脚输入原模拟测试激励,同上面一样测量两次。施加两次激励及测量四次响应虽然麻烦一些,但IC器件的边界扫描硬件电路可设计简单些,从而节省器件成本。

进行完全差分测试,就需要被测试对象有专门的差分测试结构,即有一对差分测试激励输入管脚AT1和AT1N,一对差分测试响应捕获管脚AT2和AT2N及相应的TBIC和内部总线结构。测试时,差分模拟测试激励通过AT1和AT1N、TBIC、AB1和AB1N、差分输入功能管脚的两ABM的两SB1加载到差分输入上。其差分输出响应经差分输出功能管脚的两ABM的两SB2、AB2和AB2N、TBIC、AT2和AT2N输出给外部测试响应处理器。

2.3 参数测试

参数测试是指管脚之间不是通过简单的导线连接,而是通过由电阻、电容、电感或由它们组成的网络而连接的一种互联测试,即扩展互连测试,如图1所示。扩展互连测试(即参数测试),由于模拟测试总线和I/O节点间的开关电阻,使得屏蔽测量方法不再适用。

2.3.1 简单网络参数测试

若扩展互连网络是无源的,参数测试就是要测量出该无源网络中R、L、C的元件值。ATE(AutomaticTest Equipment)通过ATAP(Analog Test AccessPort)管脚AT1,经TBIC的开关S5、ABM的SB1,就可将一个已知的模拟测试激励电流IT施加到CUT(Circuit Under Test)上,然后可通过ABM的SB2、TBIC的开关S6、ATAP的管脚AT2,将CUT上的响应电压由ATE测出,记为VT,如图2所示。

若

则VT就可近似等于CUT的端电压。注:Zv为ATE中电压测试系统的阻抗,Zs6为开关S6的阻抗,Zsb2为开关SB2的阻抗,ZD为CUT的阻抗。

若ZD是单个电阻、电感或电容,那么只需已知模拟激励电流信号的频率和幅度就可计算出其元件值。若ZD跨接在两模拟功能管脚之间,它的测量分两步进行。首先,通过对TBIC和ABM的控制,让激励电流信号通过AT1施加到指定F1上,通过AT2脚获取该F1端的电位。再改变对TBIC和ABM的控制,让激励电流信号通过AT1施加到指定ABM上,通过AT2脚获取该F2端的电位。最后,计算出ZD上的电压降,结合已知激励电流信号的频率和幅度值就可计算出其元件值。若ZD是由多个电阻、电感或电容组成的单端口网络,那么只需通过施加一组不同频率的激励电流,然后测试量对应频率ZD上的电压降就可得到一方程组,解此方程组即可求出各元件值。

2.3.2 Delta网络的参数测试

对于Delta互连网络,如图3所示,可以采用下面的方法进行测量。

(1)P4脚接VG,P3和P2脚断开。AT1激励I1施加到P1脚,通过AT2测量P1脚的电位VP11;

(2)P4脚接VG,P3脚断开。AT1激励I1施加到P1脚,通过AT2测量P2脚的电位VP21;

(3)P4脚接VG,P2脚断开。AT1激励I1施加到P1脚,通过AT2测量P3脚的电位VP31;

(4)P4脚接VG,P2脚断开。AT1激励I1施加到P3脚,通过AT2测量P1脚的电位VP12;

(5)P4脚接VG,P1脚断开。AT1激励I1施加到P3脚,通过AT2测量P2脚的电位VP22;

(6)P4脚接VG,P2和P1脚断开。AT1激励I1施加到P3脚,通过AT2测量P3脚的电位VP32。

由这些数据足够解出Z1、Z2、Z3的值〔3〕。当然,若Z1、Z2和Z3又是一无源RLC网络,通过改变I1的频率再重复上面的六步测量,总可以计算出和RLC元件的值,对于同种性质的元件(如同为R或L或C)的串并联,本测试理论只能将其作一个元件来进行测量。

2.3.3 复杂网络

对于较复杂的电路,可以从电路拓扑的角度来考虑其测试。具体来说有两种方法。

(1)通过对ABM开关矩阵的控制,可以将其简化成图2或图3的情形。然后按照相应的测试方法分别进行测量。

(2)单端口网络测量法。

对于任一无源单端口网络(若是多端口网络,可以通过对相关的ABM开关矩阵进行控制,将其转换成单端口网络),由网表文件可以得其拓扑结构、等效支路元件的个数N(等效支路元件的定义:相同性质的两元件串联或并联将被看成一个元件,即等效支路元件),通过在两端口间施加某一频率的电流激励源,再分别测量其两端电压,就可以得到该频率的等效阻抗,从而得一个非线性方程。如在两端口间施加Q(为了尽量减少测试和解非线性方程组所产生误差,一般要求Q>N)个频率不同的电流激励源,就可以得到Q个非线性方程组。解该非线性方程组就可得这N个等效支路元件的元件值。

以上问题的实质是,由电路网表得到传输导纳的非线性模型,经施加不少于Q组(不同频率)的电流激励,分别测量其端电压响应。根据此数据表(即激励响应表)来确定模型中的各参数(即支路导纳值),以保证传输导纳的非线性模型“最佳”拟合这Q组电压电流数据表。由此看来,这实质是一个非线性的模型拟合问题,即非线性最小二乘问题〔4〕。

虽然计算复杂度有所提高,但这种方法可测出复杂无源网络的各分立等效支路元件的参数值,且由于该系统使用计算机,因此处理这些数据是不困难的。虽然当互连网络太大时,这种方法的计算复杂度呈指数增长,但DOT4测试对象是数模混合IC及由其构成的PCB。既然是数模混合IC,留在芯片外的就是用来完成用户特定功能的、或是校准用的、或是难于集成的。难于集成的元件随着集成技术的提高,总可以解决,完成用户特定功能的和校准用的元器件其网络拓扑结构一般比较简单,这种方法完全可以胜任。

这里讨论的参数测试理论方法还可延伸到非线性无源元件的测量。

边界扫描支持的测试还有CLUSTER测试、器件错误装配测试、整个扫描链本身结构的基础测试器件功能测试、BIST(Built-In-SelfTest)测试、INTEST测试等。限于篇幅,此处不再作具体讨论。

3 实例分析

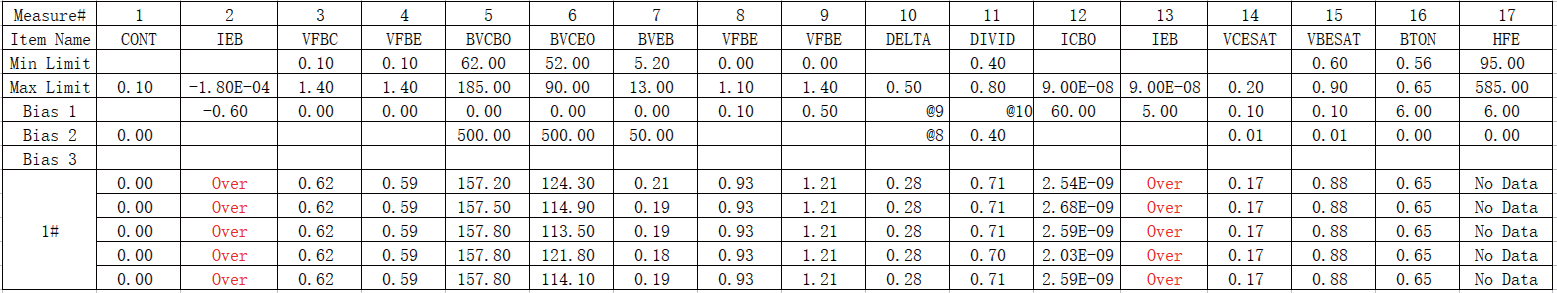

3.1 简单互连测试结果

因目前还没有符合DOT4的器件成品,所以使用了DOT4工作组用于混合信号边界扫描测试的专用实验芯片KLIC〔5〕。KLIC实际上是个Mixed-SignalScan I/O。测试对象DEMO板设计原理是在Mixed-Signal Core电路的基础上插入边界扫描结构即KLIC,使其构成混合信号边界扫描CUT。

DEMO板扫描链中两个边界扫描器件之间直接的互连线有3条,分别从IC1的输出脚DBM、ABM2、ABM3连接到IC2的输入脚DBM、ABM2、ABM3。由KLIC的边界扫描内部结构可知,其在扫描链上的互连测试矢量排列如下(其中,“X”为无关量,“V”对应表1中的测试矢量栏,“R”对应响应数据栏):

XVV XXXXXXXXXXXX XXXX XXX XXXVVXXVVXXXXXXXXXXXXXX

与之相仿,扫描测试结果在扫描链上的表示为:

XXR XXXXXXXXXXXX XXXX XXX XXXXXRXXXRXXXXXXXXXXXXX

这里我们仿照WALK-1、WALK-0的全集测试矢量方法,测试时,通过故障模拟开关进行了故障设置,并且通过响应测试码得到了测试报告和测试分析。把DBM与ABM2桥接,本测试系统的测试结果如表1所示。

3.2 扩展互连测试

对图3所示的Delta网络,用本教研室的混合信号边界扫描测试系统测得的数据如表2所示。其中,Z1为电阻,其真实值为9.734 kΩ,测量平均值为9.5367kΩ,绝对误差为-0.1973 kΩ,相对误差为-2.03%。Z2为电阻,其真实值为4.7 kΩ,测量平均值为4.43 kΩ,绝对误差为-0.27 kΩ,相对误差为5.7%。Z3为电阻,其真实值为6.85 kΩ,测量平均值为6.8888 kΩ,绝对误差为-0.038 kΩ,相对误差为0.56%。这里的较大误差是由于程控信号源和数据采集板做得不完善造成的,只要将两者加以完善,就可以达到IEEE1149.4标准规定的要求。

4 结束语

本文提出了符合1149.4标准的测试方法,并用本研究室开发的混合信号边界扫描测试系统进行了测试验证。测试结果表明,不但能测量互连元器件是否存在,而且还可测量其元件值(电阻、电容、电感),当然还可扩充到非线性元件。

混合信号测试总线是测试数字和模拟信号的起点,但不是解决问题的全部方案。对于小电抗的分立元件,或者高频IC,其测量就较困难。

2 IEEE std 1149.4-1999.IEEE Standard for a Mixed-SignalTest Bus.IEEE Standards Board,New York,19993 K P Parker,JE Mcdermid,S Oresjo.Structure andMetrology for an Analog Testability Bus.Proc.,ITC,1993:309~322

4 谢如彪,姜培庆编著.非线性数值分析.上海:上海交通大学出版社,1984

5 http://grouper.ieee.org/1149/4/kllp.html.KLIC.JTAG Analog Extension Test Chip.

评论