增加简单电路来提高传统PFC控制器性能

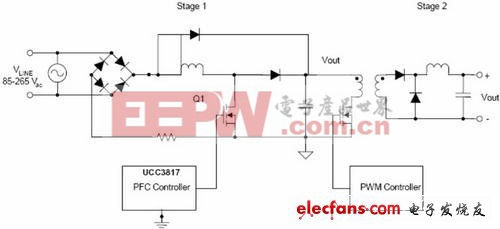

PFC 离线功率转换器系统通常设计为两级级联型。第一级为一个升压转换器,这是因为该拓扑结构拥有连续输入电流(通过使用乘法器可实现电流波形控制)以及可实现近似单位功率因数的平均电流模式控制。但是,升压转换器需要一个比输入电压更高的输出电压,和另外一个将输出电压降压至可用电压等级的转换器(见图 1)。

图1 典型的两级离线功率转换器

升压跟随器的优点

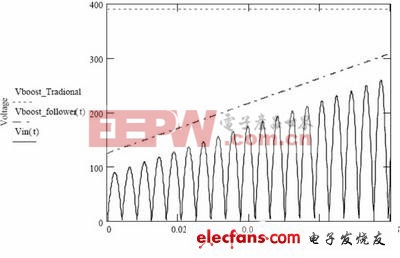

传统的升压转换器的固定输出电压要比线电压的最大峰值高出许多。但是,由于可设计步降转换器应对电压变化,所以并不需要对升压电压进行专门的调节或稳压。只要升压电压高于输入电压峰值,转换器就能正常运行。随着线电压峰值变化而改变升压电压有以下优点(例如升压跟随器预调节器):一是升压电感器的尺寸缩小,二是低压运行时的较低开关损耗。图 2 显示了升压跟随器和传统的 PFC 预调节器的输出电压随着输入电压 (Vin(t)) 变化而变化的情况。

图2 随着输入电压变化,传统升压调节器和升压跟随器输出电压的变化情况

较低的升压电感 (L)

升压电感器的选择是根据允许的最大纹波电流 (△I) 确定的,此时,线电压 (Vin(min)) 和输出电压 (Vout(min)) 均为最低,而占空比 (D) 为最大。下面的方程式用来计算出样机电源升压功率级所需电感。最小输出电压峰值的减小导致最大占空比的减小,从而使升压电感减少。

低压运行时较低的升压开关损耗

在离线 PFC 转换器中,转换器的大部分功耗都来自于进行升压开关转换 (Q1) 时的开关损耗。下面的方程式可以计算出FET开关损耗 (PFE_TR) 和部分 FET 寄生电容损耗 (PCOSS)。在下面的方程式中,IRMS_L表示流过升压电感器的均方根电流,Ton和Toff为FET开关转换次数,变量fs表示功率转换器的转换频率,Coss表示 FET寄生电容。从方程式可以推出,如果输出电压降低,开关损耗也将减少。升压跟随器的PFC转换器在低压运行时,其输出电压要远远低于传统的 PFC 升压转换器的输出电压,同时这也减少了开关损耗。

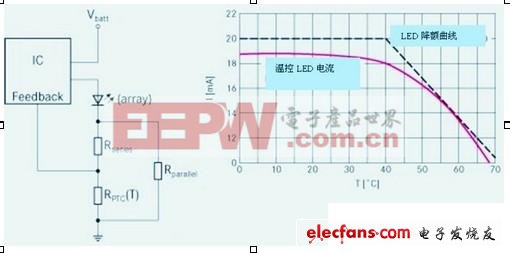

为了进一步的说明,我们建立了使用通用线电压(如 85Vac 至 265Vac)UCC3817 PFC 控制IC的两个功率为 250W 的转换器样机。其中一个转换器设计采用传统的拓扑结构,输出电压为 390V.另一个转换器则是利用升压跟随器技术进行构建的,输出电压可以在 230V 至 387.5V 之间进行变化。低压运行时升压跟随器功率大约高出 2%~3%。请参见图 3 进行功率比较。

图3 传统PFC和升压跟随器PFC在85Vrms时的效率

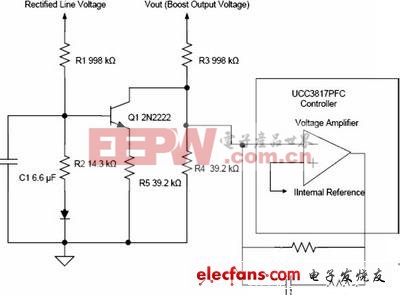

所需额外电路

设计一款带有典型 PFC 控制器的升压跟随器 PFC 功率级并不困难,只需要 5 个额外电子元件即可(见图 4)。

图4 升压跟随器电路只需多增加5个元件

所需的额外电子元件分别为 C1、R1、R2、R4、Q1 和 D1,这些元件可以用于吸收电压环路反馈中电压放大器反相信号的额外电流。当整流线电压增高或降低时,Q1 吸取一个流经 R3 的对应电流,从而导致输出电压随着线压的改变而改变。使用二极管来抵消 Q1基极发射极结温 (Vbe) 的变化。电容 C1 和 R2 形成一个低通滤波器,可以消除由整流线电压引起的纹波电压。

应用实例

本电路是为了使输出电压在 230V 至 390V 之间变化而设计的,大致为一个 2:1 的输入范围。在最终设计中,输出电压随线电压的增长应在设计电压的 8% 以内。除了Q1基极发射极电压 (Vbe) 的电阻器容差和变化以外,二级管的正向电压也是出现误差的原因。在本应用中,升压电压不需要一个严格的容差,因为下游转换器会对 PFC 预调节器输出电压中任何异常的变化进行校正。

设计本电路的第一步是建立分压器,可以由 R3 和 R4 来组成。首先选择 R3,然后使用下列方程式计算出 R4 所需的值。在本设计中,Vref 的值为 7.5V,Vout(最小)的值为 230V。

由 R1 和 R2 组成的分压器,用来使 Q1 的基电压在 1.4V 至 3.9V 之间变化。必须注意的是,不要使晶体管饱和。下列方程式可以用来选取 R2 的值:

在输入电压最小化至 85V 均方根电压时,Vqb1(最小)是 Q1 的基电压。Vd 是电路的正向二级管压降。

电容C1用来过滤出整流线电压纹波。为了限制第三阶谐波电流失真,安装滤波器来将整流线频率减至Q1基点最大电压的1.5%(Vqb1(最大))。

本设计中,最大输入电压为 265V,线频率(f_line)为 60Hz。

评论