时钟抖动时域分析(中)

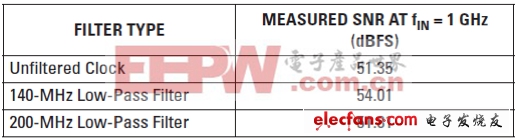

表7 ADS54RF63的测得SNR

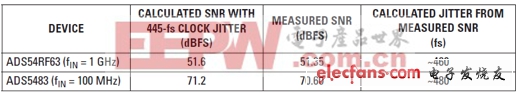

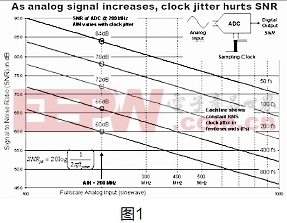

利用调节后的相位噪声曲线图,计算得抖动较好地匹配了SNR测量结果,其在ADS54RF63和ADS5483的10到30fs范围内(参见表8)。考虑到在第三谐波周围可能存在相位噪声的较小时钟抖动影响,该计算得SNR只是一种非常接近的估算结果。

表8 445-fs时钟抖动的SNR结果

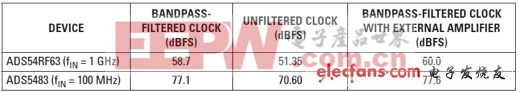

表9 滤波后及未滤波时钟的测得SNR

结论

本文介绍了使用某个滤波或未滤波时钟源时,如何正确地估算数据转换器的SNR。表9概括了得到的结果。尽管时钟输入的带通滤波器对于最小化时钟抖动是必要的,但实验表明它会降低时钟转换速率,并使ADC的孔径抖动降级。因此,最佳的时钟解决方案应包括一个限制相噪影响的带通滤波器,以及一定的时钟振幅放大和转换速率,目的是最小化ADC的孔径抖动。

评论