时钟抖动时域分析(中)

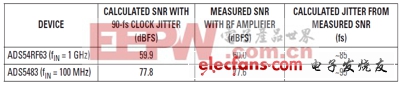

表5 90-fs时钟抖动和RF放大器的SNR结果

未滤波采样时钟试验

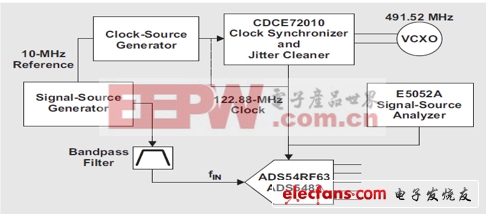

为了强调滤波采样时钟的重要性,在下一个试验中,我们将时钟带通滤波器从CDCE72010输出端去除。在图15所示结构中,我们使用了E5052A相位噪声分析仪来捕获时钟相位噪声。但是不幸的是,该分析仪对相位噪声的测量仅达到40-MHz载波频率偏移,并且在这点以外没有给出任何相位噪声特性的相关信息。

图15 未滤波采样时钟输入的测试装置结构

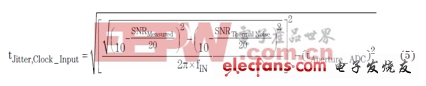

要设定使用未滤波时钟时的正确积分上限,我们必须再一次复习一下采样理论。CDCE72010的未滤波时钟输出看起来像一种具有快速升降沿的方波,而其升降沿由时钟频率的基频正弦波高阶谐波引起。这些谐波的振幅比基频低,且其振幅随谐波阶增加而下降。

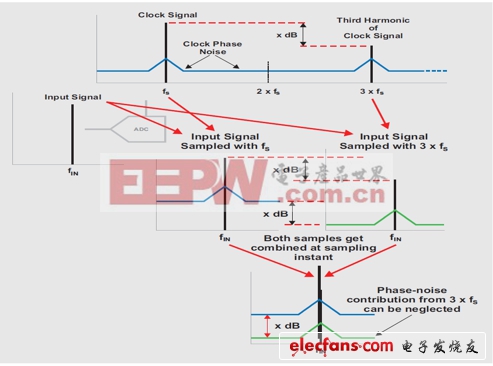

在采样时间,基频正弦波及高阶谐波与输入信号混频,如图16所示。(为了简单起见,仅显示了一个谐波。)因此,三阶谐波周围的相位噪声与输入信号混频,而第三谐波也形成一个混频结果。但是,由于时钟信号的第三谐波的振幅更低,因此该混频结果的振幅也被降低。

图16 采样时间时钟基频及其谐波与输入信号混频

两个采样信号组合在一起时,我们可以看到,一旦振幅差异超出~3 dB时,由第三谐波引起的总相位噪声减弱为最小。由于基频和第三谐波之间的交叉点为2 × fs,将宽带相位噪声积分至2 × fs可以得到相当准确的结果。

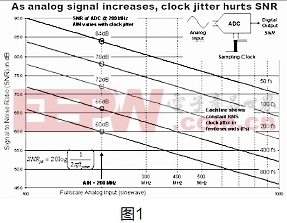

如后面图19所示,CDCE72010的未滤波LVCMOS输出相位噪声在–153 dBc/Hz附近稳定,其始于~10 MHz偏移频率,原因可能是LVCMOS输出缓冲器的热噪声。ADS54RF63 EVM具有~1 GHz(受限于变压器)的时钟输入带宽;因此理论上而言,应该可以对相位噪声求积分为~1GHz(在900-MHz偏移频率的3dB时下降)。这会带来~1.27ps的采样时钟抖动,并将fIN = 1GHz的SNR降至~42.8 dBFS!

评论