时钟抖动时域分析(中)

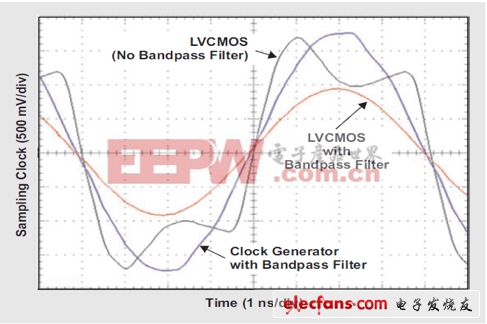

不匹配的原因是,计算得出的孔径抖动是基于时钟源生成器的快速转换速率。CDCE72010的LVCMOS输出消除了时钟信号的高阶谐波,其有助于形成快速升降沿。图13所示波形图表明了带通滤波器急剧降低未滤波LVCMOS输出转换速率,以及将方波转换为正弦波的过程。

图13 时钟抖动对采样时钟转换速率的影响

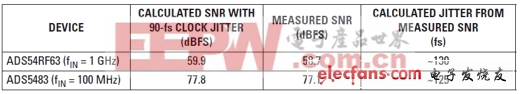

表4 90-fs时钟抖动的SNR结果

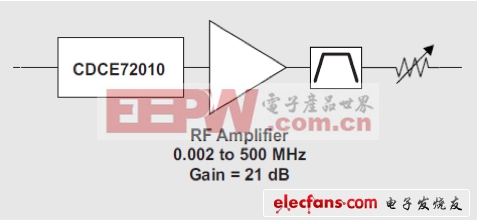

改善转换速率的一种方法是:在CDCE72010的LVCMOS输出和带通滤波器之间添加一个具有相当量增益的低噪声RF放大器,参见图14。该放大器应该放置于滤波器前面,这样便可以将其对时钟信号的噪声影响程度限定在滤波器带宽,而非ADC的时钟输入带宽。由于下一个试验的放大器具有21dB的增益,因此我们在带通滤波器后面增加了一个可变衰减器,旨在匹配滤波后LVCMOS信号到时钟生成器滤波后输出的转换速率。该衰减器可防止ADC的时钟输入超出最大额定值。

图14 带通滤波器前面添加RF放大器来降低转换速率

通过在时钟输入通路中安装低噪声RF放大器,两个数据转换器重复进行了高输入频率的SNR测量,其结果如表5所示。我们可以看到,测得SNR和预计SNR匹配的非常好。使用下面的方程式 5,计算得到的时钟抖动值在90-fs时钟抖动的5fs以内,其结果通过相位噪声测得推导得出。

评论