时钟抖动时域分析(中)

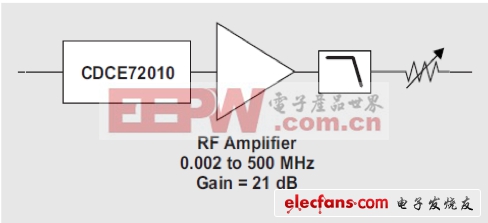

图17 低通滤波器前面添加RF放大器来降低转换速率

图18 不同低通滤波器限制相位噪声

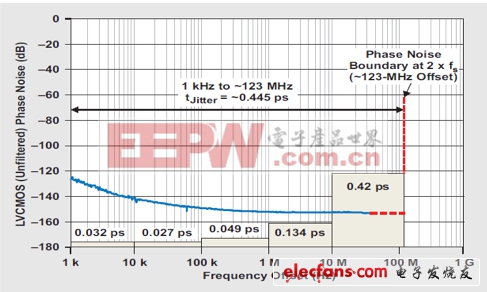

图19 外推 (extrapolate) 123-MHz偏移频率的未滤波相位噪声

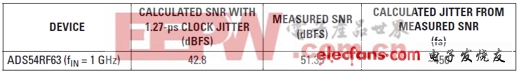

实际SNR测量结果比表6所列要好不少。对比实际测量结果,计算得时钟抖动和SNR之间存在巨大的差异。这表明,LVCMOS输出的相位噪声实际较好地限定在由变压器决定的900-MHz偏移频率界限以内。

表6 1.27-ps时钟抖动的SNR结果

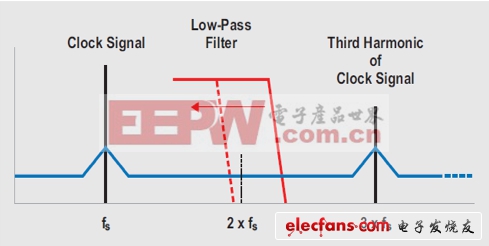

为了证明未滤波时钟信号的相位噪声需要积分至约两倍采样频率,我们实施了如下试验:在CDCE72010输出和ADS54RF63时钟输入之间添加不同的低通滤波器。

需要注意的是,与先前试验中的带通滤波器一样,3X时钟频率以下带宽的低通滤波器降低了时钟信号的转换速率。低通滤波器消除了会产生更快速时钟信号升时间和转换速率的高阶谐波,从而增加了ADC的孔径抖动。正因如此,我们将前面试验的相同低噪声RF放大器添加到时钟通路,并且利用可变衰减器让转换速率匹配信号生成器(参见图17)。

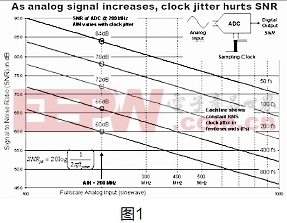

将不同转角频率的低通滤波器用于ADS54RF63的采样时钟(如图18所示),得到了一些如表7所列有趣值。该试验结果表明,LVCMOS输出对时钟抖动的相位噪声影响被限制在约200到250 MHz,其相当于122.88-MHz时钟信号的80-MHz到130-MHz偏移频率,并约为2x采样频率。因此,将宽带相位噪声扩至123-MHz偏移频率,会产生~445 fs的时钟抖动,如图19所示。理想情况下,积分下限应该位于500 Hz处(原因是选择的131000点FFT);但是,500-Hz到1 kMz偏移频率的抖动贡献值极其低,因此为了简单起见其在本测量中被忽略。

评论