TMS320C61416控制FPGA数据加载设计(二)

本系统中2片FPGA加载的原理一样。为避免繁琐,这里以1片FPGA_A为例来作介绍。

CPLD在系统中负责2项工作。

①映射DSP端Flash分页寄存器:控制Flash的高3位地址线,分8页,每页1 MB空间。

②映射DSP端2片FPGA的加载寄存器:

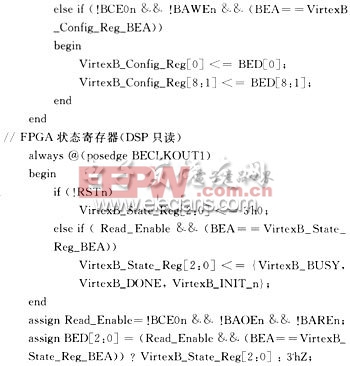

a.配置寄存器FpgaA(B)_config_Reg[8:O]。负责配置数据和时钟,高8位为Byte-Swapped前的数据位,输出到配

置引脚时进行字节交换,最低位为CCLK位。

b.控制寄存器FpgaA(B)_Prog_Reg[2:O]。负责外部控制引脚,分别为CS_B、RDWR_B和PROG_B。

c.状态寄存器FpgaA(B)_State_Reg[2:0]。负责回读配置中的握手信号,分别为BUSY、DONE和INIT_B。

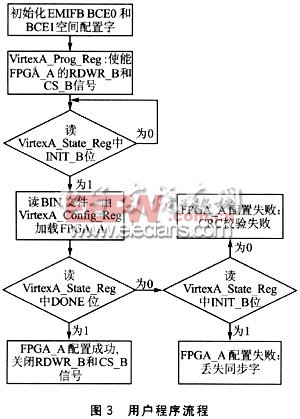

由Bootloader引导的用户程序由C语言开发,在CCS下调试通过。它主要实现Flash翻页,把之前烧写在Flash中的BIN文件,通过上述CPLD中3个加载寄存器对FPGA进行上电配置。具体流程如图3所示。

当前FPGA配置时钟CCLK是在用户程序中通过DSP写命令产生的,即写FpgaA(B)_Config_Reg的CCLK位高低电平;同时8位配置数据也连续写2次,由CPLD锁存到FPGA总线上,便能充分保证图1中该有效数据在CCLK上升沿上被锁。

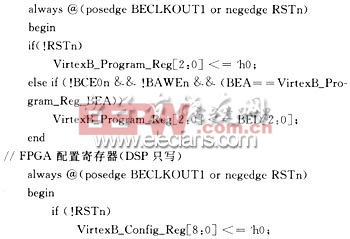

以下是CPLD中动态加载部分的Verilog代码:

//FPGA控制寄存器(DSP只写)

结 语

该系统已成功用于某公司一款软件无线电平台中,通过反复软硬件调试,现已投放市场。此平台不仅可以实现上述提到的上电Flash自行加载FPGA的目的,还可在其配置完以后通过主机端对FPGA实现动态加载,充分满足了软件无线电中可重构化、实时灵活的指导思想。

评论