计算机多设备接口波特率不匹配的研究

引言

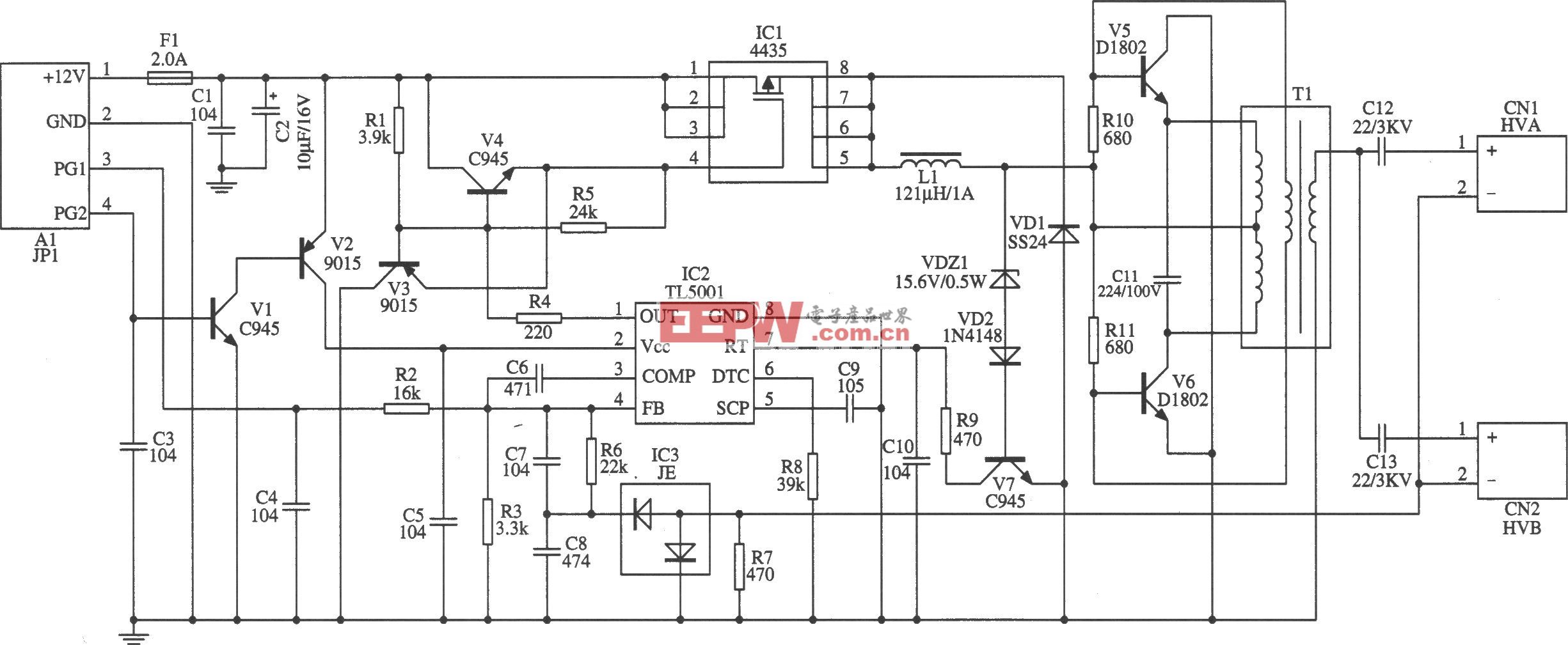

本文引用地址:https://www.eepw.com.cn/article/202529.htm 不同设备接口在传输数据时所要求的频率往往不同,而在一些仅使用一个晶振的系统上,如果一个接口的频率完全匹配,那么其他接口所使用的频率往往就不完全符合要求。例如,为了实现USB总线的48 MHz的传输频率,一般可以用12 MHz的晶振来倍频得到,而12 MHz的晶振在进行串口通信时由于与标准波特率不成倍数关系,因而期望波特率和实际波特率往往不同。

在波特率较低时,这种误差影响不大。例如,期望波特率为57 600 bps时,实际波特率为57 692 bps,传输正常;而当期望波特率高达115 200 bps时,则实际波特率为125 000 bps,误差较大。实验结果表明,此时如不对其进行修正,则无法进行正确传输。

笔者通过实验研究证明,通过使用小数波特率发生器,完全可以像低波特率时一样正确地传输,实现了多位小数的分数逼近法的算法,避免了人工计算过程,彻底实现了波特率计算和修正的自动化。

1 小数波特率发生器工作原理

当外部晶振或者VPB时钟值不是标准波特率的整数倍时,波特率的设定往往会出现偏差。通过小数波特率发生器则可减小或者消除这种偏差。

下面以LPC214x处理器的串口UART1为例阐述小数波特率发生器的工作原理。要使用小数波特率发生器,需要设置小数分频寄存器(U1FDR),该寄存器控制产生波特率的时钟分频器。

预分频器接收VPB时钟,并经过指定的小数要求产生一个输出时钟,小数由该寄存器的值决定。

在不使用小数波特率发生器时,UART1波特率由下式计算:

UART1baudrate = PCLK/(16×(256×U1DLM+U1DLL))

当使用小数波特率发生器时,则由下式计算:

UART1baudrate = [PCLK/(16 ×(256 × U1DLM + U1DLL))] ×(MulVal / (MulVal + DivAddVal)

其中PCLK为VPB总线时钟,U1DLM和U1DLL为标准的UART1波特率除数寄存器。可以看出,MulVal / (MulVal + DivAddVal)就是用来修正波特率的小数值,被称作校准系数。它由两个参数构成:DivAddVal(波特率生成欲分频除数值)和MulVal(波特率预分频乘数值)。DivAddVal和MulVal都必须为整数,且满足:

1 ≤ MulVal≤ 15,0 ≤ DivAddVal ≤ 15。

根据以上公式很容易计算串口波特率,但是实际应用中,更多的是在使用非标准晶振时确定波特率校准系数,即设定U1FDR寄存器DivAddVal和MulVal的值。确定波特率校准系数可以分如下3步进行:

① 确定除数锁存器的值: 根据需要的波特率bps,按照没有校准系数的波特率计算公式确定除数锁存器的值(DLM,DLL)。由于采用非标准晶振,得到的结果通常为小数。无论小数值大小,均舍弃小数部分的值,对结果进行取整操作(不是四舍五入),得到除数锁存器的值。

② 确定校准前的波特率: 将①得到的除数值(DLM,DLL)代入不带校准系数的串口波特率计算公式,得到未经过校准的波特率BPS。

③ 确定校准系数p: p=bps/BPS=MulVal/(MulVal+DivAddVal)

根据限制条件1≤MulVal≤15和0≤DivAddVal≤15,寻找合适的值,使得到误差尽可能小的校准系数。

2 多位小数的分数逼近算法

(1) 传统获取MulVal和DivAddVal整数值的方法

假设系统晶振为12 MHz,拟设定波特率bps为115 200 bps,根据前面所述校准系数的确定过程,12 000 000/(16×115 200)=6.51,取6为除数值,那么BPS=12 000 000/[16×(256×0+6)]=125 000 bps,所以p=bps/BPS=0.921 6。

传统获取MulVal和DivAddVal整数值的方法大多依靠经验技巧或者反复试验。如参考文献2《深入浅出ARM7LPC214x下》中,第77页描述的那样:

评论