IBIS建模——第2部分:为何以及如何创建您自己的IBIS模型

本文引用地址:https://www.eepw.com.cn/article/202204/433293.htm

简介

在构建任何系统时,仿真都发挥着关键作用。它帮助设计人员预见问题,进而避免费时且成本高昂的修改。我们的目标始终是一次就成功!在仿真高速数字接口时,如果设计不当,简单的PCB走线可能会影响信号质量。在信号完整性仿真中,IBIS(输入/输出缓冲器信息规范)模型用来表示器件的数字接口。

如IBIS系列文章的第1部分所述,IBIS是一个行为模型,通过以表格形式列出的电流与电压(I-V)和电压与时间(V-T)数据来描述器件的数字接口的电气特征。IBIS模型应尽量准确,且不含任何解析错误,避免在之后使用时出现问题。此外,对于具有数字接口的每个部件或器件,都应该提供可用的IBIS模型。这样客户需要时,可直接从制造商的网页上下载。但是,事实并非总是如此。对于IBIS模型用户,他们常遇到的一个问题就是模型的可用性。当他们在设计中选用的部件没有IBIS模型时,其产品开发可能受阻。

IBIS模型最好是由其制造商提供;但是,用户也可以创建IBIS模型。本文介绍如何使用LTspice,基于SPICE模型创建最基础的IBIS模型。下文使用IBIS建模手册(IBIS 4.0版)中的规格来介绍LTspice仿真设置。还要介绍如何使用定性和定量品质因数来验证IBIS模型。

何谓“最基本的”IBIS模型?

为了帮助客户使用LTspice创建基本的IBIS模型,需要先定义“基本”一词。基本的IBIS模型不仅取决于I/O模型关键字,还取决于需要建模的数字缓冲器的类型。这意味着需要重新审视IBIS的早期版本,以定义建立缓冲器模型需要满足的最低要求,以及当时建模的数字接口的类型。事实证明,单端CMOS缓冲器是可以使用IBIS建模的最简单的数字IO之一,本文将予以介绍。

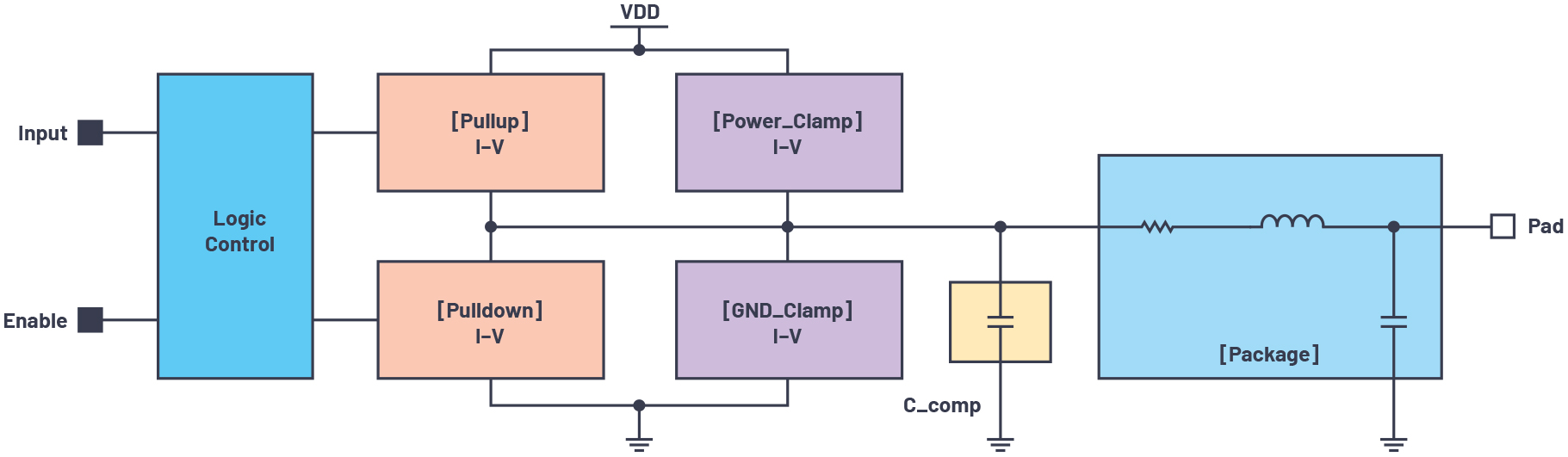

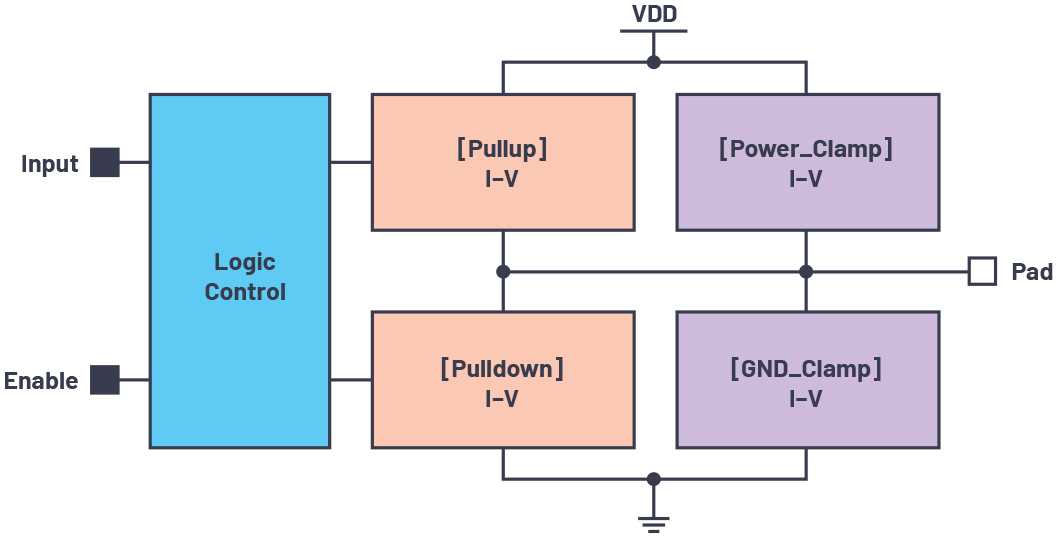

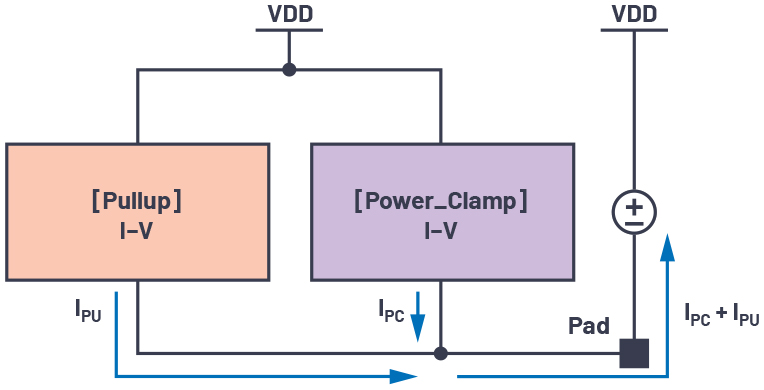

图1 3态CMOS缓冲器的IBIS模型

表1 基于Model_type的IBIS模型组件汇总

Model_type | [封装] | C_comp | [GND_ Clamp] | [Power_ Clamp] | [下拉] | [上拉] | V-T表 | [斜坡] |

输入 | ✓ | ✓ | ✓ | ✓ | — | — | — | — |

3态 | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |

I/O | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |

图1显示3态CMOS缓冲器IBIS模型的结构。如第1部分所述,IBIS模型中的组件或关键字取决于模型类型。表1汇总列出基本的IBIS模型的组件,具体由Model_type决定。

应用案例

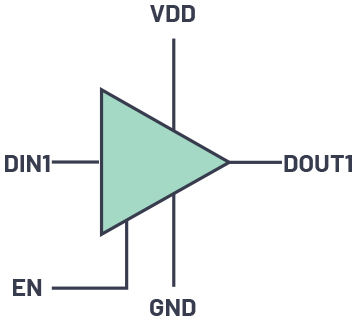

在本文中,我们将使用一个假设的ADxxxx器件的LTspice模型来创建IBIS模型。它是一个带有使能引脚的单输入和单输出数字缓冲器。因此,得到的IBIS模型将具有两个输入(DIN1和EN)、一个三态输出(DOUT1)。

一般来说,生成IBIS模型有五个基本步骤:

■ 建立预建模程序。

■ 对从SPICE模型中提取的C_comp、V-I和V-T数据进行LTspice仿真。

■ 格式化IBIS文件。

■ 使用IBIS解析器测试检查文件。

■ 比较IBIS模型与SPICE模型在相同加载条件下的仿真结果。

IBIS模型提供典型数据、最小数据和最大数据。它们通过工作电源电压范围、温度和工艺来确定[HA1]。为简洁起见,本文只讨论典型条件。

Ibischk Golden Parser系列可用于检查IBIS模型是否符合IBIS规范。ibischk可执行文件可从IBIS.ORG网页免费获取。本文使用集成ibischk的第三方IBIS模型编辑软件。

预建模程序

在开始仿真之前,用户应该下载器件的数据手册,并安装SPICE模型和LTspice文件。通过确定部件具备的数字接口数量和类型(例如,输入、开漏、三态等),对部件进行初始评估。

根据器件数据手册,确定工作电源电压、工作温度、集成电路(IC)封装类型、器件引脚排列、数字输出时序规格的加载条件(RLoad和/或CLoad),以及数字输入的低电平输入电压(VINL)和高电平输入电压(VINH)。ADxxx SPICE模型如图1所示,其指标参数列在表2。

通过使用关键字,将有关器件数字接口的所有信息汇集到一个IBIS文件中。关键字是IBIS模型中用括号括起来的标识符,如第1部分所述。更多详细信息请参阅此部分内容。

图2 Adxxxx 3态数字缓冲器SPICE模型

表2 ADxxxx数据手册参数

数据手册参数 | 值 |

VDD | 1.8 V(典型值) |

工作温度 | 25°C |

VINL | 0.3 × VDD |

VINH | 0.7 × VDD |

IC封装 | 6引脚SOT-23 |

CLoad | 15 pF |

与IC封装模型相关的关键字是[Package]。它包含RLC(电阻-电感-电容)寄生参数,代表从芯片焊盘到IC焊盘/引脚的连接。此信息可从制造商处获得。也可以查找另一个IBIS文件的[Package]数据,只要该器件采用的封装与正在评估的器件完全相同,并且来自同一制造商。6引脚SOT-23封装的器件封装寄生参数如表3所示。

表3 6引脚SOT-23封装寄生参数

[封装] | |||

变量 | 典型值 | 最小值 | 最大值 |

R_pkg | 1.595E-01 | NA | NA |

L_pkg | 4.455E-09 | NA | NA |

C_pkg | 0.370E-12 | NA | NA |

器件引脚排列如表4所示。关键字[Pin]用于描述引脚及其对应的模型名称。[Pin]一般为3列格式。第一列是引脚编号,第二列是引脚描述,第三列是模型名称。有些封装包含[HA2]类似的引脚(VCC、GND)。这些引脚可以按模型分组和描述。在这种情况下,由于SPICE模型没有给出有关内部晶体管级原理图的信息,因此最好为每个数字接口创建单独的模型。在IBIS文件中,模型名称“Power”和“GND”用于命名电源和接地引脚。非数字接口和“请勿连接”引脚则描述为“NC”或无连接。请注意,模型名称是区分大小写的。由于在稍后的建模程序中还会用到,所以需给出具体的模型名称。

表4 ADxxxx引脚列表

[Pin] | Signal_name | Model_name |

1 | VDD | Power |

2 | DIN1 | cmos_di1 |

3 | EN | cmos_en |

4 | DOUT1 | cmos_out1 |

5 | GND | GND |

6 | NC | NC |

ADxxxx真值表如表5所示。这在建立LTspice仿真时非常有用。还必须要知道如何将DOUT1引脚设置为高阻抗(高阻)模式、逻辑1和逻辑0。

表5 ADxxxx真值表

EN | DIN1 | DOUT1 |

0 | 0 | 高阻 |

0 | 1 | 高阻 |

1 | 0 | 0 |

1 | 1 | 1 |

LTspice设置和仿真

一般来说,IBIS模型通过前面提到的I-V(电流与电压)和V-T(电压与时间)数据描述数字缓冲器的行为。进行IBIS建模时,每种类型的数字接口都拥有[HA3]一组自己的I-V和/或V-T数据,如表1所示。表6更加详细地列出了这些数据集。注意查看每个数据集的注释。那些标记为“推荐”的数据,表示这些数据缺失不会在ibischk解析器测试中导致误差。但是,这些数据集对通道仿真有一定的作用。例如,钳位数据有助于分析信号反射。

表6 输入和3态接口的I-V和V-T数据集

IBIS关键字 | 输入 | 3态 | ||

V-I数据 | C_comp | 必需 | 必需 | |

[Power_Clamp] | 推荐 | 推荐 | ||

[GND_Clamp] | 推荐 | 推荐 | ||

[上拉] | — | 必需 | ||

[下拉] | — | 必需 | ||

V-T数据 | [上升波形] | 加载至VDD | — | 推荐 |

加载至GND | — | 推荐 | ||

[下降波形] | 加载至VDD | — | 推荐 | |

加载至GND | — | 推荐 | ||

[斜坡] | — | 必需 | ||

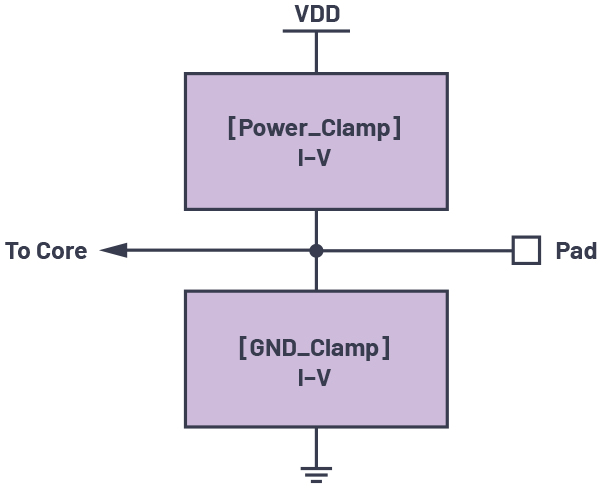

[Power_Clamp]和[GND_Clamp]

图3 [Power_Clamp]和[GND_Clamp]关键字结构的概念图

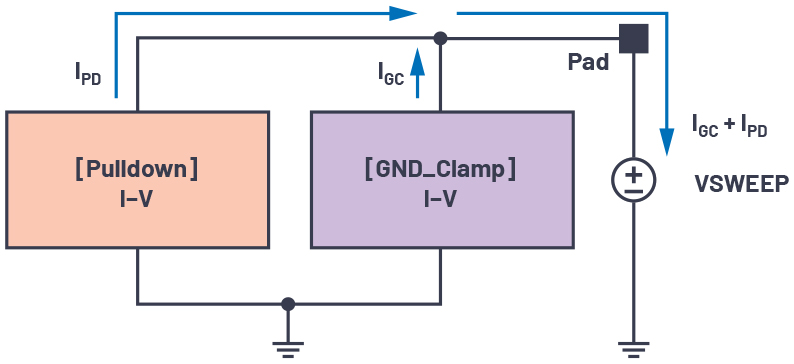

[GND_Clamp]和[Power_Clamp]通过以表格形式列出的I-V数据显示数字缓冲器的静电放电(ESD)器件的行为。[Power_Clamp]表示以VDD为基准的ESD器件的整体行为,接地箝位表示以GND为基准的ESD器件的整体行为。

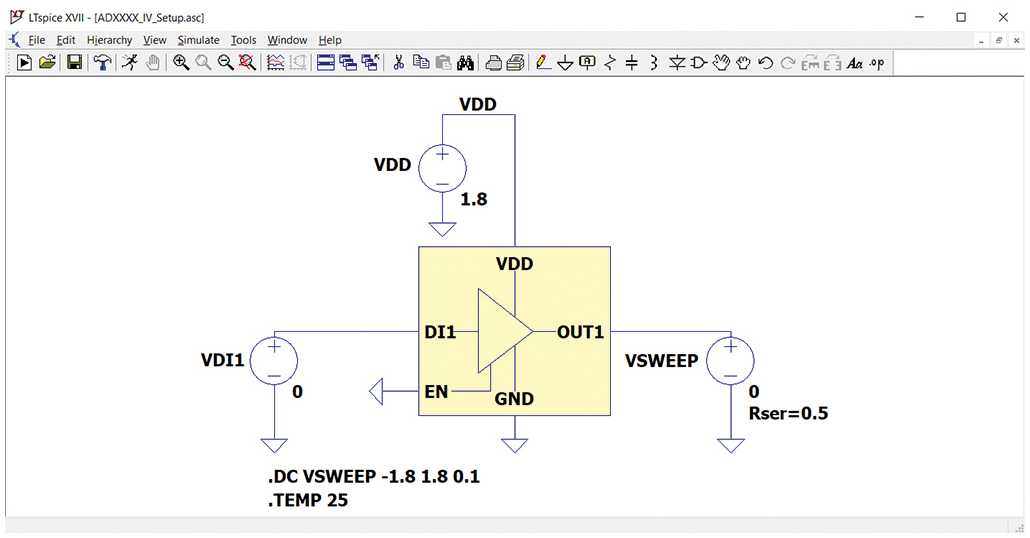

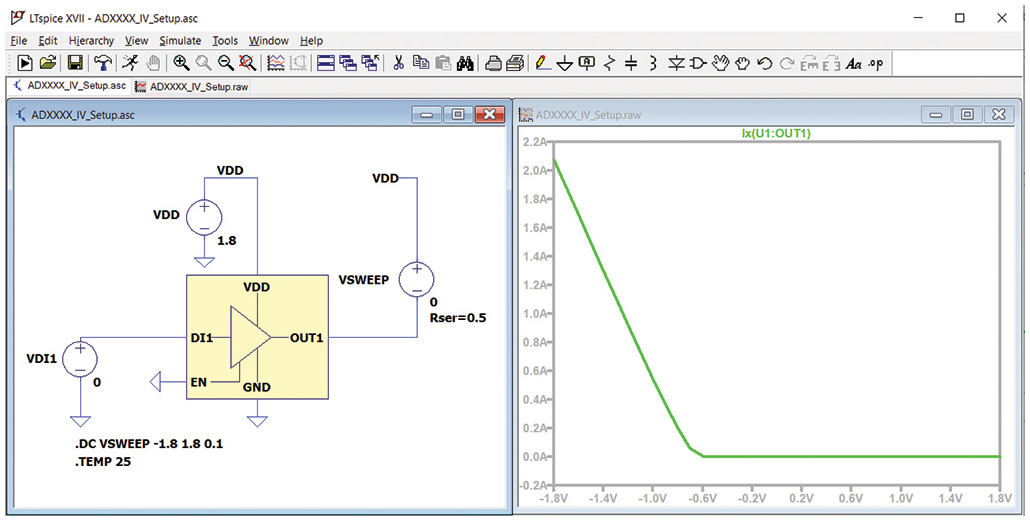

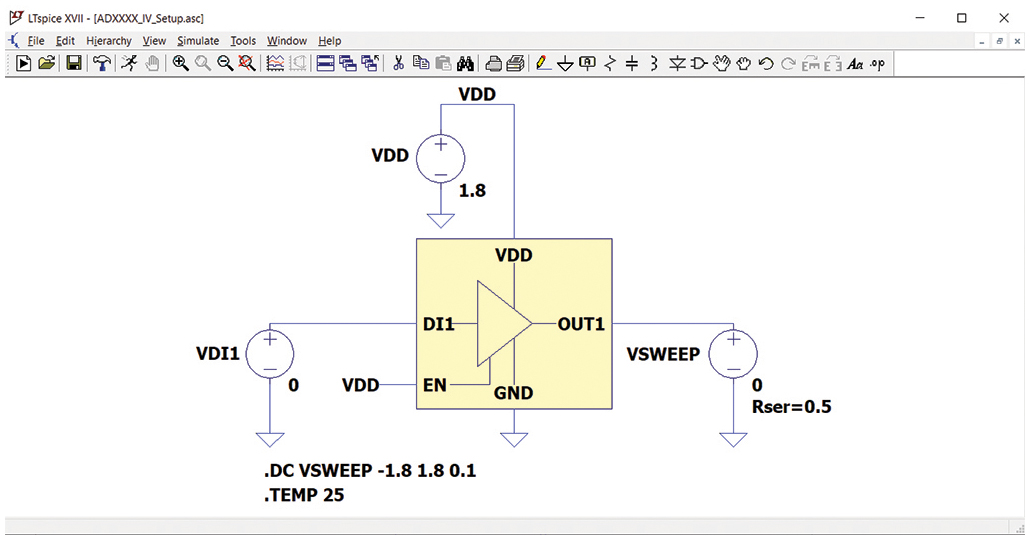

在LTspice中,I-V数据可以使用.DC SPICE命令/指令进行测量。DOUT1的接地箝位用图4所示设置进行测量。在该设置中,使用适当的电源电压将该器件配置为高阻态模式(请参见表5)。这可以确保将ESD器件与核心电路隔离。VSWEEP是以GND为基准的扫描电压。使VSWEEP基准电压接地,确保只显示GND箝位ESD器件的特征。

根据IBIS规格,应扫描电压轨以外(最好从-VDD到2 × VDD)的I-V数据,本例中是从–1.8 V到+3.6 V。通过直接执行此操作,扫描VDD以外的电压将会开启电源箝位ESD器件。为了避免这种情况,首先在–1.8 V至+1.8 V范围内扫描VSWEEP,并使用外推方法添加3.6 V数据点。此方法适用于所有I-V数据集。

另外,请注意所有I-V数据集最多只接受100个数据点。如果数据点超过这个数目,在ibischk解析器测试中会提示错误。设置.DC命令的增量,使得到的数据点数量小于或等于99。这是为了容纳用于2 × VDD外推的一个额外数据点。

进行直流扫描时,仿真中可能出现非常大的反向电流。要解决这个问题,将起始扫描从近似二极管势垒电位(-0.7 V)设置为VDD (+1.8 V)。然后将数据外推至符合–VDD至2 × VDD I-V数据。另一种方法是将一个小电阻Rser与VSWEEP串联,以限制极端电流。

图4 ADxxxx DOUT1接地箝位设置

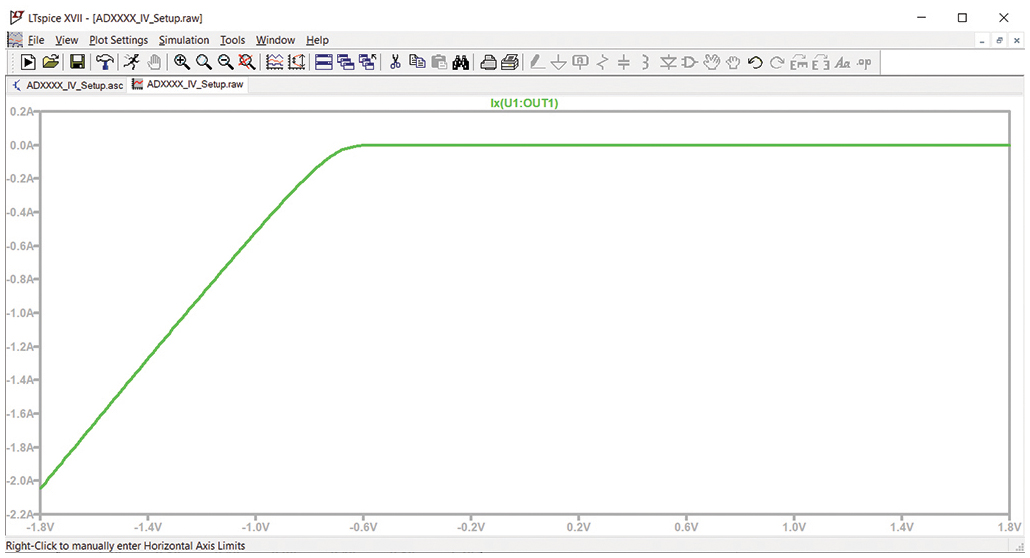

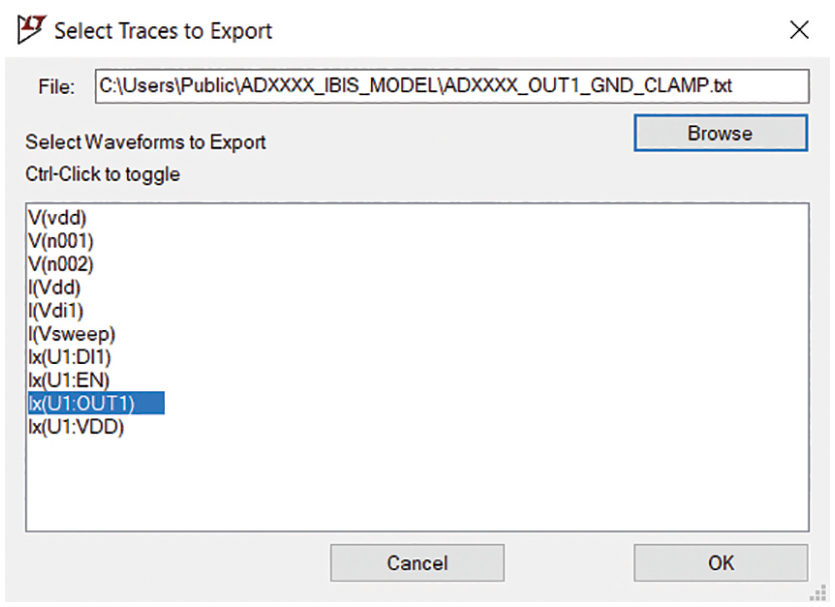

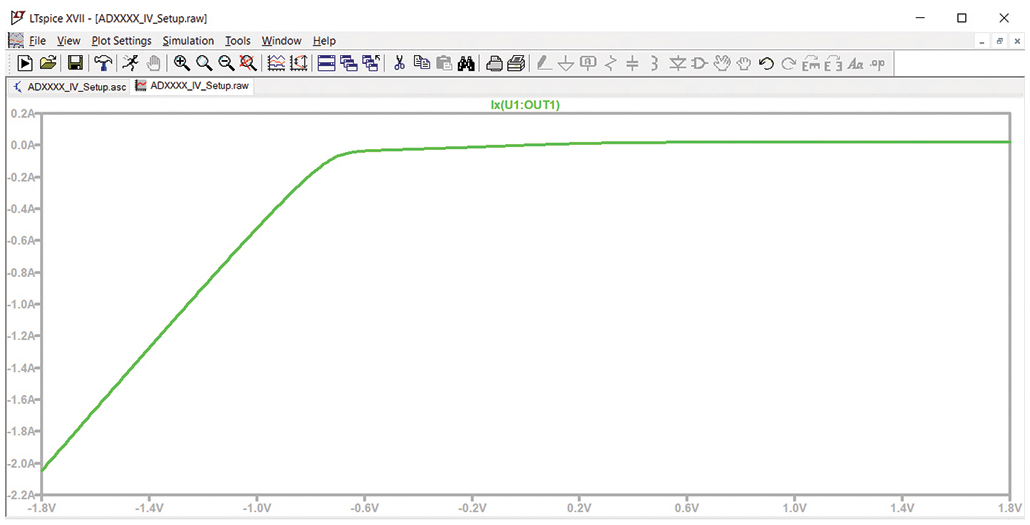

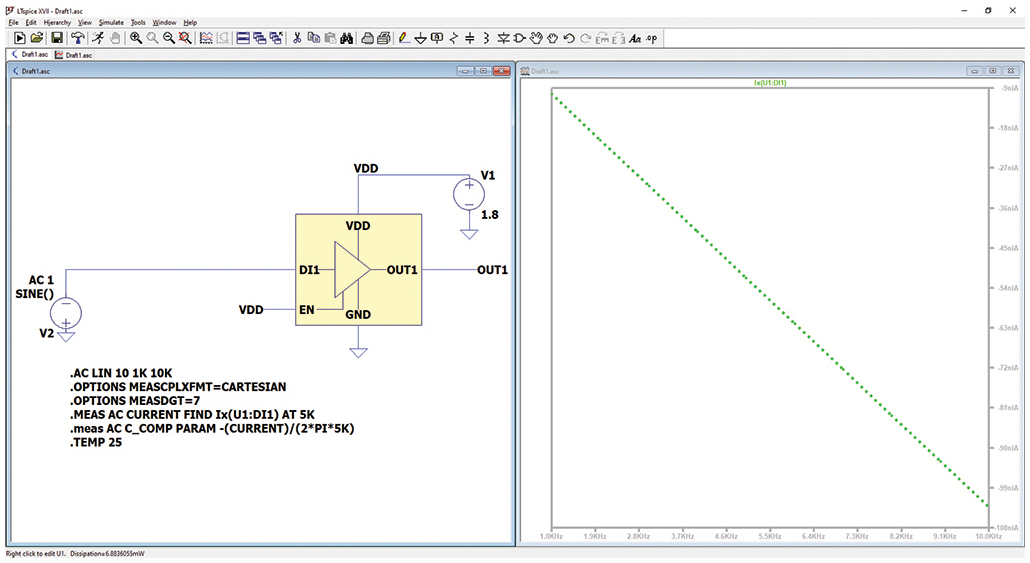

单击运行按钮,LTspice开始运行仿真。由于正在评估DOUT1,所以目标节点为Ix(U1:DOUT1)。虽然从技术角度来看I(VSWEEP)也是正确的,但IBIS模型需要Ix(U1:DOUT1)上的电流极性。这是为了最大限度减少I(VSWEEP)数据的进一步格式化,使其适合模型。结果应该如图5所示。仿真完成后,先单击结果窗口保存数据,然后单击文件 -> 将数据导出为文本。导航至要保存的目录,单击受测节点,然后单击OK(如图6所示)。

图5 接地箝位仿真结果

图6 将仿真数据导出为文本

[Power_Clamp]数据提取与接地箝位设置类似,因此扫描电压VSWEEP以VDD为基准。设置和结果如图7所示。

图7 ADxxxx OUT1电源箝位设置和结果

[下拉]和[上拉]

图8 I-V关键字结构的概念图

图8显示了I-V关键字结构的概念图。[下拉]和[上拉]表示缓冲器中上拉和下拉元素的行为。如果以图表形式表示,它们看起来就像MOSFET的I-V特征曲线。在提取[下拉]和[上拉]数据时,了解如何通过器件的真值表操控从输出引脚输出的信号非常重要。提取[下拉]和[上拉]数据的设置与[GND_Clamp]和[Power_Clamp]类似,即DOUT1引脚使能,且不处于高阻模式。

要提取[下拉]数据,DOUT1引脚应设置为逻辑0输出或0 V。所以,必须设置适当的电源电压,如图9所示。对EN引脚施加1.8 V的等效逻辑高压,以使能DOUT1引脚,对DIN1引脚施加逻辑0或0 V,将DOUT1引脚设置为逻辑0输出。可以通过真值表(表5)进行确认。结果如图10所示。

图9 ADxxxx OUT1下拉设置

图10 ADxxxx OUT1下拉图

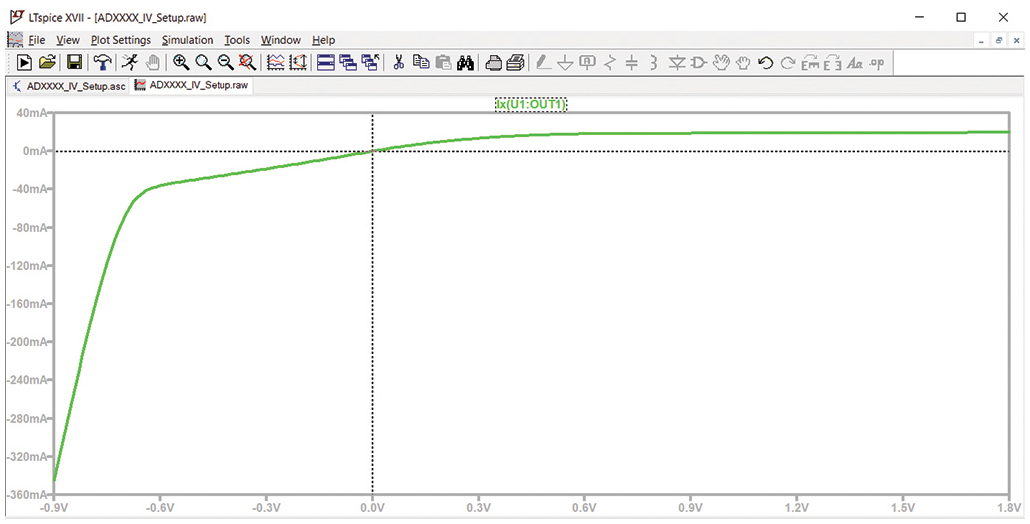

放大[下拉]数据,它类似于MOSFET的I-V特征曲线,如图11所示。

图11 ADxxxx DOUT1下拉图(缩放视图)

在保存下拉数据时,请注意它构成了[GND_Clamp]和[下拉]的总电流。图12可以更好地说明这一点。要移除[GND_Clamp]组件,只需从[下拉]保存数据中逐点减去它。为了简化这一操作,[GND_Clamp]和[下拉]直流分析的电压增量、开始电压和结束电压必须相同。

图12 来自下拉保存数据的实际电流

获取上拉数据的设置如图13所示。提供适当的电源电压,以将DOUT1设置为逻辑1 (1.8 V)。这将确保上拉元件激活/开启。然后,VSWEEP也在–1.8 V至+1.8 V范围内扫描,并且以VDD为基准。以这种方式连接VSWEEP,可以防止用户格式化数据以符合IBIS规范。

图13 ADxxxx DOUT1上拉设置和结果

与[下拉]一样,保存的[上拉]数据是从[Power_ Clamp]和[上拉]总电流得出的结果。因此,用户需要从保存的[上拉]数据中逐点减去数据,以去除[Power_Clamp]组件,如果它们的直流扫描参数相同,这很容易完成。提醒大家,对所有的I-V数据测量使用相同的直流扫描参数。

图14 来自保存的[上拉]数据的实际电流

[C_comp]

[C_comp]关键字代表缓冲器的电容,其最小、典型和最大拐角的值各不相同。它是晶体管和裸片的电容,与封装电容不同。可以采用两种方式提取[C_comp]。当引脚由交流电压供电时,可以使用方程1中的公式来得出近似值,也可以使用方程2中的公式进行计算。

![]()

其中:

■ ImIac:被测电流的虚值

■ F:交流电源的频率

■ VAC:交流电源的幅度

使用LTspice进行C_Comp提取

如图15所示,可以通过提供交流电压和频率扫描来提取缓冲器电容。由于提供的是交流电压,所以要测量电流的实部和虚部部分。当用交流电压供电时,必须反转电流的极性,以测量缓冲器的输入电流值。测量输出缓冲器电容时,对于图15所示的图,唯一要做的更改就是必须将交流电源连接至输出引脚。

图15 ADxxxx C_comp提取设置

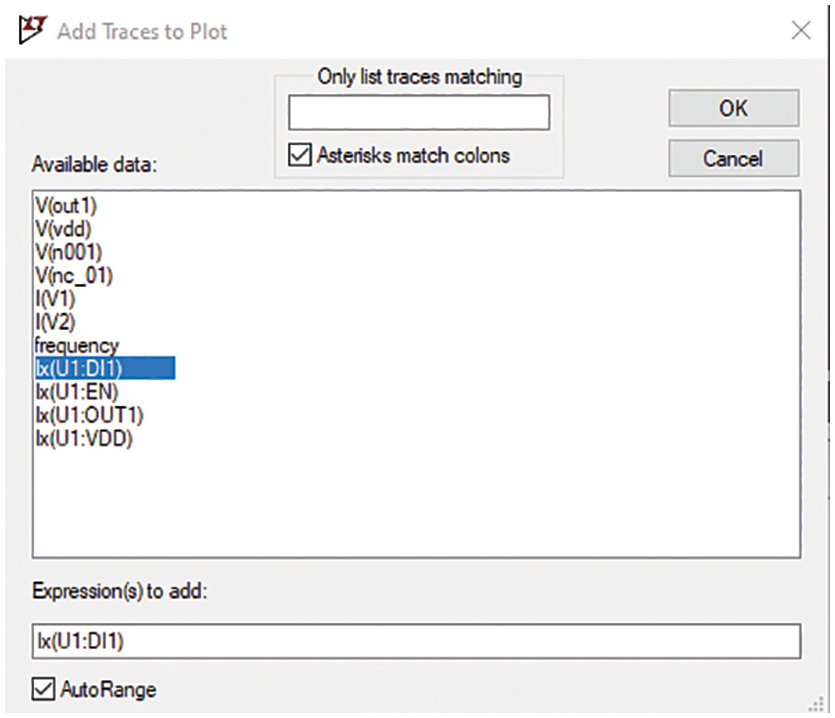

交流电压的幅值可以是任意值,但通常设置为1 V。它将按照SPICE指令进行频率扫描。使用.AC命令绘制波形时,默认设置为以波特模式显示,单位为dB。必须将其设置为笛卡尔模式才能查看电流值,这样可以直接使用缓冲器电容公式进行处理。要查看缓冲器电容波形,用户必须先右键单击波形窗口,然后单击添加走线,再选择被测量的引脚。波形图窗口将显示两条线。

实线表示被测电流的实部,虚线表示被测电流的虚部。

图16 向图中添加走线对话框

若要将图形设置从波特改为笛卡尔,右键单击波形窗口左侧的y轴,以打开左纵轴—幅度对话框。然后将图示方式从波特改为笛卡尔。

图17 将图设置从波特改成笛卡尔

评论