TD2SCDMA终端综合测试仪物理层的软硬件设计

1 引 言

本文引用地址:https://www.eepw.com.cn/article/201809/388529.htm最近,TD-SCDMA 综合测试仪引起国内研究机构和国外测试仪表业巨头很大兴趣。文献[1]指出了TD2SC2DMA 综合测试仪是产业链的薄弱环节,文献[1-2]提出了采用综测仪构建一致性测试系统的方案。Agilent、R S 等计划推出相应产品或正在进行研发。

综合测试仪总体结构都由物理层、高层协议栈、主控,测量算法4 部分组成。TD-SCDMA 与WCD2MA、CDMA2000 、GSM 综合测试仪的主要区别是物理层,其他部分可以借鉴已有测试系统。文献[3 ]给出了WCDMA/ GSM 手机测试系统主控的软件设计。

TD-SCDMA 系统与WCDMA 系统高层协议栈基本相同。测量算法也可以借鉴W DM 综合测试仪的相应算法。所以实现物理层是实现TD-SCDMA 综合测试仪的关键,需要重新研究设计。

综合测试仪物理层具有系统仿真功能和射频数据采集双重任务。一般基站的物理层功能与系统仿真功能类似。虽然目前已经有大量文献讨论WCDMA 基站实现各个方面的问题,如文献[4]比较了各种硬件平台方案,文献[5] 分析了各个算法的快速实现方法。但是,由于综合测试仪物理层具有双重任务,所以需要研究设计新的物理层实现方案来满足要求。

本文在第2 部分简要介绍了物理层与综合测试仪其他部分的接口,第3、4 部分分别描述了物理层硬件平台实现方案,DSP 和F PGA 程序设计方案。第5部分总结了物理层实验结果。

2 物理层接口

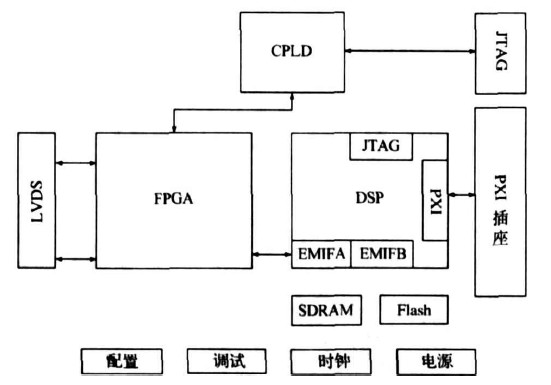

综合测试仪采用XI 总线架构,逻辑功能如图1示。

图1 综合测试仪逻辑功能图

综合测试仪物理层通过LVDS ( 低电压差分信号) 接收来自Ae roFlex3030 的12 倍速IQ 信号,经过处理,把结果分2 路通过PXI 传给测量算法以及协议栈。测量算法接收到物理层采集的12 倍速数据,得出ACL R、OBW、EVM 等测量数值。高层协议栈接收物理层解调的TD-SCDMA 信号,进一步进行L2 、L3 等高层协议处理。同时,物理层接收高层协议栈的数据,使用3 GPP 协议规定的算法进行处理之后,以1 倍速信号通过L VDS 传输到AeroFlex3020 ,最后通过功分器发射给待测终端。

3 物理层硬件平台

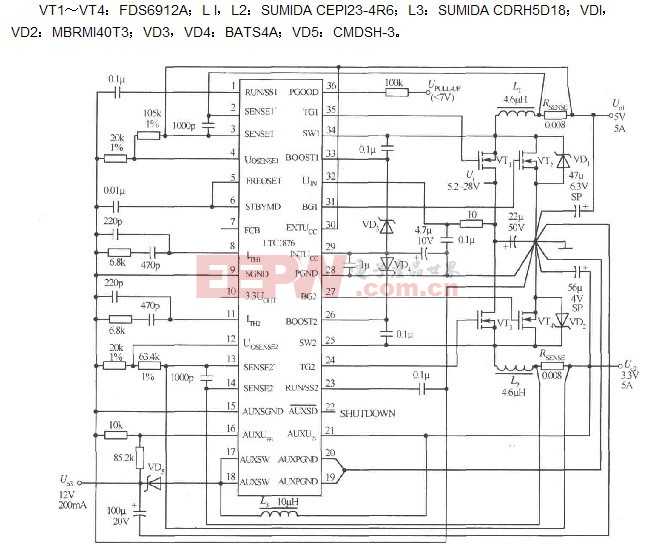

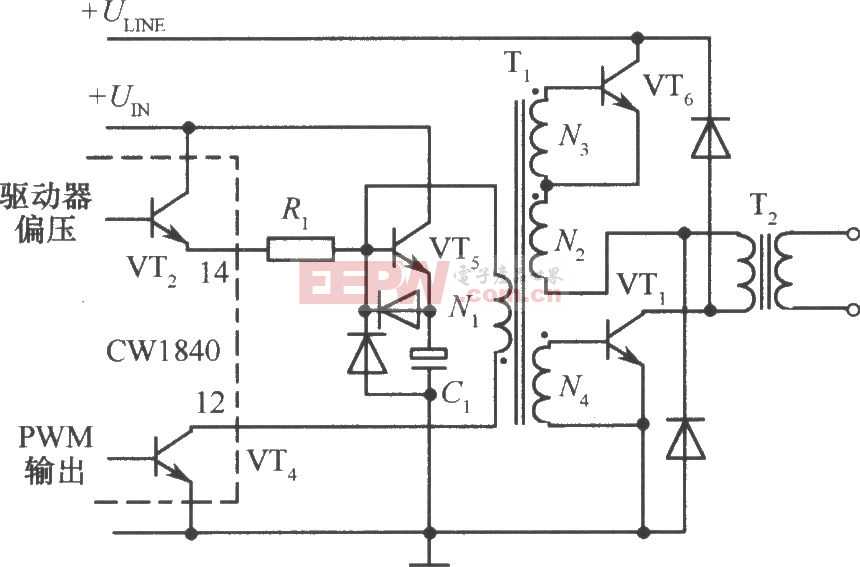

物理层采用通用DSP 加FPGA 架构, 如图2所示。

图2 物理层硬件架构图

硬件选用高性能的DSP 处理芯片---德州仪器面向通信应用的TMSC320C6416 处理器,其参数如下:主频1 GHz ,二级缓存1 MB ,配备维特比协处理器(VCP) ,Turbo 码译码协处理器( TCP) .F PGA 选用最新的Xilinx Vertex 芯片。

FP GA 与DSP 通过EMIFA 口以SBSRAM 方式连接,EMIF 时钟采用100 MHz[ 6 ],以确保高速数据交换。本设计没有采用单独的PXI 接口芯片,而采用TMSC320C6416 内置的PXI 接口模块。采用这种XI 硬件连接,同时使用优化后W 编写的驱动程序,完全可以满足射频12倍速信号采集的要求,而实现更加简单。

4 DSP 和FPGA 程序设计

4.1 FPGA 程序设计

F PGA 采用ISE 开发环境,使用VHDL 语言描述FPGA 硬件电路。综合测试仪物理层与一般基站物理层不同,要实现更加复杂的流程, 所以把尽量多的任务在DSP 完成。F PGA 内部只接收DSP 输出的单倍速的数字信号,根据3 GPP 协议,实现根升余弦滤波,采用内插方法,把单倍速的数字信号变为24 倍速信号, 通过L VDS 模块发送给AeroFlex 3020。同时,接收Are2oFlex3030 的24 倍速,数据分成2 路,一路4 倍速信号经过根升余弦用于解调TD-SCDMA 信号,另外一路12 倍速信号用于测量。

4.2 DSP 程序设计

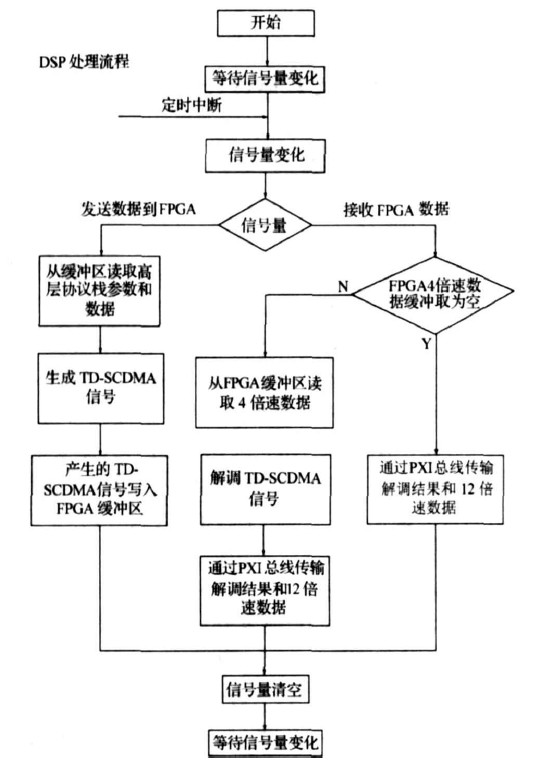

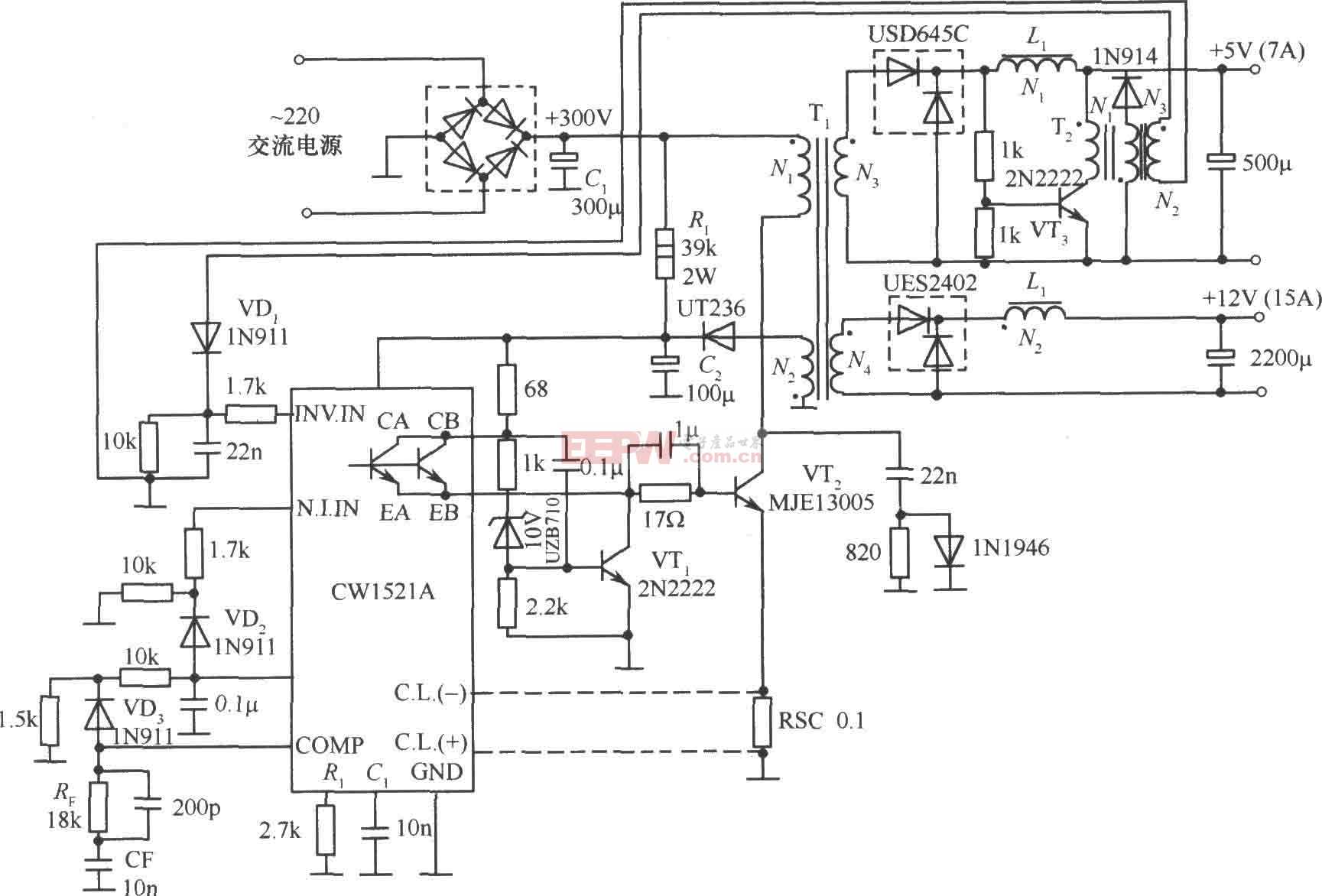

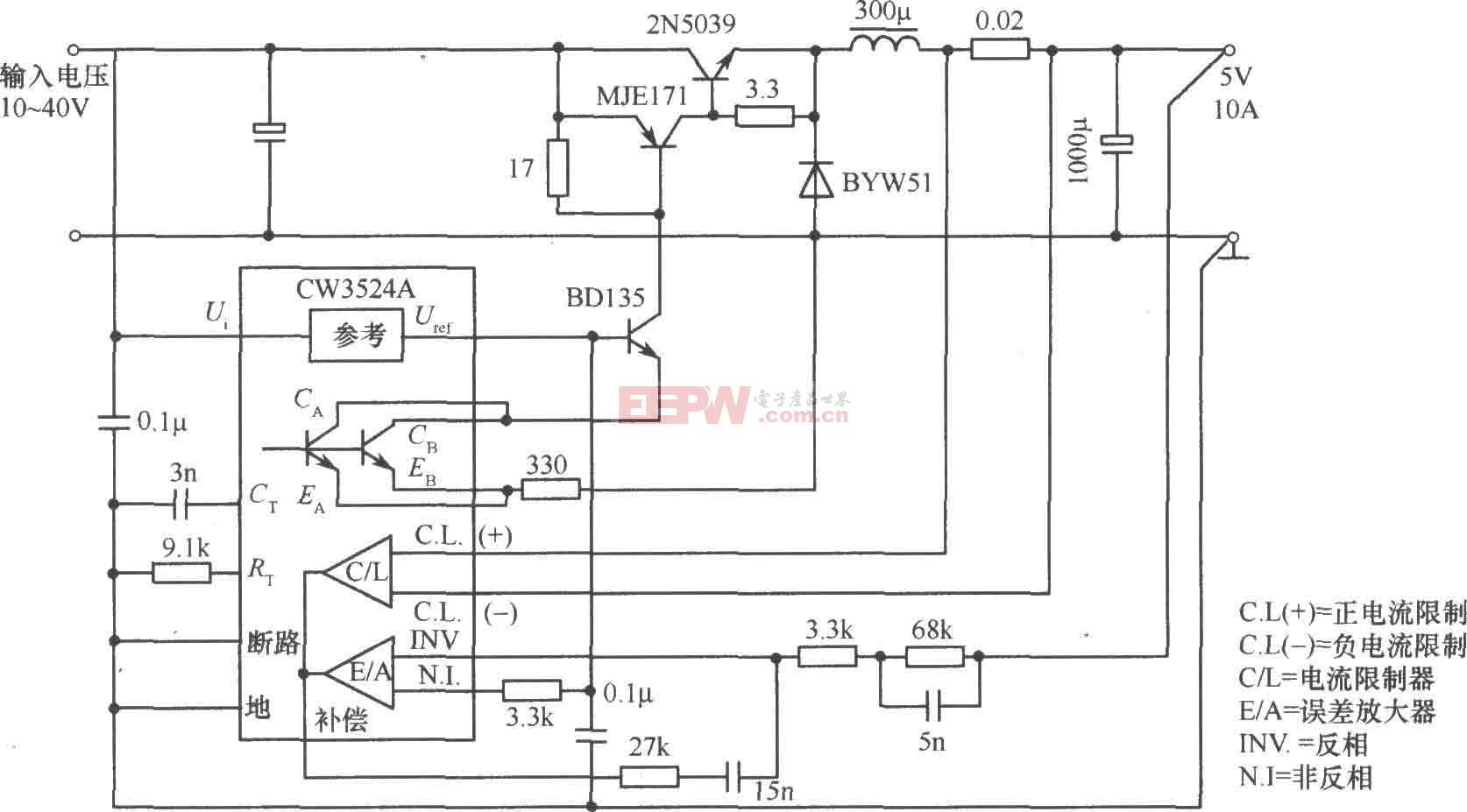

DSP 主要功能是根据3 GP P 协议接收高层传输的信息,产生TD-SCDMA 信号,传输给FPGA 以及接收FPGA 4 倍速数字信号,之后解调TD-SCDMA 信号,把解调后的信号传给高层。同时传送12 倍速信号给射频测量。DSP 流程图如图3 所示。

图3 DSP 流程图

评论